Chapter 2 Exercises with Solutions

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

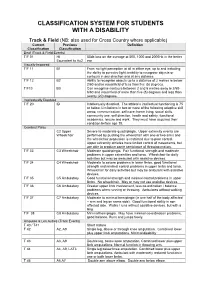

Disability Classification System

CLASSIFICATION SYSTEM FOR STUDENTS WITH A DISABILITY Track & Field (NB: also used for Cross Country where applicable) Current Previous Definition Classification Classification Deaf (Track & Field Events) T/F 01 HI 55db loss on the average at 500, 1000 and 2000Hz in the better Equivalent to Au2 ear Visually Impaired T/F 11 B1 From no light perception at all in either eye, up to and including the ability to perceive light; inability to recognise objects or contours in any direction and at any distance. T/F 12 B2 Ability to recognise objects up to a distance of 2 metres ie below 2/60 and/or visual field of less than five (5) degrees. T/F13 B3 Can recognise contours between 2 and 6 metres away ie 2/60- 6/60 and visual field of more than five (5) degrees and less than twenty (20) degrees. Intellectually Disabled T/F 20 ID Intellectually disabled. The athlete’s intellectual functioning is 75 or below. Limitations in two or more of the following adaptive skill areas; communication, self-care; home living, social skills, community use, self direction, health and safety, functional academics, leisure and work. They must have acquired their condition before age 18. Cerebral Palsy C2 Upper Severe to moderate quadriplegia. Upper extremity events are Wheelchair performed by pushing the wheelchair with one or two arms and the wheelchair propulsion is restricted due to poor control. Upper extremity athletes have limited control of movements, but are able to produce some semblance of throwing motion. T/F 33 C3 Wheelchair Moderate quadriplegia. Fair functional strength and moderate problems in upper extremities and torso. -

Ifds Functional Classification System & Procedures

IFDS FUNCTIONAL CLASSIFICATION SYSTEM & PROCEDURES MANUAL 2009 - 2012 Effective – 1 January 2009 Originally Published – March 2009 IFDS, C/o ISAF UK Ltd, Ariadne House, Town Quay, Southampton, Hampshire, SO14 2AQ, GREAT BRITAIN Tel. +44 2380 635111 Fax. +44 2380 635789 Email: [email protected] Web: www.sailing.org/disabled 1 Contents Page Introduction 5 Part A – Functional Classification System Rules for Sailors A1 General Overview and Sailor Evaluation 6 A1.1 Purpose 6 A1.2 Sailing Functions 6 A1.3 Ranking of Functional Limitations 6 A1.4 Eligibility for Competition 6 A1.5 Minimum Disability 7 A2 IFDS Class and Status 8 A2.1 Class 8 A2.2 Class Status 8 A2.3 Master List 10 A3 Classification Procedure 10 A3.0 Classification Administration Fee 10 A3.1 Personal Assistive Devices 10 A3.2 Medical Documentation 11 A3.3 Sailors’ Responsibility for Classification Evaluation 11 A3.4 Sailor Presentation for Classification Evaluation 12 A3.5 Method of Assessment 12 A3.6 Deciding the Class 14 A4 Failure to attend/Non Co-operation/Misrepresentation 16 A4.1 Sailor Failure to Attend Evaluation 16 A4.2 Non Co-operation during Evaluation 16 A4.3 International Misrepresentation of Skills and/or Abilities 17 A4.4 Consequences for Sailor Support Personnel 18 A4.5 Consequences for Teams 18 A5 Specific Rules for Boat Classes 18 A5.1 Paralympic Boat Classes 18 A5.2 Non-Paralympic Boat Classes 19 Part B – Protest and Appeals B1 Protest 20 B1.1 General Principles 20 B1.2 Class Status and Protest Opportunities 21 B1.3 Parties who may submit a Classification Protest -

VMAA-Performance-Sta

Revised June 18, 2019 U.S. Department of Veterans Affairs (VA) Veteran Monthly Assistance Allowance for Disabled Veterans Training in Paralympic and Olympic Sports Program (VMAA) In partnership with the United States Olympic Committee and other Olympic and Paralympic entities within the United States, VA supports eligible service and non-service-connected military Veterans in their efforts to represent the USA at the Paralympic Games, Olympic Games and other international sport competitions. The VA Office of National Veterans Sports Programs & Special Events provides a monthly assistance allowance for disabled Veterans training in Paralympic sports, as well as certain disabled Veterans selected for or competing with the national Olympic Team, as authorized by 38 U.S.C. 322(d) and Section 703 of the Veterans’ Benefits Improvement Act of 2008. Through the program, VA will pay a monthly allowance to a Veteran with either a service-connected or non-service-connected disability if the Veteran meets the minimum military standards or higher (i.e. Emerging Athlete or National Team) in his or her respective Paralympic sport at a recognized competition. In addition to making the VMAA standard, an athlete must also be nationally or internationally classified by his or her respective Paralympic sport federation as eligible for Paralympic competition. VA will also pay a monthly allowance to a Veteran with a service-connected disability rated 30 percent or greater by VA who is selected for a national Olympic Team for any month in which the Veteran is competing in any event sanctioned by the National Governing Bodies of the Olympic Sport in the United State, in accordance with P.L. -

U.S. Department of Veterans Affairs (VA)

U.S. Department of Veterans Affairs (VA) Veteran Monthly Assistance Allowance for Disabled Veterans Training in Paralympic and Olympic Sports Program (VMAA) In partnership with the United States Olympic Committee and other Olympic and Paralympic entities within the United States, VA supports eligible service and non-service-connected military Veterans in their efforts to represent Team USA at the Paralympic Games, Olympic Games and other international sport competitions. The VA Office of National Veterans Sports Programs & Special Events provides a monthly assistance allowance for disabled Veterans training in Paralympic sports, as well as certain disabled Veterans selected for or competing with the national Olympic Team, as authorized by 38 U.S.C. 322(d) and Section 703 of the Veterans’ Benefits Improvement Act of 2008. Through the program, VA will pay a monthly allowance to a Veteran with either a service-connected or non-service-connected disability if the Veteran meets the minimum military standards or higher (i.e. Emerging Athlete or National Team) in his or her respective Paralympic sport at a recognized competition. In addition to making the VMAA standard, an athlete must also be nationally or internationally classified by his or her respective Paralympic sport federation as eligible for Paralympic competition. VA will also pay a monthly allowance to a Veteran with a service-connected disability rated 30 percent or greater by VA who is selected for a national Olympic Team for any month in which the Veteran is competing in any event sanctioned by the National Governing Bodies of the Olympic Sport in the United State, in accordance with P.L. -

The Use of Fire Classification in the Nordic Countries – Proposals

The use of fi re classifi cation in the Nordic countries – Proposals for harmonisation Per Thureson, Björn Sundström, Esko Mikkola, Dan Bluhme, Anne Steen Hansen and Björn Karlsson SP Technical Research Institute of Sweden SP Technical SP Fire Technology SP REPORT 2008:29 The use of fire classification in the Nordic countries - Proposals for harmonisation Per Thureson, Björn Sundström, Esko Mikkola, Dan Bluhme, Anne Steen Hansen and Björn Karlsson 2 Key words: harmonisation, fire classification, construction products, building regulations, reaction to fire, fire resistance SP Sveriges Tekniska SP Technical Research Institute of Forskningsinstitut Sweden SP Rapport 2008:29 SP Report 2008:29 ISBN 978-91-85829-46-0 ISSN 0284-5172 Borås 2008 Postal address: Box 857, SE-501 15 BORÅS, Sweden Telephone: +46 33 16 50 00 Telefax: +46 33 13 55 02 E-mail: [email protected] 3 Contents Contents 3 Preface 5 Summary 6 1 Nordic harmonisation of building regulations – earlier work 9 1.1 NKB 9 2 Building regulations in the Nordic countries 10 2.1 Levels of regulatory tools 10 2.2 Performance-based design and Fire Safety Engineering (FSE) 12 2.2.1 Fire safety and performance-based building codes 12 2.2.2 Verification 13 2.2.3 Fundamental principles of deterministic Fire Safety Engineering 15 2.3 The Construction Products Directive – CPD 16 3 Implementation of the CPD in the Nordic countries – present situation and proposals 18 3.1 Materials 18 3.2 Internal surfaces 22 3.3 External surfaces 24 3.4 Facades 26 3.5 Floorings 28 3.6 Insulation products 30 3.7 Linear -

United States Olympic Committee and U.S. Department of Veterans Affairs

SELECTION STANDARDS United States Olympic Committee and U.S. Department of Veterans Affairs Veteran Monthly Assistance Allowance Program The U.S. Olympic Committee supports Paralympic-eligible military veterans in their efforts to represent the USA at the Paralympic Games and other international sport competitions. Veterans who demonstrate exceptional sport skills and the commitment necessary to pursue elite-level competition are given guidance on securing the training, support, and coaching needed to qualify for Team USA and achieve their Paralympic dreams. Through a partnership between the United States Department of Veterans Affairs and the USOC, the VA National Veterans Sports Programs & Special Events Office provides a monthly assistance allowance for disabled Veterans of the Armed Forces training in a Paralympic sport, as authorized by 38 U.S.C. § 322(d) and section 703 of the Veterans’ Benefits Improvement Act of 2008. Through the program the VA will pay a monthly allowance to a Veteran with a service-connected or non-service-connected disability if the Veteran meets the minimum VA Monthly Assistance Allowance (VMAA) Standard in his/her respective sport and sport class at a recognized competition. Athletes must have established training and competition plans and are responsible for turning in monthly and/or quarterly forms and reports in order to continue receiving the monthly assistance allowance. Additionally, an athlete must be U.S. citizen OR permanent resident to be eligible. Lastly, in order to be eligible for the VMAA athletes must undergo either national or international classification evaluation (and be found Paralympic sport eligible) within six months of being placed on the allowance pay list. -

Nebraska Highway 12 Niobrara East & West

WWelcomeelcome Nebraska Highway 12 Niobrara East & West Draft Environmental Impact Statement and Section 404 Permit Application Public Open House and Public Hearing PPurposeurpose & NNeedeed What is the purpose of the N-12 project? - Provide a reliable roadway - Safely accommodate current and future traffi c levels - Maintain regional traffi c connectivity Why is the N-12 project needed? - Driven by fl ooding - Unreliable roadway, safety concerns, and interruption in regional traffi c connectivity Photo at top: N-12 with no paved shoulder and narrow lane widths Photo at bottom: Maintenance occurring on N-12 PProjectroject RRolesoles Tribal*/Public NDOR (Applicant) Agencies & County Corps » Provide additional or » Respond to the Corps’ » Provide technical input » Comply with Clean new information requests for information and consultation Water Act » Provide new reasonable » Develop and submit » Make the Section 7(a) » Comply with National alternatives a Section 404 permit decision (National Park Service) Environmental Policy Act application » Question accuracy and » Approvals and reviews » Conduct tribal adequacy of information » Planning, design, and that adhere to federal, consultation construction of Applied- state, or local laws and » Coordinate with NDOR, for Project requirements agencies, and public » Implementation of » Make a decision mitigation on NDOR’s permit application * Conducted through government-to-government consultation. AApplied-forpplied-for PProjectroject (Alternative A7 - Base of Bluff s Elevated Alignment) Attribute -

(VA) Veteran Monthly Assistance Allowance for Disabled Veterans

Revised May 23, 2019 U.S. Department of Veterans Affairs (VA) Veteran Monthly Assistance Allowance for Disabled Veterans Training in Paralympic and Olympic Sports Program (VMAA) In partnership with the United States Olympic Committee and other Olympic and Paralympic entities within the United States, VA supports eligible service and non-service-connected military Veterans in their efforts to represent the USA at the Paralympic Games, Olympic Games and other international sport competitions. The VA Office of National Veterans Sports Programs & Special Events provides a monthly assistance allowance for disabled Veterans training in Paralympic sports, as well as certain disabled Veterans selected for or competing with the national Olympic Team, as authorized by 38 U.S.C. 322(d) and Section 703 of the Veterans’ Benefits Improvement Act of 2008. Through the program, VA will pay a monthly allowance to a Veteran with either a service-connected or non-service-connected disability if the Veteran meets the minimum military standards or higher (i.e. Emerging Athlete or National Team) in his or her respective Paralympic sport at a recognized competition. In addition to making the VMAA standard, an athlete must also be nationally or internationally classified by his or her respective Paralympic sport federation as eligible for Paralympic competition. VA will also pay a monthly allowance to a Veteran with a service-connected disability rated 30 percent or greater by VA who is selected for a national Olympic Team for any month in which the Veteran is competing in any event sanctioned by the National Governing Bodies of the Olympic Sport in the United State, in accordance with P.L. -

Judicial Magistrate Court, Tiruttani Present : Thiru

JUDICIAL MAGISTRATE COURT, TIRUTTANI PRESENT : THIRU. V. LOGANATHAN, B.A., L.L.B., D.No . 834/ 2020 Dated 21.11.2020 COVID19 ADVANCE SPECIAL CAUSE LIST, FOR 23.11.2020 (As per the OM. In D.No 5050/A/2020 dated 24.09.2020 of the Hon'ble Principal District Sessions Judge, Tiruvallur) S. Case No. Name of Parties Name of the counsel Date of Stage of the No Hearing case . 1. C.C.No.79/2015 SI of Police APP for prosecution 23.11.2020 Served Thiruvalangadu P.S and summons of Vs Mr.R.Sivaraj Lw8 & Surendhar & 3 Lw10(I.O) others 2. C.C.No.20/2017 SI of Police APP for prosecution 23.11.2020 Served K.K.Chatram P.S. and summons of Vs Mr.V.Venkatesan Lw5 to Lw7 Chinnasamy 3. C.C.No.78/2016 SI of Police APP for prosecution 23.11.2020 Served Thiruvalangadu P.S. and summons of Vs Mr.S.Suresh Lw10, Lw12 Ganapathy 4. C.C.No.50/2015 SI of Police App for prosecution 23.11.2020 Served Tiruttani P.S and summons of Vs Mr.Jayaprakash Lw2, Lw7 & Ramesh Lw8 5. C.C.No.38/2016 SI of Police App for prosecution 23.11.2020 Served K.K.Chatram P.S and summons of Vs Mr.S.Kathavarayan Lw11 to Prakasam Lw13(I.O) 6. C.C.No.70/2018 SI of Police App for prosecution 23.11.2020 Served Tiruttani P.S. and summons of Vs Mr.V.Venkatesan Lw7, Lw8 Balaji 7. C.C.No.70/2016 Forest Rang Office- App for prosecution 23.11.2020 Served Tiruttani and summons of Vs Mr.V.Venkatesan Lw2, Lw5 to Dheepanraj Lw7 8. -

VISTA2013 Scientific Conference Booklet Gustav-Stresemann-Institut Bonn, 1-4 May 2013

International Paralympic Committee VISTA2013 Scientific Conference Booklet Gustav-Stresemann-Institut Bonn, 1-4 May 2013 “Equipment & Technology in Paralympic Sports” “Equipment & Technology in Paralympic Sports” VISTA2013 Scientific Conference Gustav-Stresemann-Institut Bonn, 1-4 May 2013 The VISTA2013 Conference is organised by: International Paralympic Committee Adenauerallee 212-214 53113 Bonn, Germany Tel. +49 228 2097-200 Fax +49 228 2097-209 [email protected] www.paralympic.org © 2013 International Paralympic Committee I 2 I VISTA2013 Scientific Conference Table of Contents Forewords 4 VISTA2013 Scientific Committee 6 General Information 7 Venue 8 Programme at a Glance 10 Scientific Programme – Detail 12 Keynote Speakers 21 Symposia - Abstracts 26 Free Communications - Abstracts 32 Free Communications - Posters 78 Scientific Information 102 Scientific Award Winner 103 I 3 I VISTA2013 Scientific Conference Forewords Sir Philip Craven, MBE President, International Paralympic Committee Dear participants, On behalf of the International Paralympic Committee (IPC), I would like to welcome you to the 2013 VISTA Conference, the IPC’s scientific conference that will this year centre around the equipment and technology used in Paralympic sport. This conference brings together some of the world’s leading sport scientists, administrators, coaches and athletes. We hope you can take what you learn over the next few days back home with you to your respective communities to help further advance the Paralympic Movement. The next few days will include keynote addresses, symposia, oral presentations and poster sessions put together by the IPC Sports Science Committee that will motivate and influence you in your respective work environments, no matter which part of the Paralympic Movement you represent. -

Dm2021-0259.Pdf

Republic of the Philippines Department of Health OFFICE OF THE SECRETARY May 31, 2021 DEPARTMENT MEMORANDUM No. 2021-0259 TO : ALL UNDERSECRETARIES AND ASSISTANT SECRETARIES: DIRECTORS OF BUREAUS, SERVICES AND CENTERS FOR HEALTH DEVELOPMENT; MINISTER OF HEALTH —- BANGSAMORO AUTONOMOUS REGION IN MUSLIM MINDANAO); EXECUTIVE DIRECTORS OF SPECIALTY HOSPITALS AND NATIONAL NUTRITION COUNCIL; CHIEFS OF MEDICAL CENTERS, HOSPITALS, SANITARIA AND INSTITUTES; PRESIDENT OF THE PHILIPPINE HEALTH INSURANCE CORPORATION; DIRECTORS OF PHILIPPINE NATIONAL AIDS COUNCIL AND TREATMENT AND REHABILITATION CENTERS, AND OTHERS CONCERNED SUBJECT : Implementing Guidelines for Priority Groups A4, AS and Further Clarification of the National Deployment and Vaccination Plan for COVID-19 Vaccines I. RATIONALE On February 23, 2021, the Department of Health (DOH) issued Department Memorandum (DM) No. 2021 - 0099, otherwise known as, “Interim Omnibus Guidelines of the Implementation of the National Vaccine Deployment Plan for COVID-19,” which provided additional guidance on the COVID - 19 vaccine deployment and administration, and outlined the priority groups for the COVID-19 immunization. Succeeding policies were also issued to provide further clarification on the ongoing implementation of the National Deployment and Vaccination Plan for COVID-19 Vaccines (Department Circular No. 2021-0101, DM No. 2021-0157, DM No. 2021-0175, DM 2021- 0203). In accordance with the National Economic and Development Authority (NEDA) recommendations on the eligible population A4 Priority Groups, which was approved in the Inter - Agency Task Force (IATF) for the Management of Emerging Infectious Diseases Resolution No. 117, these implementing guidelines are hereby issued to provide directions for the inoculation of Priority Group A4, namely the frontline personnel in essential sectors, both public and private, including uniformed personnel. -

![Arxiv:2106.13378V1 [Math.CO] 25 Jun 2021 the .Cmiaoiso Vlaodn and Pol Evil-Avoiding Schubert of and Combinatorics Permutations Partitions, on 3](https://docslib.b-cdn.net/cover/3037/arxiv-2106-13378v1-math-co-25-jun-2021-the-cmiaoiso-vlaodn-and-pol-evil-avoiding-schubert-of-and-combinatorics-permutations-partitions-on-3-2903037.webp)

Arxiv:2106.13378V1 [Math.CO] 25 Jun 2021 the .Cmiaoiso Vlaodn and Pol Evil-Avoiding Schubert of and Combinatorics Permutations Partitions, on 3

SCHUBERT POLYNOMIALS, THE INHOMOGENEOUS TASEP, AND EVIL-AVOIDING PERMUTATIONS DONGHYUN KIM AND LAUREN K. WILLIAMS Abstract. Consider a lattice of n sites arranged around a ring, with the n sites occupied by particles of weights {1, 2,...,n}; the possible arrangements of particles in sites thus corresponds to the n! permutations in Sn. The inhomogeneous totally asymmetric simple exclusion process (or TASEP) is a Markov chain on Sn, in which two adjacent particles of weights i < j swap places at rate xi − yn 1 j if the particle of weight j is to the right of the particle of weight i. (Otherwise+ nothing− happens.) When yi = 0 for all i, the stationary distribution was conjecturally linked to Schu- bert polynomials [LW12], and explicit formulas for steady state probabilities were subsequently given in terms of multiline queues [AL14, AM13]. In the case of general yi, Cantini [Can16] showed that n of the n! states have probabilities proportional to double Schubert polynomials. In this paper we introduce the class of evil-avoiding permutations, which are the permutations avoiding the patterns 2413, 4132, 4213 2 √2 n−1 2 √2 n−1 and 3214. We show that there are ( + ) +(2 − ) evil-avoiding permutations in Sn, and for each evil-avoiding permutation w, we give an explicit formula for the steady state probability ψw as a product of double Schubert polynomials. (Con- jecturally all other probabilities are proportional to a positive sum of at least two Schubert polynomials.) When yi = 0 for all i, we give multiline queue formulas for the z-deformed steady state probabilities, and use this to prove the monomial factor conjecture from [LW12].