TW2965 Datasheet

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

"(222A. A772AMMAY Sept

Sept. 29, 1959 L. DIETCH 2,906,814 SIGNAL OPERATED AUTOMATIC COLOR KILLER SYSTEM Filed April 28, l955 2. Sheets-Sheet l AAW22 a a2 aa’ a2/2 ass 122A 2 ASAf MaaZ AVA272M 77AAF42 4. A (So a 72.7 3.39 M269 22 66 (ol) (4) (C) -- - - - Hí2.É.-aws7 (a) A38 INVENTOR. Aawaz A7cay Aza y "(222a. A772AMMAY Sept. 29, 1959 L, DIETCH 2,906,814 SIGNAL OPERATED AUTOMATIC COLOR KILLER SYSTEM Filed April 28, 1955 2 Sheets-Sheet 2 |- 2,906,814 United States Patent Office Patented Sept. 29, 1959 1. 2 the phase of the sync bursts with the phase of the locally produced wave to derive a correction voltage for con trolling the frequency and phase of the oscillator which 2,906,814 produces the reference wave at the receiver. It is SIGNAL OPERATED AUTOMATIC COLOR desirable that synchronization of the receiver's color KILLERSYSTEM reference oscillator have been effected before the chro minance channel is activated, in order to prevent the Leonard Dietch, Haddonfield, N.J., assignor to Radio production of spurious color information pending such Corporation of America, a corporation of Delaware synchronization. Application April 28, 1955, Serial No. 504,503 O It is, therefore, a primary object of the present inven tion to provide new and improved automatic color chan 4 Claims. (C. 178-5.4) nel disabling means. Another object of the invention is the provision of automatic color channel disabling means, the operation The present invention relates to circuitry for automati 15 of which is correlated with the action of the receiver cally switching between two modes of operation and, color. -

Tv Signal Processor for Multi System

To our customers, Old Company Name in Catalogs and Other Documents On April 1st, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding. Renesas Electronics website: http://www.renesas.com April 1st, 2010 Renesas Electronics Corporation Issued by: Renesas Electronics Corporation (http://www.renesas.com) Send any inquiries to http://www.renesas.com/inquiry. Notice 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website. 2. Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others. 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part. 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. -

1966 1967 Color

A HOWARD W. SAMS PUBLICATION NOVEMBER 1966150¢ PF Reporter® the magazine of electronic servicing r 1966 JANUARY AUGUST 2,400,000 color sets sold Know Your 1967 Color Circuits r 1 Servicing Bandpass Amplifiers L . r r plus... 01101,;aa t;It,rA r.u-)V3 ,a.,,,1- .3 Color Chaos A:.; Remote Control Pay TV 7: 3, '; v`. _ 3 r, ^ki New Tube & Transistor Data l FARALc'GR riazi, Improves Color Reception Three Ways 1. Plus GAIN-to provide sharper directivity to Plus -300 and 75 ohm outputs for match to either eliminate multipath reception. twinlead or coax. And full, flat gain over the entire FM band. 2. Plus FLATNESS-to eliminate tilts which cause incorrect colors on the TV screen. Industry Plus these quality mechanical features: Self-clean- experts say that color antennas must be flat within ing wedge -snap locks that tighten with vibration, ±2 db. Paralog-Plus antennas are flat within +1 Cycolac insulators to eliminate cumbersome cross db per channel. feed points, Golden Armor coating, Square boom construction, One-piece antenna array-and more. 3. Plus MATCH -to prevent color -distorting phase shifts. Check on how these plus features can help make plus profits for you. See your Jerrold distributor, The unique feature of the Paralog-Plus is a or write: BI MODAL DIRECTOR system. Its parasitic ele- ments combine two hi -band directors into a single director covering all to -band channels, plus the DISTRIBUTOR SALES DIVISION entire FM band. Thus, more of the elements work 401 Walnut St., Phila., Pa. 19105 to bring in any given channel. -

TW9900 Data Short

DATA SHORT To request the full datasheet, please visit www.intersil.com/products/TW9900 TW9900 FN7767 Low Power NTSC/PAL/SECAM Video Decoder with VBI Slicer Rev 5.00 April 7, 2016 The TW9900 is a low power NTSC/PAL/SECAM video decoder Features chip that is designed for portable applications. It consumes less than 100mW in typical composite input applications. The Video Decoder available power-down mode further reduces the power consumption. It uses the 1.8V for both analog and digital • NTSC (M, 4.43) and PAL (B, D, G, H, I, M, N, N combination), supply voltage and 3.3V for I/O power. A single 27MHz crystal PAL (60), SECAM support with automatic format detection is all that is needed to decode all analog video standards. • Software selectable analog inputs allow any of the following The video decoder decodes the baseband analog CVBS or combinations, e.g., 2 CVBS or 1 Y/C S-video signals into digital 8-bit 4:2:2 YCbCr for output. It • Built-in analog anti-alias filter consists of analog front-end with input source selection, • Two 10-bit ADCs and analog clamping circuit variable gain amplifier and analog-to-digital converters, Y/C separation circuit, multi-standard color decoder (PAL BGHI, • Fully programmable static gain or automatic gain control for PAL M, PAL N, combination PAL N, NTSC M, NTSC 4.43 and the Y-channel SECAM) and synchronization circuitry. The Y/C separation is • Programmable white peak control for the Y-channel done with high quality adaptive 4H comb filter for reduced • 4-H adaptive comb filter Y/C separation cross color and cross luminance. -

TVP5158, TVP5157, TVP5156 Four-Channel PAL/NTSC Video

TVP5158, TVP5157, TVP5156 Four-Channel NTSC/PAL Video Decoders With Independent Scalers, Noise Reduction, Auto Contrast, and Flexible Output Formatter for Security and Other Multi-Channel Video Applications Data Manual PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of the Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters. Literature Number: SLES243G July 2009–Revised April 2013 TVP5158, TVP5157, TVP5156 www.ti.com SLES243G –JULY 2009–REVISED APRIL 2013 Contents 1 Introduction ........................................................................................................................ 8 1.1 Features ...................................................................................................................... 8 1.2 Applications .................................................................................................................. 9 1.3 Description ................................................................................................................... 9 1.4 Related Products ............................................................................................................ 9 1.5 Trademarks ................................................................................................................ 10 1.6 Document Conventions ................................................................................................... 10 1.7 Ordering Information ..................................................................................................... -

Class 348 Television 348 - 1

CLASS 348 TELEVISION 348 - 1 348 TELEVISION 14.01 TWO-WAY VIDEO AND VOICE 37 .With continuously rotating COMMUNICATION (E.G., element VIDEOPHONE) 38 .Multiple channels 14.02 .Over wireless communication 39 .With observer selected field of 14.03 .User interface (e.g., touch view screen menu) 40 HOLOGRAPHIC 14.04 .Operating with other appliance 41 .Color TV (e.g., TV, VCR, FAX, etc.) 42 STEREOSCOPIC 14.05 .Remote control 43 .Signal formatting 14.06 .Answering machine 44 .Pseudo 14.07 .Display arrangement (e.g., 45 .Endoscope multiscreen display) 46 .Picture signal generator 14.08 .Conferencing (e.g., loop) 47 ..Multiple cameras 14.09 ..Conferencing with multipoint 48 ...More than two cameras control unit 49 ..Single camera with optical path 14.1 ..Motion image conferencing division 14.11 .Switching 50 ..Single camera from multiple 14.12 .Transmission control (e.g., positions resolution or quality) 51 .Stereoscopic display device 14.13 ..Compression or decompression 52 ..More than two display devices 14.14 ..Still frame (e.g., freeze 53 ..Viewer attached frame) 54 ..Single display with optical 14.15 ..Field or frame difference path division (e.g., moving frame) 55 ...Separation by time division 14.16 .User positioning (e.g., 56 ....With alternating shutters parallax) 57 ....With alternating polarization 21 PLURAL TRANSMITTER SYSTEM 58 ...Separation by polarization CONSIDERATIONS (E.G., 59 ...Separation by lenticular INTERFERENCE REDUCTION) screen 22 SLOW SCANNING TRANSMISSION (E.G., 60 ...Separation by color (i.e., STILL FRAME) anaglyphic) -

Stv2310 Stv2310

® STV2310 Multistandard TV/VCR Digital Video Decoder and Output Scaler PRELIMINARY DATA Fully Automatic Line C PAL/NTSC/SECAM Format Decoder Analog to Luma Converter CVBS1/Y Digital Chroma and CVBS2/Y Conversion Separator Adaptive Output and SRC Luminance Delay Scaler Data Slicer (TxT, CC, ...) Data Selection YCrCb[7:0] R/Cr Analog to Cr Cb G Digital Tint and Output Interface Clock B/Cb Conversion Control Synchronization HSYNC and IC Monitoring VSYNC Field STV2310 MAIN FEATURES ■ Automatic NTSC/PAL/SECAM Digital Chroma ■ Programmable Horizontal Scaling (x0.25 to Decoder x4 Scaling Factor) and Panorama Vision ■ Worldwide TV Standards Compatible ■ Programmable Cr, Cb output amplitude ■ VBI Data Slicer for Teletext, Closed Caption, ■ Copy-Protection System compatible WSS and other systems ■ H and V Synchronization Processing that is ■ NTSC/PAL Adaptive 4H/2D Comb Filter robust to non-standard sources ■ Analog RGB/Fast Blanking Capture and ■ Single System Clock for all Video Input Insertion in YCrCb Output Flow (SCART Formats legacy) ■ Two-wire I²C Bus Interface up to 400 kHz ■ Analog YCrCb inputs with Tint Control ■ Typical Power Consumption: 500 mW ■ Automatic Flesh Control on 117° or 123° ■ Power Supply: 1.8 V and 3.3 V Color Axis References The STV2310 is a high-quality front-end video ■ NTSC Hue Control circuit for processing all analog NTSC/PAL/SECAM ■ Line-locked ITU-R BT. 656/601 or Square standards into a 4:2:2 YCrCb video format. The Pixel YCrCb Outputs (Data and Clock) STV2310 is programmable through an I²C ■ Orthogonal Correction on Output Pixels interface. ■ ITU-R BT.601 (and Square Pixel) Resolution The STV2310 provides a cost-effective solution for for all Standards TV sets, STBs, DVD Recordable devices and PVR applications. -

Techwell Techwell

Techwell Mixed Signal Semiconductor Solutions TECHWELL VIDEO DECODERS NTSC/PAL/SECAM Video Decoder for Multimedia Applications Features TW9920 Multi-Standard Video Decoder and Encoder Target Applications Digital Camcorder The TW9920 is a multi-standard video decoder and encoder chip that Portable Media Player (PMP) is designed for multimedia applications. It uses the mixed-signal 2.5V Mobile Phone and PDA CMOS technology to provide a low-power integrated solution. The video encoder is used to encoder digital YcbCr input into analog CVBS or S-video output. With five built-in DACs, it can simultaneously support Video Decoder analog YcbCr output in addition to S-video output for various applications. NTSC (M, 4.43) and PAL (B, D, G, H, I, M, N, N It can support both NTSC (60Hz) and PAL (50Hz) output. A stable crystal combination), PAL (60), SECAM support with generated 27MHz clock is used for all necessary sub-carrier generation. It automatic format detection accepts ITU-R 656 compatible digital input externally. The video decoder Software selectable analog inputs allows any decodes the analog CVBS or S-video signals into digital YcbCr for output. of the following combinations, e.g. 4 CVBS or ( 3 CVBS and 1 Y/C ). It consists of analog front-end with input source selection, variable gain Two 9-bit ADCs and analog clamping circuit. amplifier and analog-to-digital converters, Y/C separation circuit, multi- Fully programmable static gain or automatic standard color decoder (PAL BGHI, PAL M, PAL N, combination PAL N, NTSC gain control for the Y channel M, NTSC 4.43 and SECAM) and synchronization circuitry.The Y/C separation Programmable white peak control for the Y or is done with highly adaptive 4H comb filter for reduced cross color and CVBS channel 4-H adaptive comb filter Y/C separation cross luminance. -

„Il“ 4,1M. .___15 L

& Nov. 17, 197 QJ. HALL Erm. 3,541,242 - ‘ COLOR TEMPERATURE> CORRECTION CONTROLLED BY THE COLOR \ KILLER AND COLOR OSCILLATOR Filed Dec. 16, 1968 / man ¿Mmm/:F 47 4d è? ÜW/al/f „il“ 4,1m. .___15 l Y /70 v f5 y `BY ÀTTURNEY - 3,541,242 v‘United States Patent Oliice Patented Nov. 17, 1970 1 2 the amount of developed direct voltage and thereby con~ ` 3,541,242 trols the .switching of the amplifier device. Since the sig COLOR TEMPERATURE CORRECTION CON nal being rectified is of high frequency, the amount of TROLLED BY THE COLOR KILLER AND filter capacitance required is relatively low, thus permit COLOR OSCILLATOR Cyril J. Hall, Hor-gen, and René Peter, Basel, Switzerland, ting the bias circuit to present relatively 10W capacitance assignors to RCA Corporation, a corporation of Dela to the amplifier device. ware Reference is now made to the following description Filed Dec. 16, 1968, Ser. No. 783,915 taken in conjunction with the accompanying drawing in Claims priority, application Great Britain, Aug. 27, 1968, Which: 40,979/68 10 FIG. 1 is a schematic circuit diagram partially in block Int. Cl. H04n 9/48 form of a television receiver embodying the present inven U-S. Cl. 178-5.4 9 Claims tion. FIG. 2 is a schematic circuit diagram partially in block ABSTRACT OF THE DISCLOSURE form of another embodiment according to the invention. 15 Although the receiver to be described is for NTSC sig A transistor is used to switch the drive level to a color nals, the invention is applicable to other transmission kinescope between a relatively high color temperature standards such as PAL or SECAM. -

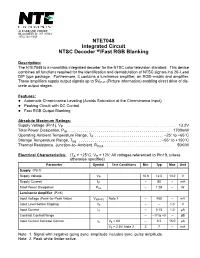

NTE7048 Integrated Circuit NTSC Decoder W/Fast RGB Blanking

NTE7048 Integrated Circuit NTSC Decoder w/Fast RGB Blanking Description: The NTE7048 is a monolithic integrated decoder for the NTSC color television standard. This device combines all functions required for the identification and demodulation of NTSC signals ina 20–Lead DIP type package. Furthermore, it contains a luminance amplifier, an RGB–matrix and amplifier. These amplifiers supply output signals up to 5VP–P (Picture information) enabling direct drive of dis- crete output stages. Features: D Automatic Chrominance Leveling (Avoids Saturation at the Chrominance Input) D Peaking Circuit with DC Control D Fast RGB Output Blanking Absolute Maximum Ratings: Supply Voltage (Pin1), VP . 13.2V Total Power Dissipation, Ptot . 1700mW Operating Ambient Temperature Range, TA . –25° to +65°C Storage Temperature Range, Tstg . –55° to +150°C Thermal Resistance, Junction–to–Ambient, RthJA . 50K/W Electrical Characteristics: (TA = +25°C, VP = 12V, All voltages referenced to Pin19, unless otherwise specified) Parameter Symbol Test Conditions Min Typ Max Unit Supply (Pin1) Supply Voltage VP 10.8 12.0 13.2 V Supply Current IP – 90 – mA Total Power Dissipation Ptot – 1.08 – W Luminance Amplifier (Pin8) Input Voltage (Peak–to–Peak Value) V8(P–P) Note 1 – 450 – mV Input Level before Clipping V8 – – 1.0 V Input Current I8 – 0.15 1.0 µA Contrast Control Range – –17 to +3 – dB Input Current Contrast Control I6 V6 < 6V – 0.5 15.0 µA V6 = 2.5V, Note 2 3 7 – mA Note 1. Signal with negative going sync; amplitude includes sync. pulse amplitude. Note 2. Peak white -

Enhancing Your Apple® Ii Volume 1

ENHANCING YOUR APPLE® II VOLUME 1 Second Edition Don Lancaster heads Synergetics, a new-age prototyping and consulting firm involved in micro applications and electronic design. He is the well-known author of the classic CMOS and TTL Cookbooks. He is one of the microcomputer pioneers, having introduced the first hobbyist integrated-circuit projects, the first sanely priced digital-electronics modules, the first low-cost TVT-1 video display terminal, the first personal computing keyboards, and lots more. Don's numerous books and articles on personal computing and electronic applications have set new standards as under standable, useful, and exciting technical writing. Don's other interests include eco logical studies, firefighting, cave exploration, bicycling, and tinaja questing. Other SAMS books by Don Lancaster include Active Filter Cookbook, CMOS Cook book, TTL Cookbook, RTL Cookbook (out of print), TVT Cookbook, Cheap Video Cookbook, Son of Cheap Video, The Hexadecimal Chronicles, The Incredible Secret Money Machine (available only from Synergetics), Don Lancaster's Micro Cookbooks Volumes 1 and 2, and Don Lancaster's Assembly Cookbook for the Apple II and lie. ENHANCING YOUR APPLE® II VOLUME 1 Second Edition by Don Lancaster Howard W. Sams & Co., Inc. 4300 WEST 62ND ST. INOIANAPOLIS, INOIANA 46268 USA Apple is a registered trademark of Apple Computer Inc., Cupertino, CA. Franklin Ace 1000 and Franklin Ace 1200 are trademarks of Franklin Computer Corp., Cherry Hill, NJ. Copyright© 1982 and 1984 by Howard W. Sams & Co., Inc. Indianapolis, IN 46268 SECOND EDITION FIRST PRINTING-1984 All rights reserved. No part of this book shall be reproduced, stored in a retrieval system, or transmitted by any means, electronic, mechanical, photocopying, recording, or otherwise, without written permission from the publisher. -

Enhancing Your App E 118 Vol.1 ~~~ Don Lancaster

21846 ENHANCING YOUR APP E 118 VOL.1 ~~~ DON LANCASTER ENHANCEMENTS INSIDE • Two Glompers • Software Color Killer • Tearing Into Machine Language • Field Sync • Fun With Mixed Fields • 121 Lores Colors • The Glitch Stomper • Gentle Scroll • Fast Backgrounder s4-n1t- NwtM·f& ~ ,r,,r ENHANCING YOUR APPLE II® VOLUME 1 DON LANCASTER heads Synergetics, a new-age design and consulting firm involved in microcomputer applications and electronic design. He is well known as the author of the classic CMOS and TTL Cookbooks. His many other books and hundreds of articles on personal computing and electronic applications have set new standards as understandable, useful, and exciting technical writing. Don's other interests include ecological studies, firefighting, cave exploration, bicycling, and tinaja questing. Other SAMS books by Don include Active Filter Cookbook CMOS Cookbook TTL Cookbook Cheap Video Cookbook Son of Cheap Video, TV Typewriter Cookbook The Hexadecimal Chronicles, Don Lancaster's Micro Cookbook, and The Incredible Secret Money Machine. ENHANCING YOUR APPLE II® VOLUME 1 by Don tancaster *Apple and Apple II are registered trademarks of Apple Computer Inc., Cuper tino, CA. Copyright @ 1982 by Howard W. Sams & Co., Inc. Indianapolis, IN 46268 FIRST EDITION SECOND PRINTING-1983 All rights reserved. No part of this book shall be reproduced, stored in a retrieval system, or transmitted by any means, electronic, mechanical, photocopying, recording, or otherwise, without written permission from the publisher. No patent liability is assumed with respect to the use of the information contained herein. While every precaution has been taken in the preparation of this book, the publisher assumes no responsibility for errors or omissions.