MVME55006E Single Board Computer Installation and Use P/N: 6806800A37K September 2019 © 2019 SMART Embedded Computing™, Inc

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Group Developed Weighing Matrices∗

AUSTRALASIAN JOURNAL OF COMBINATORICS Volume 55 (2013), Pages 205–233 Group developed weighing matrices∗ K. T. Arasu Department of Mathematics & Statistics Wright State University 3640 Colonel Glenn Highway, Dayton, OH 45435 U.S.A. Jeffrey R. Hollon Department of Mathematics Sinclair Community College 444 W 3rd Street, Dayton, OH 45402 U.S.A. Abstract A weighing matrix is a square matrix whose entries are 1, 0 or −1,such that the matrix times its transpose is some integer multiple of the identity matrix. We examine the case where these matrices are said to be devel- oped by an abelian group. Through a combination of extending previous results and by giving explicit constructions we will answer the question of existence for 318 such matrices of order and weight both below 100. At the end, we are left with 98 open cases out of a possible 1,022. Further, some of the new results provide insight into the existence of matrices with larger weights and orders. 1 Introduction 1.1 Group Developed Weighing Matrices A weighing matrix W = W (n, k) is a square matrix, of order n, whose entries are in t the set wi,j ∈{−1, 0, +1}. This matrix satisfies WW = kIn, where t denotes the matrix transpose, k is a positive integer known as the weight, and In is the identity matrix of size n. Definition 1.1. Let G be a group of order n.Ann×n matrix A =(agh) indexed by the elements of the group G (such that g and h belong to G)issaidtobeG-developed if it satisfies the condition agh = ag+k,h+k for all g, h, k ∈ G. -

1.8-600 Mhz, 150 W CW, 50 V RF Power LDMOS Transistor Data Sheet

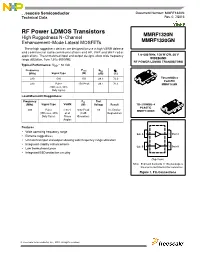

Freescale Semiconductor Document Number: MMRF1320N Technical Data Rev. 0, 7/2015 RF Power LDMOS Transistors MMRF1320N High Ruggedness N--Channel Enhancement--Mode Lateral MOSFETs MMRF1320GN These high ruggedness devices are designed for use in high VSWR defense and commercial radio communications and HF, VHF and UHF radar applications. The unmatched input and output designs allow wide frequency 1.8–600 MHz, 150 W CW, 50 V range utilization, from 1.8 to 600 MHz. WIDEBAND RF POWER LDMOS TRANSISTORS Typical Performance: VDD =50Vdc Frequency Pout Gps D (MHz) Signal Type (W) (dB) (%) 230 CW 150 26.3 72.0 TO--270WB--4 PLASTIC 230 Pulse 150 Peak 26.1 70.3 MMRF1320N (100 sec, 20% Duty Cycle) Load Mismatch/Ruggedness Frequency Pin Test (MHz) Signal Type VSWR (W) Voltage Result TO--270WBG--4 PLASTIC 230 Pulse > 65:1 0.62 Peak 50 No Device MMRF1320GN (100 sec, 20% at all (3 dB Degradation Duty Cycle) Phase Overdrive) Angles Features Wide operating frequency range Gate A 32Drain A Extreme ruggedness Unmatched input and output allowing wide frequency range utilization Integrated stability enhancements Gate B 41Drain B Low thermal resistance Integrated ESD protection circuitry (Top View) Note: Exposed backside of the package is the source terminal for the transistors. Figure 1. Pin Connections Freescale Semiconductor, Inc., 2015. All rights reserved. MMRF1320N MMRF1320GN RF Device Data Freescale Semiconductor, Inc. 1 Table 1. Maximum Ratings Rating Symbol Value Unit Drain--Source Voltage VDSS –0.5, +133 Vdc Gate--Source Voltage VGS –6.0, +10 Vdc Storage Temperature Range Tstg –65 to +150 C Case Operating Temperature Range TC –40 to +150 C (1,2) Operating Junction Temperature Range TJ –40 to +225 C Total Device Dissipation @ TC =25C PD 952 W Derate above 25C 4.76 W/C Table 2. -

MRFE6VP5600H.Pdf

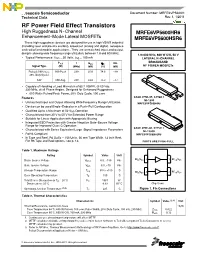

Freescale Semiconductor Document Number: MRFE6VP5600H Technical Data Rev. 1, 1/2011 RF Power Field Effect Transistors High Ruggedness N--Channel MRFE6VP5600HR6 Enhancement--Mode Lateral MOSFETs MRFE6VP5600HSR6 These high ruggedness devices are designed for use in high VSWR industrial (including laser and plasma exciters), broadcast (analog and digital), aerospace and radio/land mobile applications. They are unmatched input and output designs allowing wide frequency range utilization, between 1.8 and 600 MHz. 1.8--600 MHz, 600 W CW, 50 V • Typical Performance: VDD =50Volts,IDQ = 100 mA LATERAL N--CHANNEL BROADBAND Pout f Gps ηD IRL Signal Type (W) (MHz) (dB) (%) (dB) RF POWER MOSFETs Pulsed (100 μsec, 600 Peak 230 25.0 74.6 -- 1 8 20% Duty Cycle) CW 600 Avg. 230 24.6 75.2 -- 1 7 • Capable of Handling a Load Mismatch of 65:1 VSWR, @ 50 Vdc, 230 MHz, at all Phase Angles, Designed for Enhanced Ruggedness • 600 Watts Pulsed Peak Power, 20% Duty Cycle, 100 μsec Features CASE 375D--05, STYLE 1 NI--1230 • Unmatched Input and Output Allowing Wide Frequency Range Utilization MRFE6VP5600HR6 • Device can be used Single--Ended or in a Push--Pull Configuration • Qualified Up to a Maximum of 50 VDD Operation • Characterized from 30 V to 50 V for Extended Power Range • Suitable for Linear Application with Appropriate Biasing • Integrated ESD Protection with Greater Negative Gate--Source Voltage Range for Improved Class C Operation CASE 375E--04, STYLE 1 • Characterized with Series Equivalent Large--Signal Impedance Parameters NI--1230S • RoHS Compliant MRFE6VP5600HSR6 • In Tape and Reel. R6 Suffix = 150 Units, 56 mm Tape Width, 13 inch Reel. -

MVME8100/MVME8105/MVME8110 Installation and Use P/N: 6806800P25O September 2019

MVME8100/MVME8105/MVME8110 Installation and Use P/N: 6806800P25O September 2019 © 2019 SMART™ Embedded Computing, Inc. All Rights Reserved. Trademarks The stylized "S" and "SMART" is a registered trademark of SMART Modular Technologies, Inc. and “SMART Embedded Computing” and the SMART Embedded Computing logo are trademarks of SMART Modular Technologies, Inc. All other names and logos referred to are trade names, trademarks, or registered trademarks of their respective owners. These materials are provided by SMART Embedded Computing as a service to its customers and may be used for informational purposes only. Disclaimer* SMART Embedded Computing (SMART EC) assumes no responsibility for errors or omissions in these materials. These materials are provided "AS IS" without warranty of any kind, either expressed or implied, including but not limited to, the implied warranties of merchantability, fitness for a particular purpose, or non-infringement. SMART EC further does not warrant the accuracy or completeness of the information, text, graphics, links or other items contained within these materials. SMART EC shall not be liable for any special, indirect, incidental, or consequential damages, including without limitation, lost revenues or lost profits, which may result from the use of these materials. SMART EC may make changes to these materials, or to the products described therein, at any time without notice. SMART EC makes no commitment to update the information contained within these materials. Electronic versions of this material may be read online, downloaded for personal use, or referenced in another document as a URL to a SMART EC website. The text itself may not be published commercially in print or electronic form, edited, translated, or otherwise altered without the permission of SMART EC. -

RF Power LDMOS Transistor

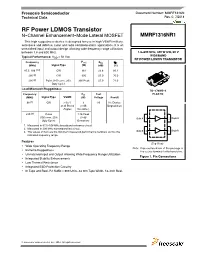

Freescale Semiconductor Document Number: MMRF1316N Technical Data Rev. 0, 7/2014 RF Power LDMOS Transistor N--Channel Enhancement--Mode Lateral MOSFET MMRF1316NR1 This high ruggedness device is designed for use in high VSWR military, aerospace and defense, radar and radio communications applications. It is an unmatched input and output design allowing wide frequency range utilization, between 1.8 and 600 MHz. 1.8–600 MHz, 300 W CW, 50 V WIDEBAND Typical Performance: VDD =50Vdc RF POWER LDMOS TRANSISTOR Frequency Pout Gps D (MHz) Signal Type (W) (dB) (%) 87.5--108 (1,3) CW 361 23.8 80.1 230 (2) CW 300 25.0 70.0 230 (2) Pulse (100 sec, 20% 300 Peak 27.0 71.0 Duty Cycle) Load Mismatch/Ruggedness TO--270WB--4 Frequency Pin Test PLASTIC (MHz) Signal Type VSWR (W) Voltage Result 98 (1) CW > 65:1 3 50 No Device at all Phase (3 dB Degradation Angles Overdrive) 230 (2) Pulse 1.16 Peak (100 sec, 20% (3 dB Gate A 32Drain A Duty Cycle) Overdrive) 1. Measured in 87.5–108 MHz broadband reference circuit. 2. Measured in 230 MHz narrowband test circuit. 3. The values shown are the minimum measured performance numbers across the Gate B 41Drain B indicated frequency range. Features (Top View) Wide Operating Frequency Range Note: Exposed backside of the package is Extreme Ruggedness the source terminal for the transistors. Unmatched Input and Output Allowing Wide Frequency Range Utilization Figure 1. Pin Connections Integrated Stability Enhancements Low Thermal Resistance Integrated ESD Protection Circuitry In Tape and Reel. R1 Suffix = 500 Units, 44 mm Tape Width, 13--inch Reel. -

MVME5100 Single Board Computer Installation and Use Manual Provides the Information You Will Need to Install and Configure Your MVME5100 Single Board Computer

MVME5100 Single Board Computer Installation and Use V5100A/IH3 April 2002 Edition © Copyright 1999, 2000, 2001, 2002 Motorola, Inc. All rights reserved. Printed in the United States of America. Motorola and the Motorola logo are registered trademarks and AltiVec is a trademark of Motorola, Inc. All other products mentioned in this document are trademarks or registered trademarks of their respective holders. Safety Summary The following general safety precautions must be observed during all phases of operation, service, and repair of this equipment. Failure to comply with these precautions or with specific warnings elsewhere in this manual could result in personal injury or damage to the equipment. The safety precautions listed below represent warnings of certain dangers of which Motorola is aware. You, as the user of the product, should follow these warnings and all other safety precautions necessary for the safe operation of the equipment in your operating environment. Ground the Instrument. To minimize shock hazard, the equipment chassis and enclosure must be connected to an electrical ground. If the equipment is supplied with a three-conductor AC power cable, the power cable must be plugged into an approved three-contact electrical outlet, with the grounding wire (green/yellow) reliably connected to an electrical ground (safety ground) at the power outlet. The power jack and mating plug of the power cable meet International Electrotechnical Commission (IEC) safety standards and local electrical regulatory codes. Do Not Operate in an Explosive Atmosphere. Do not operate the equipment in any explosive atmosphere such as in the presence of flammable gases or fumes. Operation of any electrical equipment in such an environment could result in an explosion and cause injury or damage. -

Kronecker Powers of Tensors Useful for Strassen's Laser Method

KRONECKER POWERS OF TENSORS AND STRASSEN'S LASER METHOD AUSTIN CONNER, FULVIO GESMUNDO, JOSEPH M. LANDSBERG, EMANUELE VENTURA Abstract. We answer a question, posed implicitly in [16, x11], [9, Rem. 15.44] and explicitly in [7, Problem 9.8], showing the border rank of the Kronecker square of the little Coppersmith- Winograd tensor is the square of the border rank of the tensor for all q > 2, a negative result for complexity theory. We further show that when q > 4, the analogous result holds for the Kronecker cube. In the positive direction, we enlarge the list of explicit tensors potentially useful for the laser method. We observe that a well-known tensor, the 3 × 3 determinant polynomial 9 9 9 regarded as a tensor, det3 2 C ⊗ C ⊗ C , could potentially be used in the laser method to prove the exponent of matrix multiplication is two. Because of this, we prove new upper bounds on its Waring rank and rank (both 18), border rank and Waring border rank (both 17), which, in addition to being promising for the laser method, are of interest in their own right. We discuss \skew" cousins of the little Coppersmith-Winograd tensor and indicate whey they may be useful for the laser method. We establish general results regarding border ranks of Kronecker 3 3 3 powers of tensors, and make a detailed study of Kronecker squares of tensors in C ⊗ C ⊗ C . 3 3 3 In particular we show numerically that for generic tensors in C ⊗ C ⊗ C , the rank and border rank are strictly sub-multiplicative. -

An Investigation of Group Developed Weighing Matrices

AN INVESTIGATION OF GROUP DEVELOPED WEIGHING MATRICES A thesis submitted in partial fulllment of the requirements for the degree of Master of Science By JEFF R. HOLLON B.S., Wright State University, 2008 2010 Wright State University WRIGHT STATE UNIVERSITY SCHOOL OF GRADUATE STUDIES June 1, 2010 I HEREBY RECOMMEND THAT THE THESIS PREPARED UNDER MY SUPERVI- SION BY Je R. Hollon ENTITLED An Investigation of Group Developed Weighing Matrices BE ACCEPTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF Master of Science. ____________________ K.T. Arasu, Ph.D. Thesis Director ____________________ Weifu Fang, Ph.D. Department Chair Committee on Final Examination ____________________ K.T. Arasu, Ph.D. ____________________ Yuqing Chen, Ph.D. ____________________ Xiaoyu Liu, Ph.D. ____________________ John Bantle, Ph.D. Interim Dean, School of Graduate Studies Abstract Hollon, Je R. M.S., Department of Mathematics and Statistics, Wright State University, 2010. An Investigation of Group Developed Weighing Matrices. A weighing matrix is a square matrix whose entries are 1, 0 or -1 and has the property that the matrix times its transpose is some integer multiple of the identity matrix. We examine the case where these matrices are said to be developed by an abelian group. Through a combination of extending previous results and by giving explicit constructions we will answer the question of existence for 318 such matrices of order and weight both below 100. At the end, we are left with 98 open cases out of a possible 1,022. Further, some of the new results provide insight into the existence of matrices with larger weights and orders. -

MVME6100 Single Board Computer Installation and Use P/N: 6806800D58E March 2009

Embedded Computing for Business-Critical ContinuityTM MVME6100 Single Board Computer Installation and Use P/N: 6806800D58E March 2009 © 2009 Emerson All rights reserved. Trademarks Emerson, Business-Critical Continuity, Emerson Network Power and the Emerson Network Power logo are trademarks and service marks of Emerson Electric Co. © 2008 Emerson Electric Co. All other product or service names are the property of their respective owners. Intel® is a trademark or registered trademark of Intel Corporation or its subsidiaries in the United States and other countries. Java™ and all other Java-based marks are trademarks or registered trademarks of Sun Microsystems, Inc. in the U.S. and other countries. Microsoft®, Windows® and Windows Me® are registered trademarks of Microsoft Corporation; and Windows XP™ is a trademark of Microsoft Corporation. PICMG®, CompactPCI®, AdvancedTCA™ and the PICMG, CompactPCI and AdvancedTCA logos are registered trademarks of the PCI Industrial Computer Manufacturers Group. UNIX® is a registered trademark of The Open Group in the United States and other countries. Notice While reasonable efforts have been made to assure the accuracy of this document, Emerson assumes no liability resulting from any omissions in this document, or from the use of the information obtained therein. Emerson reserves the right to revise this document and to make changes from time to time in the content hereof without obligation of Emerson to notify any person of such revision or changes. Electronic versions of this material may be read online, downloaded for personal use, or referenced in another document as a URL to a Emerson website. The text itself may not be published commercially in print or electronic form, edited, translated, or otherwise altered without the permission of Emerson, It is possible that this publication may contain reference to or information about Emerson products (machines and programs), programming, or services that are not available in your country. -

Reusable Multi-Stage Multi-Secret Sharing Schemes Based on CRT Anjaneyulu Endurthi, Oinam Bidyapati Chanu, Appala Naidu Tentu, and V

JOURNAL OF COMMUNICATIONS SOFTWARE AND SYSTEMS, VOL. 11, NO. 1, MARCH 2015 15 Reusable Multi-Stage Multi-Secret Sharing Schemes Based on CRT Anjaneyulu Endurthi, Oinam Bidyapati Chanu, Appala Naidu Tentu, and V. Ch. Venkaiah Abstract—Three secret sharing schemes that use the Mignotte’s of nuclear systems, can be stored by using secret sharing sequence and two secret sharing schemes that use the Asmuth- schemes. Bloom sequence are proposed in this paper. All these five secret Secret sharing was first proposed by Blakley[3] and sharing schemes are based on Chinese Remainder Theorem (CRT) [8]. The first scheme that uses the Mignotte’s sequence is Shamir[4]. The scheme by Shamir relies on the standard a single secret scheme; the second one is an extension of the first Lagrange polynomial interpolation, whereas the scheme by one to Multi-secret sharing scheme. The third scheme is again Blakley[3] is based on the geometric idea that uses the concept for the case of multi-secrets but it is an improvement over the of intersecting hyperplanes. second scheme in the sense that it reduces the number of public The family of authorized subsets is known as the access values. The first scheme that uses the Asmuth-Bloom sequence is designed for the case of a single secret and the second one is structure. An access structure is said to be monotone if an extension of the first scheme to the case of multi-secrets. a set is qualified then its superset must also be qualified. Novelty of the proposed schemes is that the shares of the Several access structures are proposed in the literature. -

Groups with at Most Twelve Subgroups

Groups With At Most Twelve Subgroups Michael C. Slattery Marquette University, Milwaukee WI 53201-1881 [email protected] July 9, 2020 In [2] I showed that the finite groups with a specified number of subgroups can always be described as a finite list of similarity classes. Neil Sloane suggested that I submit the corresponding sequence, the number of similarity classes with n subgroups, to his Online Encyclopedia of Integer Sequences [4]. I thought this would be a quick calculation until I discovered that my “example” case in the paper (n = 6) was wrong (as noted in [3]). I realized that producing a reliable count required a full proof. This note contains the proof behind my computation of the first 12 terms of the sequence. For completeness, we include a section of [2]: Now, we saw [above] that cyclic Sylow subgroups of G which are direct factors allow many non-isomorphic groups to have the same number of subgroups. [This lemma] tells us that these are precisely the cyclic Sylow subgroups which lie in the center of G. Consequently, if p1,...,pc are the primes which divide |G| such that a Sylow pi-subgroup is cyclic and central, then we can write G = P1 × P2 ×···× Pc × Oπ′ (G) where each Pi is a Sylow pi-subgroup, the set π = {p1,...,pc} and Oπ′ (G) is the largest normal subgroup of G with order not divisible by any prime in π. We e e will write G = O ′ (G). In other words, G is the unique subgroup of G left after arXiv:1607.01834v2 [math.GR] 7 Jul 2020 π factoring out the cyclic, central Sylow subgroups. -

A Tutorial on Conformal Prediction

Journal of Machine Learning Research 9 (2008) 371-421 Submitted 8/07; Published 3/08 A Tutorial on Conformal Prediction Glenn Shafer∗ [email protected] Department of Accounting and Information Systems Rutgers Business School 180 University Avenue Newark, NJ 07102, USA Vladimir Vovk [email protected] Computer Learning Research Centre Department of Computer Science Royal Holloway, University of London Egham, Surrey TW20 0EX, UK Editor: Sanjoy Dasgupta Abstract Conformal prediction uses past experience to determine precise levels of confidence in new pre- dictions. Given an error probability ε, together with a method that makes a prediction yˆ of a label y, it produces a set of labels, typically containing yˆ, that also contains y with probability 1 − ε. Conformal prediction can be applied to any method for producing yˆ: a nearest-neighbor method, a support-vector machine, ridge regression, etc. Conformal prediction is designed for an on-line setting in which labels are predicted succes- sively, each one being revealed before the next is predicted. The most novel and valuable feature of conformal prediction is that if the successive examples are sampled independently from the same distribution, then the successive predictions will be right 1 − ε of the time, even though they are based on an accumulating data set rather than on independent data sets. In addition to the model under which successive examples are sampled independently, other on-line compression models can also use conformal prediction. The widely used Gaussian linear model is one of these. This tutorial presents a self-contained account of the theory of conformal prediction and works through several numerical examples.