Intel La-9241P

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Global Capital, the State, and Chinese Workers: the Foxconn Experience

MCX38410.1177/0097700 447164412447164Pun and ChanModern China © 2012 SAGE Publications Reprints and permission: sagepub.com/journalsPermissions.nav Articles Modern China 38(4) 383 –410 Global Capital, the State, © 2012 SAGE Publications Reprints and permission: and Chinese Workers: sagepub.com/journalsPermissions.nav DOI: 10.1177/0097700412447164 The Foxconn Experience http://mcx.sagepub.com Pun Ngai1 and Jenny Chan2 Abstract In 2010, a startling 18 young migrant workers attempted suicide at Foxconn Technology Group production facilities in China. This article looks into the development of the Foxconn Corporation to understand the advent of capi- tal expansion and its impact on frontline workers’ lives in China. It also pro- vides an account of how the state facilitates Foxconn’s production expansion as a form of monopoly capital. Foxconn stands out as a new phenomenon of capital expansion because of the incomparable speed and scale of its capital accumulation in all regions of China. This article explores how the workers at Foxconn, the world’s largest electronics manufacturer, have been subjected to work pressure and desperation that might lead to suicides on the one hand but also open up daily and collective resistance on the other hand. Keywords global capital, Chinese state, student workers, rural migrant workers, Foxconn Technology Group When Time magazine nominated workers in China as the runners-up for the 2009 Person of the Year, the editor commented that Chinese workers have brightened the future of humanity by “leading the world to economic 1Hong Kong Polytechnic University, Kowloon, Hong Kong 2Royal Holloway, University of London, Surrey, UK Corresponding Author: Pun Ngai, Department of Applied Social Sciences, Hong Kong Polytechnic University, Kowloon, Hong Kong Email: [email protected] 384 Modern China 38(4) recovery” (Time, Dec. -

Compal Electronics, Inc. and Subsidiaries

1 Stock Code:2324 COMPAL ELECTRONICS, INC. AND SUBSIDIARIES Consolidated Financial Statements With Independent Auditors’ Review Report For the Nine Months Ended September 30, 2019 and 2018 Address: No.581 & 581-1, Ruiguang Rd., Neihu District, Taipei, Taiwan Telephone: (02)8797-8588 2 Table of contents Contents Page 1. Cover Page 1 2. Table of Contents 2 3. Independent Auditors’ Review Report 3 4. Consolidated Balance Sheets 4 5. Consolidated Statements of Comprehensive Income 5 6. Consolidated Statements of Changes in Equity 6 7. Consolidated Statements of Cash Flows 7 8. Notes to the Consolidated Financial Statements (1) Company history 8 (2) Approval date and procedures of the consolidated financial statements 8 (3) New standards, amendments and interpretations adopted 8~11 (4) Summary of significant accounting policies 11~21 (5) Significant accounting assumptions and judgments, and major sources 21 of estimation uncertainty (6) Explanation of significant accounts 21~63 (7) Related-party transactions 63~65 (8) Pledged assets 65 (9) Commitments and contingencies 66 (10) Losses due to major disasters 66 (11) Subsequent events 66 (12) Other 66~67 (13) Other disclosures (a) Information on significant transactions 67, 69~79 (b) Information on investees 68, 80~85 (c) Information on investment in Mainland China 68, 86~88 (14) Segment information 68 3 Independent Auditors’ Review Report To COMPAL ELECTRONICS, INC.: Introduction We have reviewed the accompanying consolidated balance sheets of COMPAL ELECTRONICS, INC. (the “Company”) and its subsidiaries (the “Group”) as of September 30, 2019 and 2018, and the related consolidated statements of comprehensive income for the three months and nine months then ended, as well as the changes in equity and cash flows for the nine months then ended, and notes to the consolidated financial statements, including a summary of significant accounting policies. -

Taiwan's Top 50 Corporates

Title Page 1 TAIWAN RATINGS CORP. | TAIWAN'S TOP 50 CORPORATES We provide: A variety of Chinese and English rating credit Our address: https://rrs.taiwanratings.com.tw rating information. Real-time credit rating news. Credit rating results and credit reports on rated corporations and financial institutions. Commentaries and house views on various industrial sectors. Rating definitions and criteria. Rating performance and default information. S&P commentaries on the Greater China region. Multi-media broadcast services. Topics and content from Investor outreach meetings. RRS contains comprehensive research and analysis on both local and international corporations as well as the markets in which they operate. The site has significant reference value for market practitioners and academic institutions who wish to have an insight on the default probability of Taiwanese corporations. (as of June 30, 2015) Chinese English Rating News 3,440 3,406 Rating Reports 2,006 2,145 TRC Local Analysis 462 458 S&P Greater China Region Analysis 76 77 Contact Us Iris Chu; (886) 2 8722-5870; [email protected] TAIWAN RATINGS CORP. | TAIWAN'S TOP 50 CORPORATESJenny Wu (886) 2 872-5873; [email protected] We warmly welcome you to our latest study of Taiwan's top 50 corporates, covering the island's largest corporations by revenue in 2014. Our survey of Taiwan's top corporates includes an assessment of the 14 industry sectors in which these companies operate, to inform our views on which sectors are most vulnerable to the current global (especially for China) economic environment, as well as the rising strength of China's domestic supply chain. -

Compal Electronics, Inc. and Subsidiaries

1 Stock Code:2324 COMPAL ELECTRONICS, INC. AND SUBSIDIARIES Consolidated Financial Statements With Independent Auditors’ Review Report For the Three Months Ended March 31, 2020 and 2019 Address: No.581 & 581-1, Ruiguang Rd., Neihu District, Taipei, Taiwan Telephone: (02)8797-8588 2 Table of contents Contents Page 1. Cover Page 1 2. Table of Contents 2 3. Independent Auditors’ Review Report 3 4. Consolidated Balance Sheets 4 5. Consolidated Statements of Comprehensive Income 5 6. Consolidated Statements of Changes in Equity 6 7. Consolidated Statements of Cash Flows 7 8. Notes to the Consolidated Financial Statements (1) Company history 8 (2) Approval date and procedures of the consolidated financial 8 statements (3) New standards, amendments and interpretations adopted 8~9 (4) Summary of significant accounting policies 9~16 (5) Significant accounting assumptions and judgments, and major 16~17 sources of estimation uncertainty (6) Explanation of significant accounts 17~56 (7) Related-party transactions 56~58 (8) Pledged assets 59 (9) Commitments and contingencies 59 (10) Losses due to major disasters 59 (11) Subsequent events 59 (12) Other 60 (13) Other disclosures (a) Information on significant transactions 60~61, 62~72 (b) Information on investees 61, 73~78 (c) Information on investment in mainland China 61, 79~81 (d) Major shareholders 61 (14) Segment information 61 3 Independent Auditors’ Review Report To COMPAL ELECTRONICS, INC.: Introduction We have reviewed the accompanying consolidated balance sheets of COMPAL ELECTRONICS, INC. and its subsidiaries (the “Group”) as of March 31, 2020 and 2019, and the related consolidated statements of comprehensive income, changes in equity and cash flows for the three months ended March 31, 2020 and 2019, and notes to the consolidated financial statements, including a summary of significant accounting policies. -

指數etf (2805) 截至 31/01/2014 2805

領航富時亞洲(日本除外)指數ETF (2805) 截至 31/01/2014 2805 成分股數目 669 證券百分比 99.66% 現金及現金等類百分比 0.34% 其他 0.00% 證券名稱 證券代號 交易所 資產淨值百分比 Samsung Electronics Co. Ltd. 005930 XKRX 4.36% Taiwan Semiconductor Manufacturing Co. Ltd. 2330 XTAI 2.82% Tencent Holdings Ltd. 700 XHKG 2.20% AIA Group Ltd. 1299 XHKG 1.91% China Construction Bank Corp. 939 XHKG 1.78% China Mobile Ltd. 941 XHKG 1.69% Industrial & Commercial Bank of China Ltd. 1398 XHKG 1.59% Hyundai Motor Co. 005380 XKRX 1.14% Bank of China Ltd. 3988 XHKG 1.13% Hon Hai Precision Industry Co. Ltd. 2317 XTAI 1.13% Hutchison Whampoa Ltd. 13 XHKG 0.98% Infosys Ltd. INFY XNSE 0.97% CNOOC Ltd. 883 XHKG 0.84% Oversea-Chinese Banking Corp. Ltd. O39 XSES 0.74% Housing Development Finance Corp. HDFC XNSE 0.73% DBS Group Holdings Ltd. D05 XSES 0.72% Reliance Industries Ltd. RELIANCE XNSE 0.72% Galaxy Entertainment Group Ltd. 27 XHKG 0.72% China Life Insurance Co. Ltd. 2628 XHKG 0.71% Singapore Telecommunications Ltd. Z74 XSES 0.70% PetroChina Co. Ltd. 857 XHKG 0.70% POSCO 005490 XKRX 0.69% Shinhan Financial Group Co. Ltd. 055550 XKRX 0.69% Hong Kong Exchanges and Clearing Ltd. 388 XHKG 0.68% China Petroleum & Chemical Corp. 386 XHKG 0.68% Hyundai Mobis 012330 XKRX 0.67% Cheung Kong Holdings Ltd. 1 XHKG 0.66% Sands China Ltd. 1928 XHKG 0.62% Sun Hung Kai Properties Ltd. 16 XHKG 0.62% United Overseas Bank Ltd. U11 XSES 0.62% SK Hynix Inc. -

Listing Changes in 2003

Listing Changes in 2003 Listings Name Code Date Listings Name Code Date Common First Financial Holding Co. Ltd. 2892 2-Jan Compal Communications Inc. 8078 9-Dec Stocks Johnson Health Tech. Co., Ltd. 1736 9-Jan Sitronix Technology Corp. 8016 25-Dec Makalot Industrial Co., Ltd. 1477 21-Jan Formosa Petrochemical Corp 6505 26-Dec KING BILLION ELECTRONICS CO., LTD. 3056 3-Mar Taiwn Chang Type Industrial Co., Ltd. 541 19-Mar Depository FORMOSA EPITAXY INCORPORATION 3061 11-Apr Receipts Mustek Limited 9104 20-Jan MIN AIK TECHNOLOGY CO., LTD. 3060 21-Apr Cal-Comp Electronics(Thailand) Public Co., Ltd. 9105 22-Sep GENERAL PLASTIC INDUSTRIAL CO., LTD. 6128 16-Jun Warrants Gemtek Technology Co., Ltd. 4906 30-Jun CyberTAN Technology, Inc. 3062 28-Jul Yunta Core Pacific-Uni-President Enterprises Corp. Jul. 03 0768 3-Jan SYSAGE THCHNOLOGY CO., LTD. 6112 4-Aug Fubon-Chinatrust Group Jan. 04 0769 6-Jan JYE TAI PRECISION INDUSTRIAL. CO., LTD. 6165 4-Aug Fubon-Sinopac Holdings Jan. 04 0770 8-Jan RECHI PRECISION CO., LTD. 4532 4-Aug Jih Sun-Asustek Jan. 04 0771 9-Jan CAMEO COMMUNICATIONS, INC. 6142 4-Aug China Trust-Fubon Financial Jul. 03 0772 10-Jan TECO ENTERPRISE CO., LTD. 6119 4-Aug Yuanta Core Pacific-Asustek Computer Jul. 03 0773 16-Jan Wistron Corporation 3231 19-Aug Masterlink-Pou Chen Jul. 03 0774 17-Jan SIGURD MICROELECTRONICS CORP. 6257 25-Aug Yuanta Core Pacific-Via Technologies Jul. 03 0775 20-Jan HannStar Board Corp. 5469 25-Aug Sinopac-Siliconware Jul. 03 0777 21-Jan EverFocus Electronics Corp. -

The Electronic Manufacturing Service (EMS) Industry in 2014

The Electronic Manufacturing Service Ericsson, routers for Cisco, and printers for HP. Cal- 1 (EMS) Industry in 2014 Comp Electronics (based in Thailand) produces components for HP printers and other products. Celestica (based in Canada, where it was spun off by IBM in 1994), meanwhile, produces sub-assemblies for Cisco’s internet and intranet devices, as well as products for customers such as HP, IBM, and NEC (until 2012, Celestica also was one of the producers of the Blackberry smartphone, for which Foxconn is now taking the lead in design and assembly). Each of these EMS providers has plants around the world, well beyond their home countries. EMS are similar to ODMs (Original Design Manufacturers), with a key difference that EMS providers traditionally did not take ownership of intellectual property, while ODM firms (many of EMS services at Celestica solar panel lab (Canada) which – such as Pegatron, Compal, Wistron, and Photo: Adrian Wyld/Canadian Press Quanta – originated in Taiwan) often retain at least partial IP ownership of the products they design for an OEM. Hence, ODMs historically were stronger at product design capabilities than most EMS providers. However, the line between the two types of service organizations is rapidly blurring and the same companies can act as both ODM and EMS providers. Pegatron, for instance, is one of the EMS producers of the iPhone, while Foxconn has taken on ODM- type responsibility for Blackberry. The boundaries of the EMS market are dynamic, so that measuring market size is ambiguous. However, an estimate by the “Research and Markets” industry analysts is that total electronics assembly exceeded $1 trillion in 2013 and will grow to about $1.5 trillion iPhone assembly at a Foxxcon facility in China in 2017. -

In the United States District Court for the Eastern District of Texas Marshall Division

Case 2:20-cv-00314-JRG Document 1 Filed 09/28/20 Page 1 of 77 PageID #: 1 IN THE UNITED STATES DISTRICT COURT FOR THE EASTERN DISTRICT OF TEXAS MARSHALL DIVISION LIBERTY PATENTS, LLC, CIVIL ACTION NO. 2:20-cv-314 Plaintiff, ORIGINAL COMPLAINT FOR v. PATENT INFRINGEMENT LENOVO GROUP LTD.; LENOVO JURY TRIAL DEMANDED (SHANGHAI) ELECTRONICS TECHNOLOGY CO., LTD.; LENOVO INFORMATION PRODUCTS (SHENZHEN) CO. LTD.; LCFC (HEFEI) ELECTRONICS TECHNOLOGY CO., LTD. D/B/A LC FUTURE CENTER and LENOVO COMPAL FUTURE CENTER; COMPAL ELECTRONICS, INC.; COMPAL INFORMATION TECHNOLOGY (KUNSHAN) CO. LTD. Defendants. ORIGINAL COMPLAINT FOR PATENT INFRINGEMENT Plaintiff Liberty Patents, LLC (“Liberty Patents” or “Plaintiff”) files this original complaint against Defendants Lenovo Group Limited, Lenovo (Shanghai) Electronics Technology Co. Ltd., Lenovo Information Products (Shenzhen) Co. Ltd., LCFC (Hefei) Electronics Technology Co. Ltd. d/b/a LC Future Center and Lenovo Compal Future Center, Compal Electronics, Inc., and Compal Information Technology (Kunshan) Co. Ltd. (collectively “Defendants”), alleging, based on its own knowledge as to itself and its own actions and based on information and belief as to all other matters, as follows: Case 2:20-cv-00314-JRG Document 1 Filed 09/28/20 Page 2 of 77 PageID #: 2 PARTIES 1. Liberty Patents is a limited liability company formed under the laws of the State of Texas, with its principal place of business at 2325 Oak Alley, Tyler, Texas 75703. 2. Defendant Lenovo Group Limited is a company organized under the laws of Hong Kong SAR. Lenovo Group Limited has an office at 23rd Floor, Lincoln House, Taikoo Place, 979 King’s Road, Quarry Bay, Hong Kong SAR, China. -

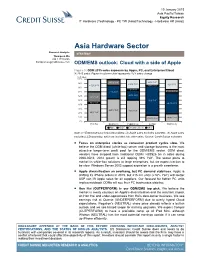

Asia Hardware Sector Research Analysts STRATEGY Thompson Wu 886 2 2715 6386 [email protected] ODM/EMS Outlook: Cloud with a Side of Apple

19 January 2015 Asia Pacific/Taiwan Equity Research IT Hardware (Technology - PC TW (Asia)/Technology - Hardware HK (Asia)) Asia Hardware Sector Research Analysts STRATEGY Thompson Wu 886 2 2715 6386 [email protected] ODM/EMS outlook: Cloud with a side of Apple Figure 1: ODM 2015 sales exposure by Apple, PC, and Enterprise/Cloud % 2015 sales: Figure in column chart represents YoY sales change % of sales 100% --14% YoY +14% YoY +2% YoY 90% +14% YoY +12% YoY +64% YoY +2% YoY 80% -3%YoY 70% +1% YoY +15% YoY -2.5% YoY 60% +8% YoY 50% -1% YoY +0% YoY +0.4% YoY 40% 30% +35% YoY +5% YoY 20% +6% YoY 10% +141% YoY +404% YoY 0% Hon Hai Quanta (1) Pegatron (2) Compal Wistron (3) Apple NB/DT Enterprise/Cloud Other Note: (1) Enterprise/Cloud excludes tablets; (2) Apple sales excludes Casetek); (3) Apple sales excludes LCD assembly, which we included into other sales. Source: Credit Suisse estimates ■ Focus on enterprise stories as consumer product cycles slow. We believe the ODM direct (white-box) server and storage business is the most attractive longer-term profit pool for the ODM/EMS sector. ODM direct vendors have stripped from traditional OEMs >US$26 bn in sales during 2008-3Q14; 2014 growth is still topping 39% YoY. The sector plans to market its white-box solutions to large enterprises, but we expect traction to be slow. Windows Server 2003 support expiration is a growth sweetener. ■ Apple diversification an overhang, but PC demand stabilises. Apple is shifting its iPhone orders in 2015, but 215 mn units (+16% YoY) with better ASP can lift Apple sales for all suppliers. -

Developments in Advanced Packaging Lead to a New

Vol. 1, No. 1 April 2017 Developments in Advanced Packaging Lead to a New Generation of Suppliers Preliminary OSAT Market Shares, 2016 We are witnessing a trend toward Because these methods of flip chip TAM = $27.7 billion modularization of subsystems for mounting are directly compatible with smartphones, which will, no doubt, surface-mount technology, the assembly ASE spill over to other digital product process now uses both dedicated flip 19.2% Amkor categories as well. Given demand for chip bonders and integrated SMT SPIL thinner and lighter form factors, OEMs placement platforms that combine die- 36.1% JCET increasingly require design flexibility bonding and chip-mounting functions. PTI ChipMOS and faster time to market, as well as This combined IC packaging and 14.0% more flexible and integrated assembly SMT workflow is being used in the Chipbond processes that lower costs. production of FCIP-related SiPs, THT Tongfu Apple is just one of the brands including DRAM and MEMS, as well Carsem 1.2% 9.4% aggressively looking to embrace such as embedded devices. Therefore, Others 2.4% modularization. By increasing the advanced PCB assembly technology is 5.7% 2.8% 2%5.3% number of SiP modules per device, moving upstream into the IC packaging 1.9% important efficiency gains can be world with mixed interconnect Source: NVR made. The same goes for further technologies that address converging component integration into flexible and increasingly modularized SMT and Increasingly, OEMs/IDMs like Apple and circuit assembly, embedded antennas, microelectronics assemblies. Samsung work directly with foundries and etc. Meanwhile, a new generation of Clearly, digital applications, OSATs to reach a higher level of integration module manufacturers is emerging to particularly smartphones and wearables, between wafer, package, and substrate. -

FTSE Publications

2 FTSE Russell Publications 28 October 2020 FTSE Taiwan USD Net Tax Index Indicative Index Weight Data as at Closing on 27 October 2020 Constituent Index weight (%) Country Constituent Index weight (%) Country Constituent Index weight (%) Country Accton Technology 0.45 TAIWAN Formosa Petrochemical 0.44 TAIWAN SinoPac Financial Holdings Co. Ltd. 0.45 TAIWAN Acer 0.29 TAIWAN Formosa Plastics Corp 1.56 TAIWAN Synnex Technology International 0.23 TAIWAN Advantech 0.49 TAIWAN Formosa Taffeta 0.13 TAIWAN Taishin Financial Holdings 0.53 TAIWAN Airtac International Group 0.42 TAIWAN Foxconn Technology 0.23 TAIWAN Taiwan Business Bank 0.19 TAIWAN ASE Technology Holding 0.87 TAIWAN Fubon Financial Holdings 1.21 TAIWAN Taiwan Cement 0.82 TAIWAN Asia Cement 0.38 TAIWAN Genius Electronic Optical 0.2 TAIWAN Taiwan Cooperative Financial Holding 0.75 TAIWAN ASMedia Technology 0.24 TAIWAN Giant Manufacturing 0.31 TAIWAN Taiwan Fertilizer 0.15 TAIWAN Asustek Computer Inc 0.7 TAIWAN GlobalWafers 0.36 TAIWAN Taiwan Glass Industrial 0.08 TAIWAN AU Optronics 0.42 TAIWAN HIWIN Technologies Corp. 0.29 TAIWAN Taiwan High Speed Rail 0.26 TAIWAN Capital Securities 0.09 TAIWAN Hon Hai Precision Industry 3.82 TAIWAN Taiwan Mobile 0.64 TAIWAN Catcher Technology 0.54 TAIWAN Hotai Motor 0.81 TAIWAN Taiwan Secom 0.1 TAIWAN Cathay Financial Holding 1.28 TAIWAN HTC Corporation 0.08 TAIWAN Taiwan Semiconductor Manufacturing 42.94 TAIWAN Chailease Holding 0.73 TAIWAN Hua Nan Financial Holdings 0.67 TAIWAN TECO Electric & Machinery 0.21 TAIWAN Chang Hwa Commercial Bank 0.45 TAIWAN Innolux 0.34 TAIWAN TPK Holding Co Ltd 0.07 TAIWAN Cheng Shin Rubber Industry 0.27 TAIWAN Inventec Co. -

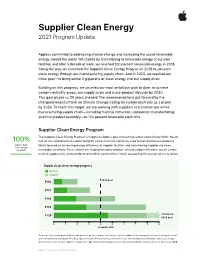

Supplier Clean Energy 2021 Program Update FINAL

Supplier Clean Energy 2021 Program Update Apple is committed to addressing climate change and increasing the use of renewable energy around the world. We started by transitioning to renewable energy at our own facilities and after a decade of work, we reached 100 percent renewable energy in 2018. Along the way, we launched the Supplier Clean Energy Program in 2015 to advance clean energy through our manufacturing supply chain. And in 2020, we reached our initial goal—to bring online 4 gigawatts of clean energy into our supply chain. Building on this progress, we unveiled our most ambitious plan to date: to achieve carbon neutrality across our supply chain and in our product lifecycle by 2030. This goal places us 20 years ahead of the recommendations put forward by the Intergovernmental Panel on Climate Change calling for carbon neutrality as a planet by 2050. To reach this target, we are working with suppliers to transition our entire manufacturing supply chain—including material extraction, component manufacturing, and final product assembly—to 100 percent renewable electricity. Supplier Clean Energy Program The Supplier Clean Energy Program is integral to Apple’s goal of reaching carbon neutrality by 2030. Nearly 100% half of our comprehensive carbon footprint comes from the electricity used to manufacture our products. supply chain We’re focused on increasing energy efficiency at supplier facilities and transitioning suppliers to clean, clean energy by 2030 renewable electricity. These efforts are helping to reduce product-related carbon emissions, create a more resilient supply chain, and contribute to healthier communities—while also paving the way for others to follow.