Cyrus Plus Technical Reference Manual 1.1.1 2/36

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Amigaone-XE Motherboard User Manual

AmigaOne-XE Motherboard User Manual PowerPC™ for Amiga OS4 & Linux April 2003 Revision 1.1 Mai Logic Incorporated & Eyetech Group Ltd Contents 1 Introduction...................................................................................................4 2 Features.........................................................................................................5 3 CPU Module card ..........................................................................................6 4 AmigaOne-XE Board Layout.....................................................................7 4.1 BACK PANEL CONNECTORS .......................................................................................8 4.2 HARD DISK, FLOPPY AND ADD ON CARD CONNECTORS ..............................................8 4.3 JUMPER AND SWITCH SETTING ON AmigaOne-XE.............................................................9 4.3.1 Jumpers and their default setting............................................................................... 9 4.3.2 Connectors and Switches ........................................................................................ 11 5 Appendix......................................................................................................15 Figure Index Figure 3-1 CPU Module Card .................................................................................................................................................6 Figure 4-1 AmigaOne-XE Board Layout .................................................................................................................................7 -

Amiga NG Nr 0

Amiga.org.pl komputer Amiga współcześnie Spis treści AMIGA legenda informatyki 2 Retro 4 Emulacja 6 Współczesna Amiga nowej generacji 11 MorphOS 17 AROS 24 Amiga dzisiaj Zainteresowanie komputerem Amiga jest nieprzemijające. Niezależnie od tych, którzy mają Amigę “od zawsze”, biegnie współcześnie jej nieprzerwany rozwój, i to wielotorowo. Oprócz tego możemy cieszyć się różnymi hobbystycznymi rozwinięciami, pozwalającymi w sposób bardziej wygodny korzystać z rozrywki w formie retro. Amiga dzisiaj to “amigowanie”, wielka różnorodność i wiele smaków 1 Amiga retro AMIGA legenda informatyki AMIGA - pierwszy na świecie komputer multimedialny. Premiera w 1985 r. Wcześniej były inne innowacyjne konstrukcje (np. firmy Xerox czy Lisa firmy Apple) ale to Amiga wnosiła fenomenalną na ówczesne czasy grafikę, animację i dźwięk. Architektura komputera to specjalizowane układy odciążające procesor. artyści Andy Warhole i Debby Harry przy pierwszej Amidze Rewelacją był też wielozadaniowy system operacyjny. Prasa branżowa potraktowała wtedy Amigę jako zabawkę, nie wiadomo było co z tym robić. Ten pierwszy model nazywał się po prostu Amiga, potem nazywano go Amiga 1000. Projekt wraz z zespołem który go stworzył, z genialnym Jayem Minerem na czele, trafił pod skrzydła CBM (Commodore Business Machines), giganta w tamtym okresie jeśli chodzi o produkcję komputerów na świecie. Kolejne modele pojawiły się 2 lata później – dopiero one odniosły sukces. Amiga 2000 i Amiga 500, oparte na podobnych podzespołach, okienkowy graficzny interfejs – Workbench jednocześnie rozdzieliły pierwotną koncepcję na dwie linie komputerów – “duże” i “małe” Amigi. 2 Amiga retro “Duże” Amigi przypominały PC, były to desktopy, umożliwiające rozbudowę za pomocą kart rozszerzeń. Za sprawą rozszerzenia Video Toaster stały się na jakiś czas standardem w edycji wideo. -

Will You Boot Haiku, on a Non Intel Platform, No BIOS Winter?

Will you boot Haiku, on a non intel platform, no BIOS winter? Booting Haiku on non-x86, a never-ending story. François Revol [email protected] Haiku? ● Free Software Operating System ● Inspired by the BeOS ● Our own kernel ● Our on GUI BeOS: Always on the run ● Hobbit BeBox prototype… – AT&T EOLed Hobbit in 1994 ● PPC BeBox (2 ✕ 603e) – Be stopped making hardware ● PPC Mac (pre-G3) – Then Steve said “you won’t get the specs” ● Intel PC – “He Who Controls the Bootloader” (2001) Jean-Louis Gassée quote “I once preached peaceful coexistence with Windows. You may laugh at my expense -- I deserve it.” Booting on PC ● BIOS → MBR {Bootman,GRUB chainload} ● MBR→ partition boot sector (stage1) – Needs partition offset (makebootable) ● Shouldn’t be required ● stage1→ haiku_loader ● haiku_loader → kernel_x86 haiku_loader ● Now in haiku_loader.hpkg (uncompressed) ● Sets graphics mode (for boot splash) ● Loads kernel, modules… from BFS – … or initrd-like tar.gz ● Sets up MMU, FPU… ● And calls the BIOS for many things… ● Calls the kernel with struct *kernel_args – Which contains platform_args and arch_args Challenges ● Since R1/beta1: Packaging – Almost reproducible build – But requires strict dependencies ● Haiku needs Haiku to build – Easy on x86 ● Bootstrap builds = easy to break ● C++ everywhere – C++ issue currently on ARM bootstrap PowerPC ● Started long long ago… – Pegasos 1 … buggy OF ● (some years passed) ● Sam460ex & other AmigaOS-compatibles – U-Boot (heavily modded) ● QEMU Mac PPC always had issues ● BeBox – Very dumb bootrom; needs PEF binary OpenFirmware ● Nice, even cleaner than BIOS ● Except for ACPI-like things – Clean power-off = keep OF mappings – Maybe use an emulator? ● We do this for VESA BIOS already ● Standardized bindings ● Framebuffer calls too high-level – Get phys addr? AmigaOne X-1000 ● You read the specs. -

CCN - Java Opensource Kit Emulator for Wireless Ad Hoc Networks

CCN - Java Opensource Kit EmulatoR for Wireless Ad Hoc Networks Ilaria Cianci, L. Alfredo Grieco, and Gennaro Boggia DEE - Politecnico di Bari Italy {i.cianci,a.grieco,g.boggia}@poliba.it ABSTRACT Despite the uncontested success of Internet, the way the The information centric paradigm assumes that the Future network is used is changed: information itself has become Internet will be built around contents rather than host lo- more and more important in all aspects of communication. cations. In this direction, the promising Content Centric In fact, most of the today Internet traffic is related to content Networking (CCN) architecture has been conceived to solve distribution, which includes file sharing, media streaming, the problems of the today Internet by means of a novel and so on. This information-centric use of the worldwide way for distributing contents (based on their names) and by network raises new challenges, many of them not being han- adopting distributed caching mechanisms. CCN can be par- dled effectively by the current network architecture [1]. For ticularly beneficial in an ad hoc networking environments, this reason, many research groups all over the world are dis- where the main goal is the delivery of data to a given des- cussing about the big topic of the Future Internet, which has tination node no matter its position, and moreover, in sce- to meet the requirements of scalability, heterogeneity, secu- narios characterized by limited connectivity, just as wireless rity, mobility, QoS, robustness, energy efficiency, economic ad hoc networks. Some interesting works, available in liter- incentives, and so on [13]. -

Amigaos4 Download

Amigaos4 download click here to download Read more, Desktop Publishing with PageStream. PageStream is a creative and feature-rich desktop publishing/page layout program available for AmigaOS. Read more, AmigaOS Application Development. Download the Software Development Kit now and start developing native applications for AmigaOS. Read more.Where to buy · Supported hardware · Features · SDK. Simple DirectMedia Layer port for AmigaOS 4. This is a port of SDL for AmigaOS 4. Some parts were recycled from older SDL port for AmigaOS 4, such as audio and joystick code. Download it here: www.doorway.ru Thank you James! 19 May , In case you haven't noticed yet. It's possible to upload files to OS4Depot using anonymous FTP. You can read up on how to upload and create the required readme file on this page. 02 Apr , To everyone downloading the Diablo 3 archive, April Fools on. File download command line utility: http, https and ftp. Arguments: URL/A,DEST=DESTINATION=TARGET/K,PORT/N,QUIET/S,USER/K,PASSWORD/K,LIST/S,NOSIZE/S,OVERWRITE/S. URL = Download address DEST = File name / Destination directory PORT = Internet port number QUIET = Do not display progress bar. AmigaOS 4 is a line of Amiga operating systems which runs on PowerPC microprocessors. It is mainly based on AmigaOS source code developed by Commodore, and partially on version developed by Haage & Partner. "The Final Update" (for OS version ) was released on 24 December (originally released Latest release: Final Edition Update 1 / De. Purchasers get a serial number inside their box or by email to register their purchase at our website in order to get access to our restricted download area for the game archive, the The game was originally released in for AmigaOS 68k/WarpOS and in December for AmigaOS 4 by Hyperion Entertainment CVBA. -

The Pegasos Book « Le Livre Du Pegasos » Compilation of Articles on the Pegasos Volume 4 : Linux, Macosx and Other Systems

The Pegasos book « Le livre du Pegasos » Compilation of articles on the Pegasos Volume 4 : Linux, MacOSX and other systems May 2007 edition - By Geoffrey CHARRA (V2.3) Translated from french by Geoffrey CHARRA (December 2007), With the help of Eric WALTER, Thibault JEANSON, Denis HILLIARD (translation) and Fulvio PERUGGI (corrections) Sponsored by The Pegasos book – Volume 4 : Linux, MacOSX and other systems Contents 1 Linux ......................................................................................................................... 4 1.1 Global information ................................................................................................. 4 1.1.1 Linux distributions running on Pegasos ............................................................... 4 1.1.2 General information on Linux usage for beginners ............................................... 5 1.1.3 Hard disk partitioning under Linux on Pegasos .................................................... 5 1.1.4 Multi-boot with bootcreator .............................................................................. 7 1.1.5 Using a Linux System from Another Linux System by Changing root ...................... 8 1.1.6 NFS : Network File System and Remote Compiling .............................................. 8 1.2 Installation of Linux Debian on Pegasos I and II ...................................................... 10 1.2.1 Installation types ........................................................................................... 10 1.2.2 Installation -

Amigaone-XE G4 We Preview the Fastest Powerpc Motherboard in Eyetech’S Range

Issue 16, Autumn 2003 £4.00 8.00Euro Find out all about this feature-packed Zorro card inside. AmigaOne-XE G4 We preview the fastest PowerPC motherboard in Eyetech’s range. Improve your digital photos and scans with our image enhancement tutorial. Contents News PageStream Issue 16 EditorialChandler’s Amiga OS 4 Update for Amiga OS 4 Autumn 2003 elcome to another on page 10. This time he Grasshopper LLC has display. Hopefully this feature Wbumper 52-page edition reports some interesting announced that they will may be added to the new of Total Amiga! As I write this developments relating to support AmigaOS 4 with a new Amiga version too. The Contents the production of this issue has developing programs for OS 4 version of their professional standard retail price of the full gone very smoothly and it and some changes in priority DTP package, PageStream 4. version of PageStream has looks like it will be out on time. that should mean the As regular readers will know, been reduced to just $99 News This has largely been made AmigaOne version is available Editorial ..............................2 PageStream is a powerful (approximately £65) making it possible by all the people who earlier than would otherwise finding software currently in program and, I think most much more affordable. There is News Items ........................3 contributed to this issue, as have been possible. This development so we thought it people will agree, one of best also a new professional edition Amiga OS 4 Update........ 10 you will see there are several should please Mick and would be worth reviewing. -

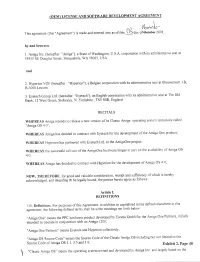

License and Software Development Agreement \

(OEM) LICENSE AND SOFTWARE DEVELOPMENT AGREEMENT \ ... N9rPW\~vC'~ This agreement (this "Agreement") is made and entered into as ofthis ()~ day ofOsleesr 2001, by and between: I. Amiga Inc (hereafter "Amiga"), a State of Washington, U.S.A corporation with its administrative seat at 34935 SE Douglas Street, Snoqualmie, WA 98065, USA and 2. Hyperion VOF (hereafter: "Hyperion"), a Belgian corporation with its administrative seat at Brouwersstr. lB, B-3000 Leuven; 3. Eyetech Group Ltd. (hereafter. "Eyetech"), an English corporation with its administrative seat at The Old Bank, 12 West Green, Stokesley, N. Yorkshire, TS9 5BB, England. RECITALS WHEREAS Amiga intends to release a new version ofits Classic Amiga operating system tentatively called "Amiga OS 40"; WHEREAS Amiga has decided to contract with Eyetech for the development ofthe Amiga One product, WHEREAS Hyperion has partnered with Eyetech Ltd. in the AmigaOne project; WHEREAS the successful roll-out ofthe AmigaOne hardware hinges in part on the availability of Amiga OS 40: WHEREAS Amiga has decided to contract with Hyperion for the development of Amiga OS 40; NOW, THEREFORE, for good and valuable consideration, receipt and sufficiency of which is hereby acknowledged, and intending tb be legally bound, the parties hereto agree as follows: Article 1. DEFINITIONS 1.01 Definitions For purposes ofthis Agreement, in addition to capitalized terms defined elsewhere in this agreement, the following defined terms shall have the meanings set forth below: "Amiga One" means the PPC hardware product developed by Escena Gmbh for the Amiga One Partners, initially intended to operate in conjunction with an Amiga 1200; "Amiga One Partners" means Eyetech and Hyperion collectively; "Amiga OS Source Code" means the Source Code ofthe Classic Amiga OS including but not limited to the Source Code of Amiga OS 3. -

Workbench November 2002 Issue 186 Microsoft & Amiga Join Forces !!

Workbench November 2002 Issue 186 Microsoft & Amiga Join Forces !! Previously thought of as a match that would never happen, Microsoft and Amiga Inc. have become partners in distributing Amiga DE applications. “Amiga has partnered with Microsoft to create the best experience for gamers and entertainment on Smartphone devices”, said Bill McEwen, CEO of Amiga. “We have been an early adopter of Microsoft Windows for Smartphones because of our belief it can revolutionize the mobile experience. With our new App Pak technology, users can access applications on their PDA or Smartphone without having to install them from their personal computer.” Microsoft will work to distribute Amiga Inc. DE applications through Microsoft’s sale channels, with all proceeds going to both Amiga Inc. and DE developers directly. The target market will be Windows enabled smartphones and PDA’s (personal digital assistants). At the moment PDA’s are priced more to the business user but new powerful models with 64 megabytes of memory are on the horizon. These new models will have a more “Gameboy Advance” type retail pricing and thus should be more readily taken up by consumers. Plus the power of the new models will enable more complex software ideally suited to the Amiga DE. Microsoft execs were shocked and amazed at an Amiga DE demo performed by Amiga Inc. CEO Bill McEwen. Microsoft and their partners had never envisioned such a thing possible as a high quality “App Pak” that can simply be plugged into a PDA or Smartphone. All their previous efforts were centered around downloading software from a CD in a PC and that was the best they could achieve. -

Download Issue 14

IssueBiggest Ever! £4.00 Issue 14, Spring 2003 8.00Euro Quake 2 Read our comprehensive review of Hyperions’s latest port. Hollywood Take a seat and enjoy our full review of this exciting new multimedia blockbuster! Contents Features The Show Must Go On! Editorial Welcome to another issue of Candy for SEAL’s Mick Sutton gives us an insight into the production of WoASE. Total Amiga, as you will no-doubt Issue 14 usergroups can afford. To give balance between space for the have noticed this issue is rather ack in the good old days we you an idea a venue capable of punters and giving the exhibitors late, which is a pity as we had Candy Factory is a graphics A built-in character generator had World of Amiga shows holding between 300 and 500 the stand space they require improved our punctuality over OS4 B the last few issues. application designed for allows you to add effects to Spring 2002 put on every year, usually at a people can cost anywhere from (some companies get a real bee high profile site (Wembley) and £500 to £1000 (outside London) in their bonnet about where they Unfortunately the main reason making logos and other text in any font without leaving texture again based on the all well attended. Everybody for a day. are situated). The floorplan goes behind the delay was that the graphics with high quality 3D the program. You can also load Contents wanted to be there and be seen, through many revisions before SCSI controller and PPC on my textured effects quickly and shapes (for example a logo) light source. -

Frequently Asked Questions on It.Comp.Os.Amiga

Frequently Asked Questions on it.comp.os.amiga rev. 1.5.1 - 17 marzo 2005 A cura di Varthall ([email protected]) (Per scrivere un'email, rimuovere dall'indirizzo soprastante la stringa bongo.) L'ultima versione della presente FAQ e' disponibile su: www.icoa.tk e sul newsgroup it.faq. Visti i numerosi e reiterati quesiti a proposito di Amiga che appaiono periodicamente su questo ng, si e' pensato di rispondere alle piu' comuni domande. A questo proposito, al fine di evitare inutile "rumore", suggerirei di EVITARE di rispondere alle gia' citate domande se non con un rimando alla FAQ stessa. Precisazioni e/o ampliamenti sono sempre ben accetti (mi riservo di modificare leggermente i testi forniti per omogeneita' stilistica). Al fine di accelerare i tempi e' preferibile inviare testo preformattato a 78 colonne con codifica ASCII a 7 bit, e naturalmente dopo che l'autore abbia verificato l'esattezza di cio' che scrive. In particolare si ringraziano: - Andrea Mansella ([email protected]), curatore delle precedenti versioni di questa faq - Shinkuro ([email protected]) - Gabriele Greco ([email protected]) - Andrea Maniero ([email protected]) - Zaxxon ([email protected]) - Angelo 'Eddy' Celentano - Paolo Besser e tutti quelli che hanno contribuito alle precedenti revisioni della faq: - Demis Gallisto ([email protected]) - Fabio Benedetti ([email protected]) - Daniele Gratteri ([email protected]) - Antonio Mule' ([email protected]) - Giorgio Signori ([email protected]) - Marco -

Workbench Oct'08 16 Pgs.PGS

Workbench October 2008 Issue 255 WE’REWE’RE STILLSTILL HERE!HERE! HAPPYHAPPY HALLOWEENHALLOWEEN October 2008 Workbench 1 Editorial Hi Folks, I’m ba-a-a-ck! And I’ll start out with the not so good news. Editor First and foremost, very few of our members have paid their Barry Woodfield Phone:9917 2967 annual membership fees for the next year yet, unfortunately. Mobile : 0448 915 283 And also Tony Mulvihill is giving up his Amiga gear due to lack of time [email protected] ibutions from work pressures. Contributions can be soft copy (on floppy½ disk) or Better news is AmiKit has been updated hard copy. It will be returned again. (Check out the AmiNews pages) if requested and accompanied with a self- Well, that’s about it for this month. addressed envelope. The editor of the Amiga Users Group Inc. newsletter Happy Amiga Halloween -ing. Ciao for now, Workbench retains the right to edit contributions for Barry R. Woodfield. clarity and length. Send contributions to: Amiga Users Group P.O. Box 2097 Seaford Victoria 3198 OR [email protected] rtising Advertising space is free for members to sell private items or services. For information on commercial rates, contact: Tony Mulvihill 0415 161 2721 [email protected] Deadlines Last Months Meeting Workbench is published each month. The deadline for each September 21st 2008 issue is the 1st Tuesday of the month of publication. Reprints All articles in Workbench are Copyright 2008 the This Months Meeting Amiga Users Group Inc. unless otherwise indicated. October 19th 2008 Articles may be reproduced for noncommercial purposes if accompanied by a credit line including the original authors name and the words: Next Months Meeting Reprinted from Workbench ADUG Memberships the newsletter of the Amiga November 16th 2008 The Amiga Downunder Users Group.