Arm Cortex M7 Technical Reference Manual

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Nios II Custom Instruction User Guide

Nios II Custom Instruction User Guide Subscribe UG-20286 | 2020.04.27 Send Feedback Latest document on the web: PDF | HTML Contents Contents 1. Nios II Custom Instruction Overview..............................................................................4 1.1. Custom Instruction Implementation......................................................................... 4 1.1.1. Custom Instruction Hardware Implementation............................................... 5 1.1.2. Custom Instruction Software Implementation................................................ 6 2. Custom Instruction Hardware Interface......................................................................... 7 2.1. Custom Instruction Types....................................................................................... 7 2.1.1. Combinational Custom Instructions.............................................................. 8 2.1.2. Multicycle Custom Instructions...................................................................10 2.1.3. Extended Custom Instructions................................................................... 11 2.1.4. Internal Register File Custom Instructions................................................... 13 2.1.5. External Interface Custom Instructions....................................................... 15 3. Custom Instruction Software Interface.........................................................................16 3.1. Custom Instruction Software Examples................................................................... 16 -

Intel Quartus Prime Pro Edition User Guide: Programmer Send Feedback

Intel® Quartus® Prime Pro Edition User Guide Programmer Updated for Intel® Quartus® Prime Design Suite: 21.2 Subscribe UG-20134 | 2021.07.21 Send Feedback Latest document on the web: PDF | HTML Contents Contents 1. Intel® Quartus® Prime Programmer User Guide..............................................................4 1.1. Generating Primary Device Programming Files........................................................... 5 1.2. Generating Secondary Programming Files................................................................. 6 1.2.1. Generating Secondary Programming Files (Programming File Generator)........... 7 1.2.2. Generating Secondary Programming Files (Convert Programming File Dialog Box)............................................................................................. 11 1.3. Enabling Bitstream Security for Intel Stratix 10 Devices............................................ 18 1.3.1. Enabling Bitstream Authentication (Programming File Generator)................... 19 1.3.2. Specifying Additional Physical Security Settings (Programming File Generator).............................................................................................. 21 1.3.3. Enabling Bitstream Encryption (Programming File Generator).........................22 1.4. Enabling Bitstream Encryption or Compression for Intel Arria 10 and Intel Cyclone 10 GX Devices.................................................................................................. 23 1.5. Generating Programming Files for Partial Reconfiguration......................................... -

Introduction to Intel® FPGA IP Cores

Introduction to Intel® FPGA IP Cores Updated for Intel® Quartus® Prime Design Suite: 20.3 Subscribe UG-01056 | 2020.11.09 Send Feedback Latest document on the web: PDF | HTML Contents Contents 1. Introduction to Intel® FPGA IP Cores..............................................................................3 1.1. IP Catalog and Parameter Editor.............................................................................. 4 1.1.1. The Parameter Editor................................................................................. 5 1.2. Installing and Licensing Intel FPGA IP Cores.............................................................. 5 1.2.1. Intel FPGA IP Evaluation Mode.....................................................................6 1.2.2. Checking the IP License Status.................................................................... 8 1.2.3. Intel FPGA IP Versioning............................................................................. 9 1.2.4. Adding IP to IP Catalog...............................................................................9 1.3. Best Practices for Intel FPGA IP..............................................................................10 1.4. IP General Settings.............................................................................................. 11 1.5. Generating IP Cores (Intel Quartus Prime Pro Edition)...............................................12 1.5.1. IP Core Generation Output (Intel Quartus Prime Pro Edition)..........................13 1.5.2. Scripting IP Core Generation.................................................................... -

Technical Competencies and Professional Skills

TECHNICAL COMPETENCIES AND PROFESSIONAL SKILLS Applied Mathematics Technical Skills: data visualization and analysis, SQL, finance and accounting Programming Languages: R, MATLAB, C++, Java, Python Markup Languages: LaTeX, HTML, CSS Software: Microsoft Office (Excel, Office, Word), XCode, Visual Studio Note: Skills, software, and languages are dependent on elective taken, computer selection, and class year. Applied Sciences Instrumentation: UV/Vis spectroscopy, NMR spectroscopy, IR spectroscopy, GC-MS, LC-MS, thermocycler, nucleic acid sequencer, microplate reader, cryocooler Lab Techniques: Gel electrophoresis and SDS-PAGE, Western blotting, primer design and Polymerase Chain Reaction (PCR), QPCR, sterile lab technique, cell culture, nucleic acid isolation and purification, protein isolation and purification (chromatography, centrifugation, dialysis), enzyme thermodynamics and kinetics, transfection and transformation, chemical synthesis and purification (distillation, extraction, chromatography, rotary evaporator, crystallization), inert atmosphere and Schlenk line techniques, titration, dissection of preserved specimens, four-probe electrical measurement, Bragg diffraction Competencies: Application of the scientific method, Scientific writing and oral communication Software and computational skills: Microsoft Office (Word, Excel, Powerpoint), ChemDraw, PyMol, TopSpin, Java, Protein DataBank (PDB), NCBI suite (including BLAST, GenBank), Orca Quantum Chemistry software, LoggerPro, LabView Architecture Design Skills: Multi-scale civic -

Formal Hardware Specification Languages for Protocol Compliance Verification

Formal Hardware Specification Languages for Protocol Compliance Verification ANNETTE BUNKER and GANESH GOPALAKRISHNAN University of Utah and SALLY A. MCKEE Cornell University The advent of the system-on-chip and intellectual property hardware design paradigms makes pro- tocol compliance verification increasingly important to the success of a project. One of the central tools in any verification project is the modeling language, and we survey the field of candidate languages for protocol compliance verification, limiting our discussion to languages originally in- tended for hardware and software design and verification activities. We frame our comparison by first constructing a taxonomy of these languages, and then by discussing the applicability of each approach to the compliance verification problem. Each discussion includes a summary of the devel- opment of the language, an evaluation of the language’s utility for our problem domain, and, where feasible, an example of how the language might be used to specify hardware protocols. Finally, we make some general observations regarding the languages considered. Categories and Subject Descriptors: B.4.3 [Input/Output and Data Communications]: Inter- connections (Subsystems)—Interfaces; B.4.5 [Input/Output and Data Communications]: Reli- ability, Testing, and Fault-Tolerance—Hardware reliability; B.7.2 [Integrated Circuits]: Design aids—Verification; C.2.2 [Computer-Communication Networks]: Network Protocols—Protocol verification; D.3.3 [Programming Languages]: Language Constructs and Features—Data types -

Intel® Arria® 10 Device Overview

Intel® Arria® 10 Device Overview Subscribe A10-OVERVIEW | 2020.10.20 Send Feedback Latest document on the web: PDF | HTML Contents Contents Intel® Arria® 10 Device Overview....................................................................................... 3 Key Advantages of Intel Arria 10 Devices........................................................................ 4 Summary of Intel Arria 10 Features................................................................................4 Intel Arria 10 Device Variants and Packages.....................................................................7 Intel Arria 10 GX.................................................................................................7 Intel Arria 10 GT............................................................................................... 11 Intel Arria 10 SX............................................................................................... 14 I/O Vertical Migration for Intel Arria 10 Devices.............................................................. 17 Adaptive Logic Module................................................................................................ 17 Variable-Precision DSP Block........................................................................................18 Embedded Memory Blocks........................................................................................... 20 Types of Embedded Memory............................................................................... 21 Embedded Memory Capacity in -

Openpiton: an Open Source Manycore Research Framework

OpenPiton: An Open Source Manycore Research Framework Jonathan Balkind Michael McKeown Yaosheng Fu Tri Nguyen Yanqi Zhou Alexey Lavrov Mohammad Shahrad Adi Fuchs Samuel Payne ∗ Xiaohua Liang Matthew Matl David Wentzlaff Princeton University fjbalkind,mmckeown,yfu,trin,yanqiz,alavrov,mshahrad,[email protected], [email protected], fxiaohua,mmatl,[email protected] Abstract chipset Industry is building larger, more complex, manycore proces- sors on the back of strong institutional knowledge, but aca- demic projects face difficulties in replicating that scale. To Tile alleviate these difficulties and to develop and share knowl- edge, the community needs open architecture frameworks for simulation, synthesis, and software exploration which Chip support extensibility, scalability, and configurability, along- side an established base of verification tools and supported software. In this paper we present OpenPiton, an open source framework for building scalable architecture research proto- types from 1 core to 500 million cores. OpenPiton is the world’s first open source, general-purpose, multithreaded manycore processor and framework. OpenPiton leverages the industry hardened OpenSPARC T1 core with modifica- Figure 1: OpenPiton Architecture. Multiple manycore chips tions and builds upon it with a scratch-built, scalable uncore are connected together with chipset logic and networks to creating a flexible, modern manycore design. In addition, build large scalable manycore systems. OpenPiton’s cache OpenPiton provides synthesis and backend scripts for ASIC coherence protocol extends off chip. and FPGA to enable other researchers to bring their designs to implementation. OpenPiton provides a complete verifica- tion infrastructure of over 8000 tests, is supported by mature software tools, runs full-stack multiuser Debian Linux, and has been widespread across the industry with manycore pro- is written in industry standard Verilog. -

NESS Esk a 2005.0034090 a 22005 Sato Et

US007 185309B1 (12) United States Patent (10) Patent No.: US 7,185,309 B1 Kulkarni et al. (45) Date of Patent: Feb. 27, 2007 (54) METHOD AND APPARATUS FOR 2004/0006584 A1 1/2004 Vandeweerd APPLICATION-SPECIFIC PROGRAMMABLE 2004/O128120 A1 7/2004 Coburn et al. NESS Esk A 2005.00340902005/0114593 A1A 220055/2005 SatoCassell et al.et al. (75) Inventors: Chidamber R. Kulkarni, San Jose, CA 2005/0172085 A1 8/2005 Klingman (US); Gordon J. Brebner, Monte 2005/0172087 A1 8/2005 Klingman Sereno, CA (US); Eric R. Keller, 2005/0172088 A1 8/2005 Klingman Boulder, CO (US); Philip B. 2005/0172089 A1 8/2005 Klingman James-Roxby, Longmont, CO (US) 2005/0172090 A1 8/2005 Klingman O O 2005/0172289 A1 8/2005 Klingman (73) Assignee: Xilinx, Inc., San Jose, CA (US) 2005/0172290 A1 8/2005 Klingman (*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 (21) Appl. No.: 10/769,591 OTHER PUBLICATIONS (22) Filed: Jan. 30, 2004 U.S. Appl. No. 10/769,330, filed Jan. 30, 2004, James-Roxby et al. (51) Int. Cl. (Continued) G06F 7/50 (2006.01) Primary Examiner Thuan Do (52) U.S. Cl. ............................................. 716/18: 718/2 Assistant Examiner Binh Tat (58) Field of Classification Search .................. 716/18, (74) Attorney, Agent, or Firm—Robert Brush 716/2, 3: 709/217: 71.9/313 See application file for complete search history. (57) ABSTRACT (56) References Cited U.S. PATENT DOCUMENTS Programmable architecture for implementing a message 5,867,180 A * 2/1999 Katayama et al. -

Introduction to Verilog HDL

Introduction to Verilog HDL Jorge Ramírez Corp Application Engineer Synopsys University Courseware Copyright © 2011 Synopsys, Inc. All rights reserved. Developed by: Jorge Ramirez Outline Lexical elements • HDL Verilog Data type representation Structures and Hierarchy • Synthesis Verilog tutorial Operators • Assignments Synthesis coding guidelines Control statements • Verilog - Test bench Task and functions Generate blocks • Fine State Machines • References Synopsys University Courseware Copyright © 2011 Synopsys, Inc. All rights reserved. Developed by: Jorge Ramirez HDL VERILOG Synopsys University Courseware Copyright © 2011 Synopsys, Inc. All rights reserved. Developed by: Jorge Ramirez What is HDL? • Hard & Difficult Language? – No, means Hardware Description Language • High Level Language – To describe the circuits by syntax and sentences – As oppose to circuit described by schematics • Widely used HDLs – Verilog – Similar to C – SystemVerilog – Similar to C++ – VHDL – Similar to PASCAL Synopsys University Courseware Copyright © 2011 Synopsys, Inc. All rights reserved. Developed by: Jorge Ramirez Verilog • Verilog was developed by Gateway Design Automation as a proprietary language for logic simulation in 1984. • Gateway was acquired by Cadence in 1989 • Verilog was made an open standard in 1990 under the control of Open Verilog International. • The language became an IEEE standard in 1995 (IEEE STD 1364) and was updated in 2001 and 2005. Synopsys University Courseware Copyright © 2011 Synopsys, Inc. All rights reserved. Developed by: Jorge Ramirez SystemVerilog • SystemVerilog is the industry's first unified hardware description and verification language • Started with Superlog language to Accellera in 2002 • Verification functionality (base on OpenVera language) came from Synopsys • In 2005 SystemVerilog was adopted as IEEE Standard (1800-2005). The current version is 1800-2009 Synopsys University Courseware Copyright © 2011 Synopsys, Inc. -

Standby Power Management Architecture for Deep- Submicron Systems

Standby Power Management Architecture for Deep- Submicron Systems Michael Alan Sheets Electrical Engineering and Computer Sciences University of California at Berkeley Technical Report No. UCB/EECS-2006-70 http://www.eecs.berkeley.edu/Pubs/TechRpts/2006/EECS-2006-70.html May 19, 2006 Copyright © 2006, by the author(s). All rights reserved. Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission. Standby Power Management Architecture for Deep-Submicron Systems by Michael Alan Sheets B.S.C.E. (Georgia Institute of Technology) 1999 M.S. (University of California, Berkeley) 2003 A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy in Engineering-Electrical Engineering and Computer Sciences in the GRADUATE DIVISION of the UNIVERSITY OF CALIFORNIA, BERKELEY Committee in charge: Professor Jan Rabaey, Chair Professor Robert Brodersen Professor Paul Wright Spring 2006 The dissertation of Michael Alan Sheets is approved: Chair Date Date Date University of California, Berkeley Spring 2006 Standby Power Management Architecture for Deep-Submicron Systems Copyright 2006 by Michael Alan Sheets 1 Abstract Standby Power Management Architecture for Deep-Submicron Systems by Michael Alan Sheets Doctor of Philosophy in Engineering-Electrical Engineering and Computer Sciences University of California, Berkeley Professor Jan Rabaey, Chair In deep-submicron processes a signi¯cant portion of the power budget is lost in standby power due to increasing leakage e®ects. -

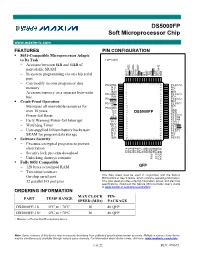

DS5000FP Soft Microprocessor Chip

DS5000FP Soft Microprocessor Chip www.maxim-ic.com FEATURES PIN CONFIGURATION 8051-Compatible Microprocessor Adapts to Its Task TOP VIEW − Accesses between 8kB and 64kB of nonvolatile SRAM LE BD6 PSEN BD5 P2.7/A15 BD4 − In-system programming via on-chip serial BA11 P0.5/AD5 CE2 P0.6/AD6 BA10 P0.7/AD7 CE1 EA N.C. BD7 A port − Can modify its own program or data 80 79 78 77 76 75 74 73 72 71 70 69 68 67 66 65 P0.4/AD4 1 64 P2.6/A14 2 N.C. 63 N.C. memory 3 62 N.C. N.C. BA9 4 61 BD3 − Accesses memory on a separate byte-wide P0.3/AD3 5 60 P2.5/A13 bus BA8 6 59 BD2 P0.2/AD2 7 58 P2.4/A12 Crash-Proof Operation BA13 8 57 BD1 P0.1/AD1 9 56 P2.3/A11 R/W 10 55 BD0 − Maintains all nonvolatile resources for 11 54 P0.0/AD0 VLI VCC0 12 53 GND over 10 years VCC 13 DS5000FP 52 GND 14 51 − Power-fail Reset VCC P2.2/A10 P1.0 15 50 P2.1/A9 BA14 16 49 P2.0/A8 − Early Warning Power-fail Interrupt P1.1 17 48 XTAL1 BA12 18 47 XTAL2 19 − Watchdog Timer P1.2 46 P3.7/RD 20 45 BA7 P3.6/WR − User-supplied lithium battery backs user P1.3 21 44 P3.5/T1 N.C. 22 43 N.C. SRAM for program/data storage N.C. 23 42 N.C. -

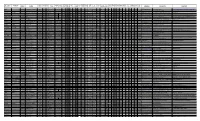

Up Cores T Est Folder Opencores Name Status Author Style / Clone

_uP_cores_t opencores style / data inst repor com LUTs blk F tool MIPS clks/ KIPS src # src tool fltg Ha max max byte # # pipe start last status author FPGA top file doc reference note worthy comments date LUT? est folder name clone size size ter ment ALUT mults ram max ver /clk inst /LUT code files chain pt vd data inst adrs inst reg len year revis cray1 alpha Christopher Fenton cray1 64 16 kintex-7-3 James Brakefield13463 6 19 10 127 ## 14.7 6.00 1.0 56.6 verilog 46 cray_sys_topyes yes Y N 4M 4M N 512 2010 CRAY data sheets homebrew Cray1 www.chrisfenton.com/homebrew-cray-1a/ fpgammix stable Tommy Thorn MMIX 64 32 arria-2 James Brakefield11605 A 8 10 94 ## q13.1 1.50 4.0 3.0 system verilog2 core yes yes Y Y 4G 4G Y 256 288 2006 2008 clone of Knuth's MMIX micro-coded s1_core S1 Core stable Fabrizio Fazzino etal SPARC 64 32 kintex-7-3 James Brakefield52845 6 8 59 56 ## v14.1 2.00 1.0 2.1 verilog 136 s1_top yes yes Y N 4G 4G Y 32 2007 2012 SPARC data sheets reduced version of OpenSPARC T1 Vivado run microblaze proprietaryXilinx uBlaze 32 32 kintex-7 Xilinx 546 6 1 320 1.03 1.0 603.7 not avail yes yes opt 4G 4G Y 86 32 3 2002 www.xilinx.com/tools/microblaze.htmMicroBlaze MCS, smallest configuration70 configuration options, MMU optional ARM_Cortex_A9 ASIC ARM ARM a9 32 16 arria V altera 4500 A 1050 2.50 1.0 583.3 asic yes yes Y 4G 4G Y 80 16 10 2012 altera data sheets uses pro-rated LC area dual issue, includes fltg-pt & MMU & caches nios2 proprietaryAltera Nios II 32 32 stratix-5 Altera 895 A 310 1.13 1.0 389.7 not avail yes yes opt 4G 4G