IRAC Test Report

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

HEATING/COOLING BEVERAGE BASE with WIRELESS CHARGING Item No

HEATING/COOLING BEVERAGE BASE WITH WIRELESS CHARGING Item No. 207196 User Guide Thank you for purchasing the Sharper Image Heating/Cooling Beverage Base with Wireless Charging. Please take a moment to read this guide and store it for future reference. FEATURES • Keeps coffee mug hot or soda can cold • Charges your Qi-enabled phone without cables or wires • Quick charge capable (10W and 7.5W) • Standard charge 5W • Auto sensor supplies the correct power for your device • Automatic safety shut-off after 4 hours (charging) CONTENTS OF BOX • 1X Mug • 1X Base Unit • 1 Power Adapter OPERATION 1. Connect the power adapter to the device. 2. Plug the power adapter into an AC outlet. 3. Place the included mug or your beverage can on top of the heating/cooling element, properly aligning it with the bottom of the container. 4. Press the power button ONCE to activate COOLING. Press a SECOND TIME to activate HEATING. 5. Place your wireless charging device on the charging surface. The Qi wireless charging pad will begin charging automatically. NOTE: There is no On/Off Switch for the wireless charger. Your phone will charge automatically if it is compatible with wireless charging. See the Compatibility list below or consult your device’s owner’s manual to check if your device is Qi enabled for wireless charging. For safety purposes, the Qi wireless charging pad will shut off automatically after 4 hours. - 1 - COMPATIBILITY Qi wireless charging is compatible with most newer phones, including: • Apple iPhone 8, 8 Plus, X, XS, XS Max, XR, 11, 11 Pro, 11 -

Sprint Complete

Sprint Complete Equipment Replacement Insurance Program (ERP) Equipment Service and Repair Service Contract Program (ESRP) Effective July 2021 This device schedule is updated regularly to include new models. Check this document any time your equipment changes and before visiting an authorized repair center for service. If you are not certain of the model of your phone, refer to your original receipt or it may be printed on the white label located under the battery of your device. Repair eligibility is subject to change. Models Eligible for $29 Cracked Screen Repair* Apple Samsung HTC LG • iPhone 5 • iPhone X • GS5 • Note 8 • One M8 • G Flex • G3 Vigor • iPhone 5C • iPhone XS • GS6 • Note 9 • One E8 • G Flex II • G4 • iPhone 5S • iPhone XS Max • GS6 Edge • Note 20 5G • One M9 • G Stylo • G5 • iPhone 6 • iPhone XR • GS6 Edge+ • Note 20 Ultra 5G • One M10 • Stylo 2 • G6 • iPhone 6 Plus • iPhone 11 • GS7 • GS10 • Bolt • Stylo 3 • V20 • iPhone 6S • iPhone 11 Pro • GS7 Edge • GS10e • HTC U11 • Stylo 6 • X power • iPhone 6S Plus • iPhone 11 Pro • GS8 • GS10+ • G7 ThinQ • V40 ThinQ • iPhone SE Max • GS8+ • GS10 5G • G8 ThinQ • V50 ThinQ • iPhone SE2 • iPhone 12 • GS9 • Note 10 • G8X ThinQ • V60 ThinQ 5G • iPhone 7 • iPhone 12 Pro • GS9+ • Note 10+ • V60 ThinQ 5G • iPhone 7 Plus • iPhone 12 Pro • A50 • GS20 5G Dual Screen • iPhone 8 Max • A51 • GS20+ 5G • Velvet 5G • iPhone 8 Plus • iPhone 12 Mini • Note 4 • GS20 Ultra 5G • Note 5 • Galaxy S20 FE 5G • GS21 5G • GS21+ 5G • GS21 Ultra 5G Monthly Charge, Deductible/Service Fee, and Repair Schedule -

These Phones Will Still Work on Our Network After We Phase out 3G in February 2022

Devices in this list are tested and approved for the AT&T network Use the exact models in this list to see if your device is supported See next page to determine how to find your device’s model number There are many versions of the same phone, and each version has its own model number even when the marketing name is the same. ➢EXAMPLE: ▪ Galaxy S20 models G981U and G981U1 will work on the AT&T network HOW TO ▪ Galaxy S20 models G981F, G981N and G981O will NOT work USE THIS LIST Software Update: If you have one of the devices needing a software upgrade (noted by a * and listed on the final page) check to make sure you have the latest device software. Update your phone or device software eSupport Article Last updated: Sept 3, 2021 How to determine your phone’s model Some manufacturers make it simple by putting the phone model on the outside of your phone, typically on the back. If your phone is not labeled, you can follow these instructions. For iPhones® For Androids® Other phones 1. Go to Settings. 1. Go to Settings. You may have to go into the System 1. Go to Settings. 2. Tap General. menu next. 2. Tap About Phone to view 3. Tap About to view the model name and number. 2. Tap About Phone or About Device to view the model the model name and name and number. number. OR 1. Remove the back cover. 2. Remove the battery. 3. Look for the model number on the inside of the phone, usually on a white label. -

Device Compatibility

Device compatibility Check if your smartphone is compatible with your Rexton devices Direct streaming to hearing aids via Bluetooth Apple devices: Rexton Mfi (made for iPhone, iPad or iPod touch) hearing aids connect directly to your iPhone, iPad or iPod so you can stream your phone calls and music directly into your hearing aids. Android devices: With Rexton BiCore devices, you can now also stream directly to Android devices via the ASHA (Audio Streaming for Hearing Aids) standard. ASHA-supported devices: • Samsung Galaxy S21 • Samsung Galaxy S21 5G (SM-G991U)(US) • Samsung Galaxy S21 (US) • Samsung Galaxy S21+ 5G (SM-G996U)(US) • Samsung Galaxy S21 Ultra 5G (SM-G998U)(US) • Samsung Galaxy S21 5G (SM-G991B) • Samsung Galaxy S21+ 5G (SM-G996B) • Samsung Galaxy S21 Ultra 5G (SM-G998B) • Samsung Galaxy Note 20 Ultra (SM-G) • Samsung Galaxy Note 20 Ultra (SM-G)(US) • Samsung Galaxy S20+ (SM-G) • Samsung Galaxy S20+ (SM-G) (US) • Samsung Galaxy S20 5G (SM-G981B) • Samsung Galaxy S20 5G (SM-G981U1) (US) • Samsung Galaxy S20 Ultra 5G (SM-G988B) • Samsung Galaxy S20 Ultra 5G (SM-G988U)(US) • Samsung Galaxy S20 (SM-G980F) • Samsung Galaxy S20 (SM-G) (US) • Samsung Galaxy Note20 5G (SM-N981U1) (US) • Samsung Galaxy Note 10+ (SM-N975F) • Samsung Galaxy Note 10+ (SM-N975U1)(US) • Samsung Galaxy Note 10 (SM-N970F) • Samsung Galaxy Note 10 (SM-N970U)(US) • Samsung Galaxy Note 10 Lite (SM-N770F/DS) • Samsung Galaxy S10 Lite (SM-G770F/DS) • Samsung Galaxy S10 (SM-G973F) • Samsung Galaxy S10 (SM-G973U1) (US) • Samsung Galaxy S10+ (SM-G975F) • Samsung -

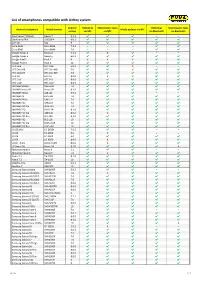

List of Smartphones Compatible with Airkey System

List of smartphones compatible with AirKey system Android Unlocking Maintenance tasks Unlocking Maintenance tasks Android smartphone Model number Media updates via NFC version via NFC via NFC via Bluetooth via Bluetooth Asus Nexus 7 (Tablet) Nexus 7 5.1.1 ✔ ✔ ✔ – – Blackberry PRIV STV100-4 6.0.1 ✔ ✔ ✔ ✔ ✔ CAT S61 S61 9 ✔ ✔ ✔ ✔ ✔ Doro 8035 Doro 8035 7.1.2 – – – ✔ ✔ Doro 8040 Doro 8040 7.0 – – – ✔ ✔ Google Nexus 4 Nexus 4 5.1.1 ✔ X ✔ – – Google Nexus 5 Nexus 5 6.0.1 ✔ ✔ ✔ ✔ ✔ Google Pixel 2 Pixel 2 9 X X X ✔ ✔ Google Pixel 4 Pixel 4 10 ✔ ✔ ✔ ✔ ✔ HTC One HTC One 5.0.2 ✔ ✔ X – – HTC One M8 HTC One M8 6.0 ✔ ✔ X ✔ ✔ HTC One M9 HTC One M9 7.0 ✔ ✔ ✔ ✔ ✔ HTC 10 HTC 10 8.0.0 ✔ X X ✔ ✔ HTC U11 HTC U11 8.0.0 ✔ ✔ ✔ ✔ ✔ HTC U12+ HTC U12+ 8.0.0 ✔ ✔ ✔ ✔ ✔ HUAWEI Mate 9 MHA-L09 7.0 ✔ ✔ ✔ ✔ ✔ HUAWEI Nexus 6P Nexus 6P 8.1.0 ✔ ✔ ✔ ✔ ✔ HUAWEI P8 lite ALE-L21 5.0.1 ✔ ✔ ✔ – – HUAWEI P9 EVA-L09 7.0 ✔ ✔ ✔ ✔ ✔ HUAWEI P9 lite VNS-L21 7.0 ✔ ✔ ✔ ✔ ✔ HUAWEI P10 VTR-L09 7.0 ✔ ✔ ✔ ✔ ✔ HUAWEI P10 lite WAS-LX1 7.0 ✔ ✔ ✔ ✔ ✔ HUAWEI P20 EML-L29 8.1.0 ✔ ✔ ✔ ✔ ✔ HUAWEI P20 lite ANE-LX1 8.0.0 ✔ X ✔ ✔ ✔ HUAWEI P20 Pro CLT-L29 8.1.0 ✔ ✔ ✔ ✔ ✔ HUAWEI P30 ELE-L29 10 ✔ ✔ ✔ ✔ ✔ HUAWEI P30 lite MAR-LX1A 10 ✔ ✔ ✔ ✔ ✔ HUAWEI P30 Pro VOG-L29 10 ✔ ✔ ✔ ✔ ✔ LG G2 Mini LG-D620r 5.0.2 ✔ ✔ ✔ – – LG G3 LG-D855 5.0 ✔ X ✔ – – LG G4 LG-H815 6.0 ✔ ✔ ✔ ✔ ✔ LG G6 LG-H870 8.0.0 ✔ X ✔ ✔ ✔ LG G7 ThinQ LM-G710EM 8.0.0 ✔ X ✔ ✔ ✔ LG Nexus 5X Nexus 5X 8.1.0 ✔ ✔ ✔ ✔ X Motorola Moto X Moto X 5.1 ✔ ✔ ✔ – – Motorola Nexus 6 Nexus 6 7.0 ✔ X ✔ ✔ ✔ Nokia 7.1 TA-1095 8.1.0 ✔ ✔ X ✔ ✔ Nokia 7.2 TA-1196 10 ✔ ✔ ✔ -

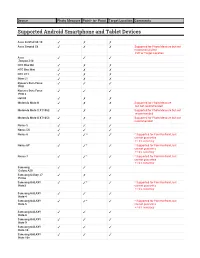

List of Supported Devices

Device Photo Measure Point- to- Point Target Location Comments Supported Android Smartphone and Tablet Devices Asus ZenPad 3S 10 ✓ ✗ ✗ Asus Zenpad Z8 ✓ ✗ ✗ Supported for Photo Measure but not recommended for P2P or Target Location Asus ✓ ✓ ✓ Zenpad Z10 HTC One M8 ✓ ✗ ✗ HTC One Mini ✓ ✗ ✗ HTC U11 ✓ ✗ ✗ iNew L1 ✓ ✗ ✗ Kyocera Dura Force ✓ ✓ ✓ PRO Kyocera Dura Force ✓ ✓ ✓ PRO 2 LGV20 ✓ ✗ ✗ Motorola Moto G ✓ ✗ ✗ Supported for Photo Measure but not recommended Motorola Moto X XT1052 ✓ ✗ ✗ Supported for Photo Measure but not recommended Motorola Moto X XT1053 ✓ ✗ ✗ Supported for Photo Measure but not recommended Nexus 5 ✓ ✓ ✓ Nexus 5X ✓ ✓ ✓ Nexus 6 ✓ ✓* ✓ * Supported for Point-to-Point, but cannot guarantee +/-3% accuracy Nexus 6P ✓ ✓* ✓ * Supported for Point-to-Point, but cannot guarantee +/-3% accuracy Nexus 7 ✓ ✓* ✓ * Supported for Point-to-Point, but cannot guarantee +/-3% accuracy Samsung ✓ ✓ ✓ Galaxy A20 Samsung Galaxy J7 ✓ ✗ ✓ Prime Samsung GALAXY ✓ ✓* ✓ * Supported for Point-to-Point, but Note3 cannot guarantee +/-3% accuracy Samsung GALAXY ✓ ✓ ✓ Note 4 Samsung GALAXY ✓ ✓* ✓ * Supported for Point-to-Point, but Note 5 cannot guarantee +/-3% accuracy Samsung GALAXY ✓ ✓ ✓ Note 8 Samsung GALAXY ✓ ✓ ✓ Note 9 Samsung GALAXY ✓ ✓ ✓ Note 10 Samsung GALAXY ✓ ✓ ✓ Note 10+ Device Photo Measure Point- to- Point Target Location Comments Samsung GALAXY ✓ ✓ ✓ Note 10+ 5G Samsung GALAXY ✓ ✓ ✓ Note 20 Samsung GALAXY ✓ ✓ ✓ Note 20 5G Samsung GALAXY ✓ ✗ ✗ Supported for Photo Measure but not Tab 4 (old) recommended Samsung GALAXY ✓ ✗ ✓ Supported for Photo -

English-Basic-Deductible-Tool.Pdf

T-Mobile® Deductible and Fee Schedule Alcatel Tier BlackBerry Tier HTC Tier 3T 8 7100T, 7105T 10 665 7230, 7290 Flyer 768 8120, 8520 myTouch 2 A30 9780 Bold myTouch 4G Slide 3 Aspire Classic One Evolve Curve Sensation 4G Fierce XL Windows Phone 8X Fierce, Fierce 2, Fierce 4 9700 Bold 1 GO FLIP, GO FLIP 3 9810, 9900 3 JOY TAB Q10 Huawei Tier LINKZONE, LINKZONE 2 Z10 Comet Pixi 7 Prism, Prism II POP 7 Priv 4 Sonic 4G POP Astro 1 REVVL Coolpad Tier Summit Soul Tap Catalyst webConnect JOY TAB Kids 2 Defiant Rogue 1 myTouch 2 IDOL 4S 3 Snap S7 PRO 3 Surf Apple Tier life KonnectONE Tier 2 iPad One M9 Moxee Signal 1 iPad 7th Gen iPad Air 2 Dell Tier iPad Mini, iPad Mini 2, iPad Mini 4 Kyocera Tier Streak 7 2 iPhone 4, iPhone 4s iPhone 5, iPhone 5c, iPhone 5s 3 Hydro WAVE Ericsson Tier 1 iPhone 6s Rally iPhone SE World 1 DuraForce PRO, DuraForceXD 3 Watch Series 3 Watch Series 5 Garmin Tier LG Tier iPad Air Garminfone 3 iPad Mini 3 450 iPad Pro 9.7 GEOTAB Tier Aristo iPhone 6 Aristo 2 PLUS 4 GO8 iPhone 6 Plus 1 Aristo 4+ iPhone 6s Plus SyncUP FLEET Aristo 5 dLite iPhone 7, iPhone 7 Plus 1 Watch Series 4 Google Tier GS170 Pixel 3a K7, K10 iPad Pro 10.5-inch 3 K20 Plus Pixel 3a XL iPad Pro 11-inch Leon iPad Pro 12.9-inch Pixel 3 Optimus L90 iPhone 8, iPhone 8 Plus Sentio iPhone X Pixel 3 XL 4 5 iPhone XR Pixel 4 DoublePlay iPhone XS, iPhone XS MAX Pixel 4 XL 5 G Pad 5 iPhone 11 G Pad F 8.0 iPhone 11 Pro, iPhone 11 Pro Max HTC Tier G Pad X2 8.0, G Pad X2 8.0 Plus Watch Nike+ Series 3 G Pad X 8.0 Desire 1 G Stylo G2 ASUS Tier Amaze 4G G2x Dash 3G Google Nexus 7 2 K30 G2 K40 2 HD2, HD7 K51 life Lion myTouch 3G 1.2, myTouch 3G slide 2 myTouch myTouch 4G Optimus F3, F3Q, F6, L9, T One M9 Stylo 2 PLUS, Stylo 3 PLUS One S Stylo 4 Radar 4G Stylo 5 Shadow Stylo 6 Wildfire S V20 Please note: If you switch your device to one that is classified in another tier, the monthly charge for your new tier will be reflected on your T-Mobile bill. -

Google Pixel Phones on Android 11.0 (MDFPP31/WLANCEP10) Security Target

Google Pixel Phones on Android 11.0 (MDFPP31/WLANCEP10) Security Target Version 1.6 2021/02/04 Prepared for: Google LLC 1600 Amphitheatre Parkway Mountain View, CA 94043 USA Prepared By: www.gossamersec.com Google Pixel Phones on Android 11.0 (MDFPP31/WLANCEP10) Security Target Version 1.6, 2021/02/04 1. SECURITY TARGET INTRODUCTION ........................................................................................................ 4 1.1 SECURITY TARGET REFERENCE ...................................................................................................................... 4 1.2 TOE REFERENCE ............................................................................................................................................ 4 1.3 TOE OVERVIEW ............................................................................................................................................. 5 1.4 TOE DESCRIPTION ......................................................................................................................................... 6 1.4.1 TOE Architecture ................................................................................................................................... 7 1.4.2 TOE Documentation .............................................................................................................................. 9 2. CONFORMANCE CLAIMS ............................................................................................................................ 10 2.1 CONFORMANCE RATIONALE -

These Phones Will Still Work on Our Network After We Phase out 3G in February 2022

These phones will still work on our network after we phase out 3G in February 2022 Apple iPhone 6 and newer Samsung • Galaxy A71 5G (A716U, • Galaxy Note20 5G (N981U, • Galaxy S21 5G (G991U, G991U1) • Galaxy S10 (G973U, G973UC, • Galaxy XCover FieldPro (G889A) A716U1) N981U1) • Galaxy S21+ 5G (G996U, G996U1) G973U1) • Galaxy XCover Pro (G715U1, • Galaxy A50 (A505U1, A505A) • Galaxy Note20 Ultra 5G (N986U, • Galaxy S21 Ultra 5G (G998U, • Galaxy S10+ (G975U, G975U1) G715A) • Galaxy A51 5G (A516U, N986U1) G998U1) • Galaxy S10 5G (G977U) A516U1, A516UP) • Galaxy S10e (G970U, G970U1) • Galaxy Z flip 5G (F707U, F707U1) • Galaxy A51 (A515U, A515U1) • Galaxy Note10 (N970U, N970U1) • Galaxy S20 5G (G981U, G981U1) • Galaxy S10 Lite (G770U1) • Galaxy Z Flip (F700U/DS, F700U1) • Galaxy A21 SE (A215U1) • Galaxy Note10+ (N975U, N975U1) • Galaxy S20+ 5G (G986U, G986U1) • Galaxy Z Fold2 5G (F916U, • Galaxy A11 (A115A, A115AZ, • Galaxy Note10+ 5G (N976U) • Galaxy S20 Ultra 5G (G988U, • Galaxy S9 (G960U, G960U1) F916U1) A115AP, A115U1) G988U1) • Galaxy S9+ (G965U, G964U1) • Galaxy Z Fold (F900U, F900U1) • Galaxy A10e (A102U, A102UC, • Galaxy Note9 (N960U, N960U1) • Galaxy S20 FE (G781U, G781U1, A102U1) • Galaxy Note8 (N950U) G781UC) • Galaxy S8 (G950U) • Galaxy A6 (A600A, A600AZ) • Galaxy Note5 (N920A) • Galaxy S8 Active (G892A) • Galaxy A01 (A015A, SM- • Galaxy Note4 (N910A) • Galaxy S8+ (G955U) A015U1) • Galaxy Note Edge (N915A) • Galaxy S7 Edge (G935A) • Galaxy Express Prime 3 (J337A) • Galaxy S7 (G930A) • Galaxy Express Prime 2/J3 • Galaxy S7 Active -

Barometer of Mobile Internet Connections in Poland

Barometer of Mobile Internet Connections in Poland Publication of July 21, 2020 First half 2020 nPerf is a trademark owned by nPerf SAS, 87 rue de Sèze 69006 LYON – France. Contents 1 Summary of results ...................................................................................................................... 2 1.1 nPerf score, all technologies combined ............................................................................... 2 1.2 Our analysis ........................................................................................................................... 3 2 Overall results 2G/3G/4G ............................................................................................................. 3 2.1 Data amount and distribution ............................................................................................... 3 2.2 Success rate 2G/3G/4G ........................................................................................................ 4 2.3 Download speed 2G/3G/4G .................................................................................................. 4 2.4 Upload speed 2G/3G/4G ....................................................................................................... 5 2.5 Latency 2G/3G/4G ................................................................................................................ 5 2.6 Browsing test 2G/3G/4G....................................................................................................... 6 2.7 Streaming test 2G/3G/4G .................................................................................................... -

Oslo Energy Compatibility List

OSLO ENERGY COMPATIBILITY LIST BRAND MODELS Apple iPhone 8 (Plus) Apple iPhone X / Apple iPhone XS (Max)/ iPhone XR Apple Apple iPhone 11/ iPhone 11 Pro (Max) Apple iPhone SE 2nd Gen. (2020) Apple 12 (Mini), 12 Pro (Max) Blackberry Blackberry Priv Blackberry Z30 Samsung Galaxy S20/ S20+ (Plus)/ S20 Ultra Samsung Galaxy S10e/ S10 / S10+ (Plus) Samsung Galaxy S9/ S9+ (Plus) Samsung Galaxy S8/ S8+ (Plus) Samsung Galaxy S7/ edge Samsung Galaxy S6/ edge/ edge+ Samsung Samsung Galaxy Z Flip Samsung Galaxy Fold Samsung Z Fold 2 Samsung Galaxy Note 10/ Note 10+ (Plus) Samsung Galaxy Note 5 Samsung Galaxy Note 7 Samsung Galaxy Note 8 Samsung Galaxy Note 9 Google Pixel 3/ Pixel 3 XL Google Pixel 4/ Pixel 4 XL Google Google Pixel 5 Google Nexus 4 Google Nexus 5 Google Nexus 6 Huawei P30 (Pro) Huawei Huawei P40 Pro (Pro+) Huawei Mate 20 Pro Huawei Mate RS OnePlus OnePlus 8 Pro LG V50 / V50 ThinQ LG V40 ThinQ LG G7 ThinQ LG LG G8 ThinQ LG V30 (Plus) LG Optimus F5 Sony Xperia XZ3 Sony Sony Xperia XZ2 Nokia 9 PureView Nokia 8 Sirocco Nokia Lumia 1520 Nokia Nokia Lumia 930 Nokia Lumia 929 / Icon Nokia Lumia 920 Nokia Lumia 830 Nokia Lumia 735 ZTE Axon 10 Pro ZTE Axon 9 Pro Asus PadFone S Others Elephone P9000 Blackview BV6300 Pro Kogan Agora XS Motorola Moto X Force Xiaomi Mi Mix 3 Xiaomi Mi 9 COMPATIBILITY Qi certified phones with appropriate dimensions only. Refer to the list above. WIRELESS CHARGING OUTPUT Up to 10W TRANSMISSION DISTANCE 3-6 mm Wireless charging may not work properly if you have a thick case on your phone. -

Google Pixel Phones on Android 11 Administrator Guidance Documentation

Google Pixel Phones on Android 11 Administrator Guidance Documentation Version 1.3 02/04/2021 1. DOCUMENT INTRODUCTION ...................................................................................... 4 1.1 EVALUATED DEVICES ......................................................................................................... 4 1.2 ACRONYMS ......................................................................................................................... 4 2. EVALUATED CAPABILITIES ........................................................................................ 5 2.1 DATA PROTECTION ............................................................................................................. 5 2.1.1 File-Based Encryption ................................................................................................ 5 2.2 LOCK SCREEN ..................................................................................................................... 6 2.3 KEY MANAGEMENT ............................................................................................................ 6 2.3.1 KeyStore ...................................................................................................................... 6 2.3.2 KeyChain..................................................................................................................... 7 2.4 DEVICE INTEGRITY ............................................................................................................. 7 2.4.1 Verified Boot ..............................................................................................................