Single Port to Dual Port Conversion for an LSI Memory

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

The Use of Next Generation Sequencing to Study the Environmental Mycobiome and Its Potential Health Effects

The use of next generation sequencing to study the environmental mycobiome and its potential health effects Emma Marczylo Bioaerosols – June 2017 Overview • Brief Background: • Why are CRCE interested in fungal bioaerosols? • Mycobiome analysis: • Why use next generation sequencing? • Ongoing work • What is the current focus of CRCE’s bioaerosol research? 2 Bioaerosols – June 2017 Why bioaerosols? • Respiratory health/toxicology a big focus within our department & bioaerosols represent a current respiratory health concern 3 Bioaerosols – June 2017 Why bioaerosols? • Common sources relevant to public health 4 Bioaerosols – June 2017 Why bioaerosols? • Public concern over health effects of living near composting and intensive farming sites • Systematic reviews on exposures and health outcomes related to bioaerosol emissions from composting facilities (published 2015*) or intensive farming (ongoing) in collaboration with SAHSU • Evidence on both exposure assessment and health effects are limited • A big unknown is the microbial composition of such bioaerosols *Pearson et al, 2015, J Toxicol Environ Health B Crit Rev,18:43-69 5 Bioaerosols – June 2017 Why fungi? Normally die rapidly due to water evaporation, although increased humidity and clumping can prolong survival • Can remain viable for much longer periods, even at low humidity & high/low temperatures • Much less known about the fungal composition of bioaerosols (and other samples) • Fungi linked with development and exacerbation of asthma symptoms 6 Bioaerosols – June 2017 Mycobiome -

Framework for In-Field Analyses of Performance and Sub-Technique Selection in Standing Para Cross-Country Skiers

sensors Article Framework for In-Field Analyses of Performance and Sub-Technique Selection in Standing Para Cross-Country Skiers Camilla H. Carlsen 1,*, Julia Kathrin Baumgart 1, Jan Kocbach 1,2, Pål Haugnes 1 , Evy M. B. Paulussen 1,3 and Øyvind Sandbakk 1 1 Centre for Elite Sports Research, Department of Neuromedicine and Movement Science, Faculty of Medicine and Health Sciences, Norwegian University of Science and Technology, 7491 Trondheim, Norway; [email protected] (J.K.B.); [email protected] (J.K.); [email protected] (P.H.); [email protected] (E.M.B.P.); [email protected] (Ø.S.) 2 NORCE Norwegian Research Centre AS, 5008 Bergen, Norway 3 Faculty of Health, Medicine & Life Sciences, Maastricht University, 6200 MD Maastricht, The Netherlands * Correspondence: [email protected]; Tel.: +47-452-40-788 Abstract: Our aims were to evaluate the feasibility of a framework based on micro-sensor technology for in-field analyses of performance and sub-technique selection in Para cross-country (XC) skiing by using it to compare these parameters between elite standing Para (two men; one woman) and able- bodied (AB) (three men; four women) XC skiers during a classical skiing race. The data from a global navigation satellite system and inertial measurement unit were integrated to compare time loss and selected sub-techniques as a function of speed. Compared to male/female AB skiers, male/female Para skiers displayed 19/14% slower average speed with the largest time loss (65 ± 36/35 ± 6 s/lap) Citation: Carlsen, C.H.; Kathrin found in uphill terrain. -

Field Indicators of Hydric Soils

United States Department of Field Indicators of Agriculture Natural Resources Hydric Soils in the Conservation Service United States In cooperation with A Guide for Identifying and Delineating the National Technical Committee for Hydric Soils Hydric Soils, Version 8.2, 2018 Field Indicators of Hydric Soils in the United States A Guide for Identifying and Delineating Hydric Soils Version 8.2, 2018 (Including revisions to versions 8.0 and 8.1) United States Department of Agriculture, Natural Resources Conservation Service, in cooperation with the National Technical Committee for Hydric Soils Edited by L.M. Vasilas, Soil Scientist, NRCS, Washington, DC; G.W. Hurt, Soil Scientist, University of Florida, Gainesville, FL; and J.F. Berkowitz, Soil Scientist, USACE, Vicksburg, MS ii In accordance with Federal civil rights law and U.S. Department of Agriculture (USDA) civil rights regulations and policies, the USDA, its Agencies, offices, and employees, and institutions participating in or administering USDA programs are prohibited from discriminating based on race, color, national origin, religion, sex, gender identity (including gender expression), sexual orientation, disability, age, marital status, family/parental status, income derived from a public assistance program, political beliefs, or reprisal or retaliation for prior civil rights activity, in any program or activity conducted or funded by USDA (not all bases apply to all programs). Remedies and complaint filing deadlines vary by program or incident. Persons with disabilities who require alternative means of communication for program information (e.g., Braille, large print, audiotape, American Sign Language, etc.) should contact the responsible Agency or USDA’s TARGET Center at (202) 720-2600 (voice and TTY) or contact USDA through the Federal Relay Service at (800) 877-8339. -

National Classification? 13

NATIONAL CL ASSIFICATION INFORMATION FOR MULTI CLASS SWIMMERS Version 1.2 2019 PRINCIPAL PARTNER MAJOR PARTNERS CLASSIFICATION PARTNERS Version 1.2 2019 National Swimming Classification Information for Multi Class Swimmers 1 CONTENTS TERMINOLOGY 3 WHAT IS CLASSIFICATION? 4 WHAT IS THE CLASSIFICATION PATHWAY? 4 WHAT ARE THE ELIGIBLE IMPAIRMENTS? 5 CLASSIFICATION SYSTEMS 6 CLASSIFICATION SYSTEM PARTNERS 6 WHAT IS A SPORT CLASS? 7 HOW IS A SPORT CLASS ALLOCATED TO AN ATHLETE? 7 WHAT ARE THE SPORT CLASSES IN MULTI CLASS SWIMMING? 8 SPORT CLASS STATUS 11 CODES OF EXCEPTION 12 HOW DO I CHECK MY NATIONAL CLASSIFICATION? 13 HOW DO I GET A NATIONAL CLASSIFICATION? 13 MORE INFORMATION 14 CONTACT INFORMATION 16 Version 1.2 2019 National Swimming Classification Information for Multi Class Swimmers 2 TERMINOLOGY Assessment Specific clinical procedure conducted during athlete evaluation processes ATG Australian Transplant Games SIA Sport Inclusion Australia BME Benchmark Event CISD The International Committee of Sports for the Deaf Classification Refers to the system of grouping athletes based on impact of impairment Classification Organisations with a responsibility for administering the swimming classification systems in System Partners Australia Deaflympian Representative at Deaflympic Games DPE Daily Performance Environment DSA Deaf Sports Australia Eligibility Criteria Requirements under which athletes are evaluated for a Sport Class Evaluation Process of determining if an athlete meets eligibility criteria for a Sport Class HI Hearing Impairment ICDS International Committee of Sports for the Deaf II Intellectual Impairment Inas International Federation for Sport for Para-athletes with an Intellectual Disability General term that refers to strategic initiatives that address engagement of targeted population Inclusion groups that typically face disadvantage, including people with disability. -

United States Olympic Committee and U.S. Department of Veterans Affairs

SELECTION STANDARDS United States Olympic Committee and U.S. Department of Veterans Affairs Veteran Monthly Assistance Allowance Program The U.S. Olympic Committee supports Paralympic-eligible military veterans in their efforts to represent the USA at the Paralympic Games and other international sport competitions. Veterans who demonstrate exceptional sport skills and the commitment necessary to pursue elite-level competition are given guidance on securing the training, support, and coaching needed to qualify for Team USA and achieve their Paralympic dreams. Through a partnership between the United States Department of Veterans Affairs and the USOC, the VA National Veterans Sports Programs & Special Events Office provides a monthly assistance allowance for disabled Veterans of the Armed Forces training in a Paralympic sport, as authorized by 38 U.S.C. § 322(d) and section 703 of the Veterans’ Benefits Improvement Act of 2008. Through the program the VA will pay a monthly allowance to a Veteran with a service-connected or non-service-connected disability if the Veteran meets the minimum VA Monthly Assistance Allowance (VMAA) Standard in his/her respective sport and sport class at a recognized competition. Athletes must have established training and competition plans and are responsible for turning in monthly and/or quarterly forms and reports in order to continue receiving the monthly assistance allowance. Additionally, an athlete must be U.S. citizen OR permanent resident to be eligible. Lastly, in order to be eligible for the VMAA athletes must undergo either national or international classification evaluation (and be found Paralympic sport eligible) within six months of being placed on the allowance pay list. -

Early Childhood Special Education/Early Intervention Revalidated 2017

Initial Specialty Set: Early Childhood Special Education/Early Intervention Revalidated 2017 Initial Preparation Standard 1: Learner Development and Individual Learning Differences Knowledge ECSE.K1.1 Theories of typical and atypical early childhood development ECSE.K1.2 Biological and environmental factors that affect pre-, peri-, and postnatal development and learning ECSE.K1.3 Specific disabilities, including the etiology, characteristics, and classification of common disabilities in infants and young children, and specific implications for development and learning in the first years of life ECSE.K1.4 Impact of medical conditions and related care on development and learning ECSE.K1.5 Impact of medical conditions on family concerns, resources, and priorities ECSE.K1.6 Factors that affect the mental health and social-emotional development of infants and young children ECSE.K1.7 Infants and young children develop and learn at varying rates ECSE.K1.8 Impact of child’s abilities, needs, and characteristics on development and learning ECSE.K1.9 Impact of language delays on cognitive, social-emotional, adaptive, play, temperament and motor development ECSE.K1.10 Impact of language delays on behavior Skills ECSE.S1.1 Develop, implement, and evaluate learning experiences and strategies that respect the diversity of infants and young children, and their families ECSE.S1.2 Develop and match learning experiences and strategies to characteristics of infants and young children ECSE.S1.3 Support and facilitate family and child interactions as primary -

2021 Florida Elite Football Official Rulebook

2021 FLORIDA ELITE FOOTBALL OFFICIAL RULEBOOK 2021 FL ELITE RULEBOOK 1 TABLE OF CONTENTS PART I-THE FLORIDA ELITE PROGRAM HEADQUARTERS CONFERENCE REMARKS ADMINISTRATIVE BYLAWS MANUAL MISSION STATEMENT GOALS AND PHILOSOPHY OF THE FLORIA ELITE PROGRAM PART II-FLORIDA ELITE STRUCTURE DEFINITIONS S1-LEAGUE S2-ASSOCIATION S3-ADMINISTRATORS S4-TEAM S5-DIVISION INTRODUCTION TO THE RULES PART III - FLORIDA ELITE REGULATIONS ARTICLE 1: POWERS/AUTHORITY OF LEAGUE ARTICLE 2: BOUNDARIES ARTICLE 3: COACHES REQUIREMENTS ARTICLE 4: REGISTRATION S1-PARENTAL CONSENT S2-MEDICAL EXAMINATION S3-PROOF OF AGE S4-SCHOLASTIC FITNESS S5-INFECTIOUS DISEASE WAIVER ARTICLE 5: FORMATION OF TEAMS AND SQUADS ARTICLE 6: MANDATORY CUTS ARTICLE 7: VOLUNTARY CUTS ARTICLE 8: CERTIFICATION ARTICLE 9: DROPS AND ADDS ARTICLE 10: NO ALL-STARS ARTICLE 11: AWARDS ARTICLE 12: PRACTICE ARTICLE 13: CAMPS ARTICLE 14: IMPORTANT POINT – MEDICAL & CONCUSSIONS S1-CONCUSSIONS ARTICLE 15: CHARGING ADMISSION ARTICLE 16: PROTESTS ARTICLE 17: PATCH REQUIREMENT ARTICLE 18: MANDATORY BACKGROUND CHECKS PART IV - ENFORCEMENT POLICY POLICE POWERS/HEARINGS & APPEALS MINIMUM MANDATED PENALTIES S1-ADULT OFFENSES S2-JUVENILE OFFENSES S3-TEAM AND ASSOCIATION OFFENSES 2021 FL ELITE RULEBOOK 2 PART V-GENERAL FOOTBALL RULES RULE 1: AGE REQUIREMENTS RULE 2: LENGTH OF PERIODS RULE 3: DIGITAL BOOK CHECK PROCEDURES RULE 4: PLAYING FIELDS RULE 5: INJURED PLAYERS PART VI- ROOKIE - SENIORS FOOTBALL RULES RULE 1: AGES RULE 2: CERTIFICATION OF PLAYERS RULE 3: ROSTER SIZE S1-MAXIMUM ROSTER SIZE: S2-MINIMUM ROSTER -

(VA) Veteran Monthly Assistance Allowance for Disabled Veterans

Revised May 23, 2019 U.S. Department of Veterans Affairs (VA) Veteran Monthly Assistance Allowance for Disabled Veterans Training in Paralympic and Olympic Sports Program (VMAA) In partnership with the United States Olympic Committee and other Olympic and Paralympic entities within the United States, VA supports eligible service and non-service-connected military Veterans in their efforts to represent the USA at the Paralympic Games, Olympic Games and other international sport competitions. The VA Office of National Veterans Sports Programs & Special Events provides a monthly assistance allowance for disabled Veterans training in Paralympic sports, as well as certain disabled Veterans selected for or competing with the national Olympic Team, as authorized by 38 U.S.C. 322(d) and Section 703 of the Veterans’ Benefits Improvement Act of 2008. Through the program, VA will pay a monthly allowance to a Veteran with either a service-connected or non-service-connected disability if the Veteran meets the minimum military standards or higher (i.e. Emerging Athlete or National Team) in his or her respective Paralympic sport at a recognized competition. In addition to making the VMAA standard, an athlete must also be nationally or internationally classified by his or her respective Paralympic sport federation as eligible for Paralympic competition. VA will also pay a monthly allowance to a Veteran with a service-connected disability rated 30 percent or greater by VA who is selected for a national Olympic Team for any month in which the Veteran is competing in any event sanctioned by the National Governing Bodies of the Olympic Sport in the United State, in accordance with P.L. -

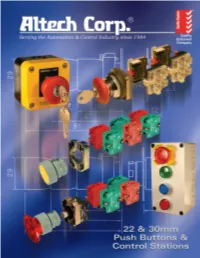

Pushbuttons.Pdf

PushButtons2013Cover.QXD_CircuitBreakers_2006Cover.QXD 10/3/17 2:20 PM Page 1 Altech Corporation 35 Royal Road Flemington, NJ 08822-6000 P 908.806.9400 • F 908.806.9490 www.altechcorp.com Altech Corp.® 255-052013-3M Printed July 2013 AltechAltech CorporationCorporation Since 1984, Altech Corporation has grown to become a leading supplier of automation and industrial control components. Headquartered in Flemington, NJ, Altech has an experienced staff of engineering, manufacturing and sales personnel to provide the highest quality products with superior service. This is the Altech Commitment! Altech 22 and 30mm Push Buttons offer ideal cost-effective solutions for control circuits utilizing both direct and remote management applications. Ease of assembly has been engineered into the design; the only tool necessary for installation is a screwdriver. • LED Indicating Devices • Pilot Lights • Push Button Stations • Push Button Enclosures • UL Recognized • Custom Push Button Assemblies • All Very Competitively Priced Our well trained technical experts welcome the opportunity to answer your technical questions and provide solutions to your automation and control needs. Give us a call or visit www.altechcorp.com. Quality Commitment Altech’s control components meet diverse national and international standards such as UL, NEC, CSA, IEC, VDE and more. Altech provides superior customer service and delivery through Total Quality Management and Continuous Process Improvement. Altech is ISO 9001 approved. We perform these services with honesty and integrity -

Official Rules

2018 Willamette Valley Youth Football & Cheer OFFICIAL RULES Page 1 Willamette Valley Youth Football & Cheer Table of Contents Part I – The WVYFC Program ............................................................... 5 Article 1: Members Code of Conduct ............................................. 5 Part II – WVYFC Structure .................................................................... 7 Part III – Regulations ............................................................................ 7 Article 1: Authority of League ......................................................... 7 Article 2: Boundaries ....................................................................... 7 Article 3: Coaches Requirements .................................................... 8 Article 4: Registration ..................................................................... 8 Article 5: Formation of Teams ........................................................ 9 Article 6: Mandatory Cuts ............................................................. 10 Article 7: Voluntary Cuts ............................................................... 10 Article 8: Certification ................................................................... 10 Article 9: Retention of Eligibility ................................................... 10 Article 10: No All Stars .................................................................. 10 Article 11: Awards ......................................................................... 11 Article 12: Practice (Definition & Date -

UPPET and UPOLET National Headcount 2016

RESULTS OF THE UNIVERSAL SECONDARY EDUCATION (USE/UPPET) & UNIVERSAL POST O’ LEVEL EDUCATION & TRAINING (UPOLET) NATIONAL HEAD COUNT EXERCISE CONDUCTED ON 19 JULY 2016 Statistics Section Education Planning and Policy Analysis Department Table of Contents Table of Contents ................................................................................................ 2 List of tables ........................................................................................................ 3 List of figures ....................................................................................................... 3 List of Acronyms ................................................................................................. 4 Executive Summary ............................................................................................. 5 2.0 Objective of the exercise ............................................................................. 7 3.0 Methodology ............................................................................................... 8 4.0 Preliminary Findings of the 2016 Headcount exercise .................................... 8 6.0 Policy Issues revealed by the Headcount ................................................... 16 7.0 Recommendations: .................................................................................... 16 ANNEXES ........................................................................................................ 16 Annex 1: USE/UPPET cohort analysis 2007-2016 .................................. -

The Paralympic Athlete Dedicated to the Memory of Trevor Williams Who Inspired the Editors in 1997 to Write This Book

This page intentionally left blank Handbook of Sports Medicine and Science The Paralympic Athlete Dedicated to the memory of Trevor Williams who inspired the editors in 1997 to write this book. Handbook of Sports Medicine and Science The Paralympic Athlete AN IOC MEDICAL COMMISSION PUBLICATION EDITED BY Yves C. Vanlandewijck PhD, PT Full professor at the Katholieke Universiteit Leuven Faculty of Kinesiology and Rehabilitation Sciences Department of Rehabilitation Sciences Leuven, Belgium Walter R. Thompson PhD Regents Professor Kinesiology and Health (College of Education) Nutrition (College of Health and Human Sciences) Georgia State University Atlanta, GA USA This edition fi rst published 2011 © 2011 International Olympic Committee Blackwell Publishing was acquired by John Wiley & Sons in February 2007. Blackwell’s publishing program has been merged with Wiley’s global Scientifi c, Technical and Medical business to form Wiley-Blackwell. Registered offi ce: John Wiley & Sons, Ltd, The Atrium, Southern Gate, Chichester, West Sussex, PO19 8SQ, UK Editorial offi ces: 9600 Garsington Road, Oxford, OX4 2DQ, UK The Atrium, Southern Gate, Chichester, West Sussex, PO19 8SQ, UK 111 River Street, Hoboken, NJ 07030-5774, USA For details of our global editorial offi ces, for customer services and for information about how to apply for permission to reuse the copyright material in this book please see our website at www.wiley.com/wiley-blackwell The right of the author to be identifi ed as the author of this work has been asserted in accordance with the UK Copyright, Designs and Patents Act 1988. All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording or otherwise, except as permitted by the UK Copyright, Designs and Patents Act 1988, without the prior permission of the publisher.