Solid-State Transmitters for IFF and SSR Systems

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Digital Multi–Programme TV/HDTV by Satellite

Digital multi–programme TV/HDTV by satellite M. Cominetti (RAI) A. Morello (RAI) M. Visintin (RAI) The progress of digital technology 1. Introduction since the WARC’77 is considered and the perspectives of future The significant progress of digital techniques in applications via satellite channels production, transmission and emission of radio are identified. Among these, digital and television programmes is rapidly changing the established concepts of broadcasting. multi–programme television systems, with different quality levels (EDTV, SDTV) and possible The latest developments in VLSI (very–large scale evolution to HDTV, are evaluated in integration) technology have significantly contrib- uted to the rapid emergence of digital image/video terms of picture quality and service compression techniques in broadcast and informa- availability on the satellite channels tion–oriented applications; optical fibre technolo- of the BSS bands (12 GHz and gy allows broadband end–to–end connectivity at 22 GHz) and of the FSS band (11 very high bit–rates including digital video capabil- GHz) in Europe. A usable channel ities; even the narrow–band terrestrial broadcast capacity of 45 Mbit/s is assumed, as channels in the VHF/UHF bands (6–7 MHz and 8 well as the adoption of advanced MHz) are under investigation, in the USA [1] and channel coding techniques with in Europe [2], for the future introduction of digital QPSK and 8PSK modulations. For television services. high and medium–power satellites, in operation or planned, the The interest for digital television in broadcasting receiving antenna diameters and multimedia communications is a clear exam- required for correct reception are ple of the current evolution from the analogue to reported. -

Miniature Radio Frequency Transponder Technology Suitability As Threatened Species Tags

Miniature radio frequency transponder technology suitability as threatened species tags SCIENCE FOR CONSERVATION: 71 Murray E. Douglas Published by Department of Conservation P.O. Box 10-420 Wellington, New Zealand 1 Science for Conservation presents the results of investigations by DoC staff, and by contracted science providers outside the Department of Conservation. Publications in this series are internally and externally peer reviewed January 1998, Department of Conservation ISSN 1173–2946 ISBN 0–478–01987–4 This publication originated from work done by Murray E. Douglas, Science & Research Division, Department of Conservation, Wellington. It was approved for publication by the Director, Science and Research Division, Department of Conservation, Wellington. Cataloguing-in-Publication data Douglas, Murray E. Miniature radio frequency transponder technology suitability as threatened species tags / Murray E. Douglas. Wellington, N.Z. : Dept. of Conservation, 1998. 1 v. ; 30 cm. (Science for conservation, 1173–2946 ; 71.) Includes bibliographical references. ISBN 0478019874 1. Radio telemetry. 2. Animal radio tracking. 3. Transponders. I. Title. II. Series: Science for conservation (Wellington, N.Z.) ; 71. 621.3848 20 zbn98–008524 2 CONTENTS Abstract 5 1. Introduction 5 1.1 Aim 5 1.2 Definitions 6 1.3 Background 7 2. Methods 8 2.1 Search methods 8 3. Findings 9 3.1 Active transponders and pagers 9 3.1.1 Technology experts 9 3.1.2 International products and companies 9 3.1.3 Locator Systems Ltd, New Zealand 9 Transponder size 10 Activation -

Part 13 Restricted Radiotelephone (Including Commercial Radio Operator)

Part 13 Restricted Radiotelephone (Including Commercial Radio Operator) RESTRICTED RADIOTELEPHONE OPERATOR PERMIT WHO NEEDS AN RP? At least one person holding an RP is required aboard stations in the maritime and aviation services when: making international flights, voyages, or communications; 2) using frequencies under 30 MHz; 3) using a satellite ship earth station, or 4) operating a vessel subject to the Bridge to Bridge Act (including domestic operation). WHO DOESN’T NEED AN RP? For mobile stations: 1) On board a voluntarily equipped ship using only VHF frequencies on domestic voyages OR using a radar, EPIRB, survival craft, or on-board station; 2) on board an aircraft using only VHF frequencies on domestic voyages OR using radar, radio altimeter, transponder, or other automated radionavigation transmitter; or 3) at a domestically operated marine utility station. For fixed stations: 1) at shore radar, shore radiolocation, maritime support, or shore radionavigation stations; 2) at a coast station or aeronautical ground station using only VHF frequencies; or 3) at an aeronautical enroute station which automatically transmits digital communications to aircraft. You no longer need an RP to operate a Broadcast station (e.g., AM, FM, TV). This requirement was eliminated on 12/1/95 (Report and Order, MM Docket No. 94-130 released 10/23/95). Restricted Radiotelephone Operator NOTE: Aliens who are not legally eligible for employment in the United States should also use FCC 605. New (Lifetime Permit & Limited Use) (Per Permit) Duplicate/Replacement -

RF Power Products October 2002 ABOUT ADVANCED POWER TECHNOLOGY RF

RF Power Products October 2002 ABOUT ADVANCED POWER TECHNOLOGY RF In 2002 Advanced Power Technology acquired two leading suppliers of silicon based radio frequency (RF) power transistors - GHz Technology, Inc. and Microsemi RF Products, Inc. a wholly owned subsidiary of Microsemi Corporation. Advanced Power Technology RF (APT-RF) was then formed when these two companies were merged and combined with RF products already existing within APT. This new organization offers products featuring Bipolar, VDMOS, and LDMOS technologies. All of the products are based on silicon and span the frequency range from 1MHz to 3.5GHz using voltage supplies from as low as a few volts to as high as 250V. Headquarters for APT-RF is located in Santa Clara, California with additional facilities in Montgomeryville, Pennsylvania and our corporate headquarters (Advanced Power Technology, Inc.) in Bend, Oregon. In addition, products are assembled and wafers produced in facilities operated by our production partners located in Mexico, Malaysia, Taiwan, and Austria. The Company produces products in facilities that are ISO9001 registered, space qualified, and Mil Standard approved. Our automated assembly line is among the most modern in the world assuring consistent quality and repeatable performance. Advanced Power Technology RF aggressively invests in new technology and product development. Our product roadmaps in Avionics, L-Band Radar, S-Band Radar, and pulsed LDMOS applications are intended to provide products that set the performance standard in each of these market niches. OUR MISSION AND GOALS The mission of APT-RF is to be the world leader in non-cellular/PCS high power silicon RF & microwave power transistors. -

Satellite Data Communications Link Requirements for a Proposed Flight Simulation System

Theses - Daytona Beach Dissertations and Theses 4-1994 Satellite Data Communications Link Requirements for a Proposed Flight Simulation System Gerald M. Kowalski Embry-Riddle Aeronautical University - Daytona Beach Follow this and additional works at: https://commons.erau.edu/db-theses Part of the Aviation Commons Scholarly Commons Citation Kowalski, Gerald M., "Satellite Data Communications Link Requirements for a Proposed Flight Simulation System" (1994). Theses - Daytona Beach. 266. https://commons.erau.edu/db-theses/266 This thesis is brought to you for free and open access by Embry-Riddle Aeronautical University – Daytona Beach at ERAU Scholarly Commons. It has been accepted for inclusion in the Theses - Daytona Beach collection by an authorized administrator of ERAU Scholarly Commons. For more information, please contact [email protected]. Gerald M. Kowalski A Thesis Submitted to the Office of Graduate Programs in Partial Fulfillment of the Requirements for the Degree of Master of Aeronautical Science Embry-Riddle Aeronautical University Daytona Beach, Florida April 1994 UMI Number: EP31963 INFORMATION TO USERS The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleed-through, substandard margins, and improper alignment can adversely affect reproduction. In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion. UMI® UMI Microform EP31963 Copyright 2011 by ProQuest LLC All rights reserved. This microform edition is protected against unauthorized copying under Title 17, United States Code. -

Unit - 7 & 8 DBS, Satellite Mobile and Specialized Services

www.getmyuni.com 10EC662 Unit - 7 & 8 DBS, Satellite mobile and specialized services Introduction, orbital spacing, power ratio, frequency and polarization, transponder capacity, bit rates for digital TV, satellite mobile services, USAT, RadarSat, GPS, orb communication and iridium. Text Book: 1. Satellite Communications, Dennis Roddy, 4th Edition, McGraw-Hill International edition, 2006. References books: 1. Satellite Communications, Timothy Pratt, Charles Bostian and Jeremy Allnutt, 2nd Edition, John Wiley & Sons, 2003. 2. Satellite Communication Systems Engineering, W. L. Pitchand, H. L. Suyderhoud, R. A. Nelson, 2nd Ed., Pearson Education., 2007. Page 44 www.getmyuni.com 10EC662 7.1 Introduction Satellites provide broadcast transmissions in the fullest sense of the word, since antenna footprints can be made to cover large areas of the earth. The idea of using satellites to provide direct transmissions into the home has been around for many years, and the services provided are known generally as direct broadcast satellite (DBS) services. Broadcast services include audio, television, and Internet services. 7.2 Orbital Spacing’s Orbital spacing is 9° for the high-power satellites, so adjacent satellite interference is considered nonexistent. It should be noted that although the DBS services are spaced by 9°, clusters of satellites occupy the nominal orbital positions. For example, the following satellites are located at 119°W longitude. 7.3 Power Rating Satellites primarily intended for DBS have a higher [EIRP] than for the other categories, being in the range 51 to 60 dBW. At a Regional Administrative Radio Council (RARC) meeting in 1983, the value established for DBS was 57 dBW (Mead, 2000). -

The Near Spacecraft Rf Telecommunications System

THE NEAR SPACECRAFT RF TELECOMMUNICATIONS SYSTEM The NEAR Spacecraft RF Telecommunications System Robert S. Bokulic, M. Katherine E. Flaherty, J. Robert Jensen, and Thomas R. McKnight A n X-band telecommunications system developed for the Near Earth Asteroid Rendezvous (NEAR) spacecraft represents an unmatched combination of performance, innovation, and cost-effectiveness for a deep space mission. It centers about two redundant X-band transponder systems that provide the command, telemetry, and tracking functions. Despite a tight development schedule, a significant amount of new technology has been used in the system. Included in the design are the most recent developments in transponder hardware, an X-band solid-state power amplifier (a deep space “first”), and efficient microstrip patch antennas. During spacecraft emergencies, a microstrip fanbeam antenna is used as part of a unique Earth acquisition algorithm. Postlaunch measurements have verified that in-flight performance closely matches predicted performance. (Keywords: Deep space transponders, Fanbeam antenna, NEAR, Patch antenna, Solid- state power amplifier, Telecommunications, X-band.) INTRODUCTION The telecommunications system design for a typical the asteroid 433 Eros in January 1999 and eventually deep space probe is driven by mission design. Not only go into orbit around it. does the distance between the spacecraft and Earth The spacecraft is designed for simplicity by config- vary, but the geometrical relationships among the uring the high-gain antenna (HGA) and solar panels spacecraft, Earth, Sun, and destination object(s) also so that they are nongimbaled and pointed along the vary, making the antenna pattern requirements highly same axis. This arrangement is made possible because dependent on mission design. -

Before the Federal Communications Commission Washington, D.C. 20554

Before the Federal Communications Commission Washington, D.C. 20554 In the Matter of Petition for Reconsideration of ) a decision ofthe Wireline Competition ) Bureau by the Virginia State Department ) DA 02-1123 ofEducation ) ) Federal-State joint Board on ) Universal Service ) CC Docket No. 96-45 ) Changes to the Board ofDirectors ofthe ) National Exchange Carrier Association ) CC Docket No. 97-21 Petition for R(',consideration Table of Contents Background Facts 1 Discussion 3 What is a Common Carrier? 4 Fourth Reconsideration Order 6 Autotote SEC Filings 7 Eligible Services List 8 Appeals to the SLD 9 PIA Contact Procedure 12 Summary The Virginia Department ofEducation Petitions the Wireline Competition Bureau to reconsider its Order (DA 02-1123) denying our Request for Review ofa decision by the Schools and Libraries Division, We discuss the information available on how to detennine common carrier status at the time ofour Request for Review filing and how that guidance has changed since that filing. We provide new documentation from Autotote confirming that they offer telecommunications services on a common carrier basis. Finally, we ask that this new documentation be allowed into the record under provisions ofCFR 47 Section 1.106 (I). Before the Federal Communications Commission Washington, D.C. 20554 In the Matter of: Petition for Reconsideration of ) a decision ofthe Wireline Competition ) Bureau by the Virginia State Department ) DA 02-1123 ofEducation ) ) Federal-State joint Board on ) Universal Service ) CC Docket No. 96-45 ) Changes to the Board ofDirectors ofthe ) National Exchange Carrier Association ) CC Docket No. 97-21 Petition for Reconsideration of Wireline Competition Bureau decision on Virginia Department of Education's Request for Review of Universal Service Administrator Decision In accordance with CFR Title 47 Part 1, Section 1.106, the Virginia Department ofEducation (DOE) respectfully petitions the Wireline Competition Bureau (WeB) to reconsider its decision denying DOE's Request for Review. -

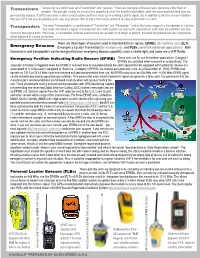

Transceivers Emergency Beacons Transponders

Transceivers Transceiver is a word made up of "transmitter" and "receiver." There are two types of transceivers, generally either fixed or portable. The portable variety are usually less powerful but has the benefit of portability, while the more powerful fixed type are permanently in place. A GPS transceiver is often used to either confirm or back up an existing satellite signal. So, in addition to the five or more satellites that your GPS unit may be picking up on, you may also be able to find a transceiver attached to a physical location on earth. Transponders The word Transponder is a combination of "Transmitter" and "Responder," and as the name suggests a transponder is a device that reads and sends a signal. A transponder on a GPS system not only reads a position on earth from the satellites, but also transmits that signal back. Practically, a transponder could be used to track the location of an object or person, provided that person has the transponder either attached or carried on him/her. There are three types of beacons used to transmit distress signals, EPIRBs (for maritime use), ELTs Emergency Beacons [Emergency Locator Transmitter](for aviation use), and PLBs (used for land-based applications). Both transceivers and transponders can be designed to have emergency beacon capability, have a strobe light, and some are a VHF Radio. Emergency Position Indicating Radio Beacon (EPIRB) These units are for use in maritime applications. Category I EPIRBs are activated either manually or automatically. The automatic activation is triggered when the EPIRB is released from its mounted outside the cabin special bracket equipped with hydrostatic release at a water depth of 3-10 feet and is designed to “float free”. -

Telephone Installations for Small Passenger Boats

§ 80.880 47 CFR Ch. I (10–1–16 Edition) (d) An on/off switch must be provided INMARSAT ship earth station meeting for the entire installation with a visual the equipment authorization rules of indication that the installation is parts 2 and 80 of this chapter. switched on. [68 FR 46973, Aug. 7, 2003] (e) The equipment must indicate the channel number, as given in the Radio § 80.881 Equipment requirements for Regulations, to which it is tuned. It ship stations. must allow the determination of the Vessels subject to subpart R of this channel number under all conditions of part must be equipped as follows: external lighting. Channel 16 must be (a) A category 1, 406.0–406.1 MHz distinctively marked. EPIRB meeting the requirements of (f) The receiver must have a manual § 80.1061; volume control and a squelch control. (b) A NAVTEX receiver meeting the (g) If the external controls are on a requirements of § 80.1101(c)(1); separate control unit and more than (c) A Search and Rescue Transponder one such control unit is provided, the meeting the requirements of one on the bridge must have priority § 80.1101(c)(6); and over the others. When there is more (d) A two-way VHF radiotelephone than one control unit, indication must meeting the requirements of be given to the other(s) that the trans- § 80.1101(c)(7). mitter is in operation. [68 FR 46973, Aug. 7, 2003] § 80.880 Vessel radio equipment. (a) Vessels operated solely within § 80.882 2182 kHz watch. -

Satellite Communications in the New Space

IEEE COMMUNICATIONS SURVEYS & TUTORIALS (DRAFT) 1 Satellite Communications in the New Space Era: A Survey and Future Challenges Oltjon Kodheli, Eva Lagunas, Nicola Maturo, Shree Krishna Sharma, Bhavani Shankar, Jesus Fabian Mendoza Montoya, Juan Carlos Merlano Duncan, Danilo Spano, Symeon Chatzinotas, Steven Kisseleff, Jorge Querol, Lei Lei, Thang X. Vu, George Goussetis Abstract—Satellite communications (SatComs) have recently This initiative named New Space has spawned a large number entered a period of renewed interest motivated by technological of innovative broadband and earth observation missions all of advances and nurtured through private investment and ventures. which require advances in SatCom systems. The present survey aims at capturing the state of the art in SatComs, while highlighting the most promising open research The purpose of this survey is to describe in a structured topics. Firstly, the main innovation drivers are motivated, such way these technological advances and to highlight the main as new constellation types, on-board processing capabilities, non- research challenges and open issues. In this direction, Section terrestrial networks and space-based data collection/processing. II provides details on the aforementioned developments and Secondly, the most promising applications are described i.e. 5G associated requirements that have spurred SatCom innovation. integration, space communications, Earth observation, aeronauti- cal and maritime tracking and communication. Subsequently, an Subsequently, Section III presents the main applications and in-depth literature review is provided across five axes: i) system use cases which are currently the focus of SatCom research. aspects, ii) air interface, iii) medium access, iv) networking, v) The next four sections describe and classify the latest SatCom testbeds & prototyping. -

Deep Space One Telecommunication Development M.I

• • SSC98-IV-l • Deep Space One Telecommunication Development M.I. Herman, S. Valas, W. Hatch, C.C. Chen, S. H. Zingales, R. P. Scaramastra, L.R. Amaro, • and M. D. Rayman Jet Propulsion Laboratory • California Institute of Technology 4800 Oak Grove Drive • Pasadena, CA 91109 m1s 161-213 818-354-8541 • [email protected] • Abstract. Deep Space One (DS1) is the first of the New Millennium Program deep space technology validation missions, to be launched October 1998. This paper focuses on the • Telecommunication Subsystem architecture, technology developments, as well as the test results. Technical factors that influenced the subsystem architecture were the ability to command the • spacecraft and downlink telemetry data in cruise and emergency situations, and the need to provide radiometric data. Additional challenges included the requirement to demonstrate new • telecommunication technology, enable the validation of other system technologies (for example solar electric propulsion, autonomous navigation, and beacon monitor operation), and at the same time utilize a single string system design. From a programmatic perspective we had to accomplish • these goals within a budget and workforce load that was at least a factor 2 less than the Mars • Pathfinder Project. The Small Deep Space Transponder (SDST), a new technology developed by Motorola, is the • heart of the Telecommunication Subsystem and is a result of a JPL multimission sponsored competitive award. The SDST provides the functionality normally associated with 4-5 individual • subassemblies at less than half the mass (2.95 kg). Another new technology to be validated on DS1 is a 2.5W Ka-band solid state amplifier developed by Lockheed Martin (under their own funding).