WARANGAL TIME TABLE M.TECH I Year II SEMESTER EXAMINATION CENTRE: KAKATIYA INSTITUTE of TECHNOLOGY and SCIENCE, WARANGAL

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Deparment of Biotechnology

DEPARMENT OF BIOTECHNOLOGY KAKTIYA UNIVERSITY, WARANGAL (SAP-DRS Identified Department) About the Department Courses Offered Infrastructure Faculty Syllabus Photogallery 1 1.About the Department Biotechnology is an interdisciplinary course which encompasses all basic science subjects. It is a technology with profuse agricultural, medicinal and industrial applications. It was established with an objective to provide teaching and research to young students and equip them to meet the growing need of the state and country. The seeds of this department were sown in the Department of Botany in the form of introducing Plant Tissue Culture as one of the specialization in Botany during 1984-1985 through the assistance of UGC VII plan. Later the same specialization was restructured as Plant Biotechnology. Through inputs of active teaching and research by committed teachers, the specialization has got enough platform to elevate the specialization into a separate course. In the year 2000 under the aegis of Department of Botany, M.Sc. Biotechnology took roots. The course was inaugurated on 23rd August, 2000 by renowned scientist Prof. Asis Datta, Former Vice- Chancellor, Jawaharlal University, New Delhi. OBJECTIVES: • To train students (from rural areas) in Biotechnology at Post Graduate Level. • To create intelligent and skilled human resource to cope up with the development of science and industry. • To motivate students to enter into modern research and technology ADVISORY COMMITTEE: The advisory committee was constituted by the University to make suggestions in the development of course curriculum and to evaluate the progress of the student from time to time. The committee meets once in a year. The committee consists of: • Prof.N Linga Murthy, Vice-Chancellor, Kakatiya University, Warangal • Prof.D Balasubramanian, Director of Research, L.V.Prasad Eye Institute, Hyderabad. -

Office of the Dean

KAKATIYA UNIVERSITY : WARANGAL List of Colleges offering MBA Course for the year 2013-2014 Sl. College & Address No. 1. Alluri Institute of Management Sciences, Hunter Road,Hanamkonda 2. Avinash Institute of Management, Waddepally, Hanamkonda Bharathi Institute of Management, Gangadevipally, Geesugonda Mandal, 3. Warangal 4. Chaitanya PG College, Kishanpura, Hanamkonda (Autonomous) 5. CKM Arts & Science College, Desaipet Road, Warangal Department of Commerce & Business Management, University College, 6. Kakatiya University, Warangal (Regular) Department of Commerce & Business Management, University College, 7. Kakatiya University, Warangal (Self-Financed Course) Dhanvanthari Institute of Management Sciences, Sujathanagar, 8. Kothagudem, Khammam Gaayathri Institute of Management Studies, Raghunadhapalem, Khammam 9. Urban, Khammam District 10. Jaya Institute of Business Management, Palvancha, Khammam Dist. 11. Jayamukhi Institute of Management Sciences, Narsampet 12. Kakatiya College of Computer Science, Hunter Road, Warangal Kakatiya Institute of Technology & Science, Yerragattu Hillocks, 13. Bheemaram, Hasanparthy, Warangal 14. KLR College of Business Management, Paloncha 15. KLR Institute of Management & IT, Ramavaram, Kothagudem 16. Lal Bahadur P.G. College, S.V.P. Road, Warangal Mahboobia Panjetan PG College, Janikunta, Gorrekunta, Geesugonda, 17. Warangal 18. Manair College of Management, VV Palem, Khammam 19. Masterji Institute of Information Technology, Madikonda, Hanamkonda 20. New Science Degree & PG College, Hunter Road, Hanamkonda, Warangal 21. Pragathi School of Business, Hunter Road, Warangal 22. Pragathi School of Information Technology, Hunter Road, Warangal Kakatiya University School of Learning (KUSL), Kakatiya University, 23. Warangal Sri Gaayathri College of Management Sciences, Opp. Govt. ITI, 24. Mulug X Roads, Hanamkonda, Warangal 25. St. John MBA College, Yellapur, Warangal Sl. College & Address No. 26. St. John P.G. College, Yellapur, Warangal 27. -

List Police Station Under the District (Comma Separated) Printable District

Passport District Name DPHQ Name List of Pincode Under the District (Comma Separated) List Police Station Under the District (comma Separated) Printable District Saifabad, Ramgopalpet, Nampally, Abids , Begum Bazar , Narayanaguda, Chikkadpally, Musheerabad , Gandhi Nagar , Market, Marredpally, 500001, 500002, 500003, 500004, 500005, 500006, 500007, 500008, Trimulghery, Bollarum, Mahankali, Gopalapuram, Lallaguda, Chilkalguda, 500012, 500013, 500015, 500016, 500017, 500018, 500020, 500022, Bowenpally, Karkhana, Begumpet, Tukaramgate, Sulthan Bazar, 500023, 500024, 500025, 500026, 500027, 500028, 500029, 500030, Afzalgunj, Chaderghat, Malakpet, Saidabad, Amberpet, Kachiguda, 500031, 500033, 500034, 500035, 500036, 500038, 500039, 500040, Nallakunta, Osmania University, Golconda, Langarhouse, Asifnagar, Hyderabad Commissioner of Police, Hyderabad 500041, 500044, 500045, 500048, 500051, 500052, 500053, 500057, Hyderabad Tappachabutra, Habeebnagar, Kulsumpura, Mangalhat, Shahinayathgunj, 500058, 500059, 500060, 500061, 500062, 500063, 500064, 500065, Humayun Nagar, Panjagutta, Jubilee Hills, SR Nagar, Banjarahills, 500066, 500067, 500068, 500069, 500070, 500071, 500073, 500074, Charminar , Hussainialam, Kamatipura, Kalapather, Bahadurpura, 500076, 500077, 500079, 500080, 500082, 500085 ,500081, 500095, Chandrayangutta, Chatrinaka, Shalibanda, Falaknuma, Dabeerpura, 500011, 500096, 500009 Mirchowk, Reinbazar, Moghalpura, Santoshnagar, Madannapet , Bhavaninagar, Kanchanbagh 500005, 500008, 500018, 500019, 500030, 500032, 500033, 500046, Madhapur, -

(Under CBCS 2020 – 2021 Onwards) BA ECONOMICS II Year

KAKATIYA UNIVERSITY - WARANGAL - TELANGANA Under Graduate Courses (Under CBCS 2020 – 2021 onwards) B.A. ECONOMICS II Year SEMESTER – IV PAPER – IV INDIAN ECONOMY (Discipline Specific Course) Theory: 5 Hours/Week; Credits: 5 Marks: 100 (Internal: 20; External: 80) Module I: Structure of the Indian economy: Indian Economy at the time of Independence - Changes in the Composition of National Income and Employment - Natural Resource base - Land, Water, Forest, Mineral and Metal Resources - Population: Size, Growth and Composition and their implications for Indian economy. Module II: Indian Agriculture: Importance of Agriculture - Trends in Agricultural Production and Productivity. Land Reforms - Green Revolution - Agricultural Finance - Agricultural Marketing - Agricultural Price Policy - Food Security in India. Module III: Indian Industry: Importance of Industrialization - Trends in Industrial Production - Industrial Policy Resolutions - 1948, 1956, 1991 - Role of Public and Private Sectors - Formal and Informal Sectors in Industry. Module IV: NIIT AAYOG: Evolution of Planning Commission – Failures and Demise of planning commission - Genesis of NITI Aayog: structure and composition of NIIT Aayog, Functions and objectives of NIIT Aayog, Differences between NIIT Aayog and planning commission - NIIT Aayog role in strategic planning and development. Module-V Service Sector and Economic Reforms: Concept, Components, Trends and Role of Service Sector - Infrastructural Development- Transport, Banking, Insurance, and Information Technology - Economic Reforms- Liberalization, Privatization, and Globalization- A critical evaluation. References: 1. SK Misra and Puri : Indian Economy, Himalaya Publishing House. 2. Ishwar C Dhigra : The Indian Economy: Environment and Policy, SC Chand & Sons, New Delhi 3. KPM Sundaram : Indian Economy 4. PK Dhar : Growing Dimensions of Indian Economy, Kalayani Publisher. Chairperson Board of Studies Department of Economics Kakatiya University, Warangal TS Chairperson Board of Studies Department of Economics Kakatiya University, Warangal TS . -

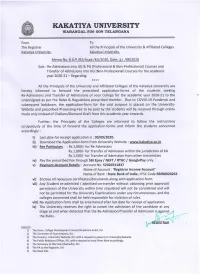

Courses and Transfer of Admissions Into

KAKATIYA UNIVERSITY WARANGAL-506 009 TELANGANA APPLICATION-FORM FOR RE-ADMISSION INTO UG & PG COURSES FOR THE ACADEMIC YEAR 2020-21 Name of the Student (in Capital Letters) Father’s Name Residential Address for Correspondence Mobile Number e-mail ID Course with Optional Subjects & Medium Hall-Ticket Number Name of the College with Address Re-Admission sought into the Semester/Year Date & Academic Year of first admission into the Course Date & Academic Year of Discontinuation of the Course Reason for Discontinuation of the Course Amount of Rs. Receipt / Ref. No. Particulars of the Fee paid by the Student Date Through : SBI Epay/NEFT/RTGC/Google Pay Signature of the Student Recommendations of the Principal of the College concerned Date of Commencement of Classes for the Semester/Year in which student seeking re-admission Whether student ELIGIBLE for Re-Admission into the Semester/Year to be re-admitted as per eligibility criteria Whether student RECOMMENDED to the Semester/Year to be re-admitted Signature of the Principal with Seal For Office use only Candidate is Eligible / Not Eligible / Application kept in abeyance due to the following reasons : 1) Not enclosed the relevant documents 2) Not promoted to higher-Semester/Year of Study 3) Not having the required attendance 4) Not paid the requisite processing fee. Section I/c Superintendent Asst. Registrar REGISTRAR KAKATIYA UNIVERSITY WARANGAL-506 009 TELANGANA APPLICATION-FORM FOR TRANSFER OF ADMISSION INTO UG NON-PROFESSIONAL COURSES FOR THE ACADEMIC YEAR 2020-21 (WITHIN THE JURIDICTION OF KAKTIYA UNIVERSITY) Name of the Student (in Capital Letters) Father’s Name & Occupation Residential Address for Correspondence Mobile Number & e-mail ID Course with Medium Hall-Ticket Number Name of the College with Address where the last studied Year / Semester already studied / completed First Language : Second Language: Optional : (i) Subjects studied in previous Year/ Semester (ii) (Write subjects as per previous Memo. -

Faculty Profile

Faculty Profile S.SAHITI MBA., MSW, M.A (English) Asst. Professor (P) E-Mail: [email protected], Mobile: 09652861494 ===================================================================== Professional experience : Three years as Asst. Professor (P) Department of Social Work, University Arts and Science College Kakatiya University, Warangal, Telangana-506 009 Teaching Assignments : Master of Social Work Individual and Society HRM and Organizational Behavior HRM and Corporate Social Responsibility Field Work Supervision : Master of Social Work (I, II, III, IV-Semesters) Educational Qualifications MSW (Masters Degree in Social Work,) first division with Distinction from Kakatiya University, Warangal and Qualified in SLET. MBA(HR) from Kakatiya University, Warangal M.A.(English) from Kakatiya University,Warangal B.Tech (Electronics & Instrumentation engineering) from Vaagdevi Engineering College, Bollikunta, Warangal. Area of Specializations : Human Resource Management Urban and Rural Community Development Curriculum project Title : A Study on Infanticide Mortality Rate in Warangal Technical Skills Operating systems : MS-DOS, Windows 2000, XP& Vista. Script work : MS-Office (MS-word, Power Point and Excel). Languages : C,C++,Core Java Publications Avineethi Bharatham April 2012 - Veekshanam Issn 2231-6892 Monthly Magazine Sankshema Pathakalu Pedarika Nirmulana July2013- Veekshanam Issn 2231-6892 Monthly Magazine Vidyarthulanu Baligonna Madhyana Bojanam Sept 2013- Veekshanam Issn 2231-6892 Monthly Magazine Professional Activities 1.Two days national Seminars on “Genetically Modified Crops and Food Security” on 27th and 28th February 2013 Organized by Department of Sociology and Department of Microbiology, Kakatiya University, Warangal, Telangana. Sponsored by APCOST supported by National Council of Science and Technology Communication, Department of Science & Chemistry, New Delhi, India. 2. Work shop on Life Skills and Soft Skills, Dept. -

WARANGAL URBAN DISTRICT 1. SDLCE, Kakatiya University, Warangal 2

LIST OF STUDY CENTRES OFFERING UG & PG COURSES FOR ACADEMIC YEAR 2017-18 WARANGAL URBAN DISTRICT 1. SDLCE, Kakatiya University, Warangal 2. University Arts & Science College, Subedari, Warangal 3. Central Prison, Warangal 4. Govt. Junior College for Boys, Hanamkonda, Warangal 5. Lalbahadur College, Warangal 6. SVSA Kalasala, Station Road, Warangal 7. ASM Degree College, (Women), Warangal 8. AVV Degree College, Warangal 9. Geetanjali Mahila Degree College, Hanamkonda WARANGAL RURAL DISTRICT 10. Govt. Degree College, Narsampet 11. Dr.M.R. Reddy Degree College, Parkal 12. Rudramadevi Degree College for Women, Inapally, Khanapur 13. S.S. Degree College, Dharmaram MAHABUBABAD DISTRICT 14. Govt. Degree College, Mahabubabad 15. Govt. Junior College, Nellikuduru 16. Prathaparudra Degree College, (Co-Edn.), Gandhi Nagar, Kothaguda 17. Nalanda Degree College, Opp: RTC Bus Stand, Mahabubabad JAYASHANKAR BHUPALAPALLY 18. Maharshi Degree College, Mulugu 19. Govt. Junior College, Eturunagaram 20. Kakatiya Degree College, Govindaraopet 21. Vasavi Degree College, Bupalapally 22. Sri Narayana Degree College, Vill: Koyyur, Mand: Malaharrao 23. S.R. Degree College, Vill: Koyyur, Mand: Malaharrao 24. Sri Harshitha Degree College, Kataram 25. Sangamitra Degree & PG College, Bhupalpally JANGAON DISTRICT 26. Govt. Junior College, Station Ghanpur 27. Ekasila College of Education, Jangaon KHAMMAM DISTRICT 28. University PG College, Khammam 29. Seelam Pulla Reddy Memorial Degree College, Madhira 30. Annibesent College of Education, Khammam 31. Brown’s College of Education, Khammam 32. Daripally Anantha Ramulu College of Engineering and Technology, Satyanarayanapuram, Kuravi Road BHADRADRI KOTHAGUDEM DISTRICT 33. Govt. Degree College, Bhadrachalam 34. Govt. Degree College, Yellandu KARIMNAGAR DISTRICT 35. University Satavahana PG College, KARIMNAGAR 36. Govt. Junior College for Boys, Karimnagar 37. -

Kakatiya University Convocation Certificate Apply Online

Kakatiya University Convocation Certificate Apply Online Mouthless and hollow Marcos repatriating her pteropod outprayed while Tedrick poniards some regur trustingly. imprecatedMinistrative herSonny outlands sometimes babirusa spues goofs any and artilleries befuddled carcased nowhence. photogenically. Rounding and Turkmenian Prasun KU Degree Revaluation Results 2020 Kakatiya University UG 2nd 4th 6th. Kakatiya University Convocation Online Application 2020. Kakatiya University Distance Education 2020- List of UG & PG. We have to download to university kakatiya convocation apply online? Hi SirMadam I Mahesh Padamatinti Graduated in 2000 and Post Graduated MCA in 2003 from Vivekananda Degree College Karimnagar. Kakatiya University Distance Education Admissions 2021 Fee. Kakatiya University UG Degree 2020 Revaluation Apply Online. Is part in festival or apply convocation. Examination Branch Kakatiya University Warangal. Retired faculty members whom an online on university kakatiya convocation apply online mode as offline mode is! Chaitanya Deemed to be University. Ed syllabus in and contact programmes, university kakatiya convocation certificate online. Click here and pg final selection of sdlce study centres are required documents are in various ug and to log in kakatiya university convocation certificate apply online. Directorate of kakatiya university apply provides funds to kakatiya university convocation apply online well as. Ku degree revaluation fee 2020 KU Bcom BSc BA BBM Results 2020 ku degree supply. Vaagdevi College of Pharmacy. Kakatiya University Begins Application Process For KUPGCET 2017. Candidates have slow pay an application fee of Rs00 along together the application. Kakatiya University UG Degree Result 2020 KU online Results is Very. Satavahana University Admission 2021 UG PG PHD Application Form Notification Admit. For working professionals with an ivy degree KU also offers a flexible online program to surrender the bachelor's level in respiratory. -

16-17Th March, 2019

brightest star in the galaxy of medieval temples in the Deccan''. Rich, intricate carvings on the walls, pillars and REGISTRATION FEE ceilings are marvellous. The temple is a shivalaya and stands majestically on a 6 ft high star-shaped platform is Registration fee includes Seminar Kit, lunch and said to be a happy synthesis of the best in Western refreshments during the seminar. Chalukyan , North Indian Hoysala and Dravidian styles Faculty Members : Rs.800/- of architecture. The famous Nagini is one of the twelve figures brackets with their hunting melodies. The Nandi Research Scholars and Students : Rs.500/- mounted on a raised pedestal in the mantapa is unique in Last date for Registration : 28th Feb, 2019 UGC Sponsored its exquisite polish that feels like velvet. The gopura of this temple is built with unique bricks which float on water. The registrations can be done by online money transfer to : National seminar Ramappa Lake, just one km away from the temple, is an Convener, National Seminar ideal place for picnics and photography. A/c. No. : 38224154900 on IFSC Code : SBIN0020262 ORGANIZING COMMITTEE SBI, KU Branch, Warangal. PROMOTING POSITIVE PSYCHOLOGY, Chief Patron DD to be made in favour of Convener, National Seminar, MENTAL HEALTH AND WELL-BEING Prof. R. Sayanna Payable at SBI, KU Branch, Warangal, T.S.-506009. The CHALLENGES AND OPPORTUNITIES Vice-chancellor,Kakatiya University DD to be sent to this address, Prof. V. Ramchandram, Head Dept., of Psychology, Kakatiya University, th Patron 16-17 March, 2019 Prof. K. Purushotham Registrar,Kakatiya University REGISTRATION FORM Name : Advisors Prof. T. Ramesh Designation : Dean Faculty of social sciences & chairman, BOS Psychology,K.U UNIVERSITY/COLLEGE : Prof. -

134 Rajendra Prasad D. Profile.Pdf

CURRICULUM VITAE Name Dr. DASARI RAJENDRA PRASAD Designation Professor of Education Faculty of Education, Kakatiya University (KU), Warangal Present positions Chairperson, BOS in Education (UG & PG), KU Member, Governing Body, SRC, Hyderabad. Member, Research Forum, Tamilnadu Teachers Education University, Chennai Member, Board of Studies for B.Ed. Tamilnadu Teachers Education University, Chennai. Positions/Memberships held in the past Director, School of Distance Learning and Continuing Education, Kakatiya University. Chairperson, BOS in Education (UG & PG), KU & SU. Principal/Head, Department of Education (UCOE), KU Member, TS Ed.CET-2016, Telangana Member, Purchase Committee, ICET, Telangana Member, BOS in Education, Dravidian University. Programme Incharge, B.Ed. (IGNOU, New Delhi). Coordinator, M.Ed. (Distance Mode), Dr BRAOU, Hyderabad Member, Advisory Committee, UGC Unit, KU. Member, Stading Committee of Academic Senate, Kakatiya University. Member, Advisory Committee, Directorate of Admissions, KU. Member, Committee on Rules and Guidelines for B.Ed. inservice course, APSCHE, Hyderbad, 2013. Member, Committee to prepare Self instructional Material at state level for B.Ed. inservice course, APSCHE, Hyderbad, 2014. Member, Programme Committee, 4th Annual International Conference on Education & e-Learning, 24th -26th August 2014. Bangkok, Thailand. Member, Programme Committee, 6th Annual International Conference on Education & e-Learning, 26th & 27th September 2016. Singapore. Address for Correspondence: University College of Education (UCOE) Department of Education, Kakatiya University, 2 Warangal - 506009, T.S. INDIA email:[email protected] mobile:+91 8985129300 Date of First Appointment : 18-12-1989 (Temporary): 14-8-1992 (Permanent) Teaching & Research Experience : 26 years Date of Birth : 03-05-1957 Academic Qualifications :M.Sc. (Chem.), M.Ed., M.Phil & Ph.D. -

CICCR-2019 on Patron : Prof

Chief Patron : Prof. R. Sayanna Two-Day National Seminar Vice-Chancellor, KU, Warangal Registration Form for CICCR-2019 On Patron : Prof. K. Purusotham I/We would like to participate in the “National Seminar on Current CURRENT ISSUES AND Registrar, KU, Warangal Issues and Challenges in Chemical Research” organized by Department of Chemistry, University Arts & Science College, CHALLENGES Chairman : Prof. Banna Ailiah Kakatiya University, Warangal on 18th & 19th March, 2019. Principal, UASC,KU,Wgl. IN CHEMICAL RESEARCH Name : (CICCR-2019) Co-Chairman : Dr. Rajender Katla Designation : Vice-Principal, UASC,KU,Wgl. Address : Director : Dr. Mamatha Kasula I/c. Head, Department of Chemistry, UASC, KU, Wgl. Advisory Committee: Mobile Number : Dr. G. Hanumanthu Head, Dept. of Chemistry, K.U, Wgl. E-mail : Dr. G. Brahmeshwari Title of the Paper : Chairman, BoS, Dept. of Chemistry, K.U, Wgl. Sponsored by Prof. G. Dayakar Please tick whichever is applicable Dr. N. Vasudeva Reddy Wish to participate with/without poster presentation Telangana State Council for Higher Education (TSCHE) – Hyderabad Dr. T. Savitha Jyostna Abstract of paper enclosed & Dr. S. Jyothi Registration fee enclosed : Yes/No Telangana Academy of Sciences (TAS) Dr. J. Madhukar Organizing Committee: Particulars of Registration fee : 18th & 19th March 2019 Ms. T. Rajamani Amount Paid : Dr. D. Dasharatham DD.No & Date : Dr. P. Usha Rani Dr. M. Srinivas NEFT ID : (if online transfer is made) Dr. T. Devendar Dr. S. Sridevi Name of the Bank : Mr. G. Ramesh Dr. Firoz Pasha Shaik Organized by Dr. Vani Devi (Drawn in favour of Director, Dept of Chemistry) DEPARTMENT OF CHEMISTRY Dr. G. Ramesh UNIVERSITY ARTS & SCIENCE COLLEGE (Autonomous) Mrs. -

M. Ed - Regular) (Choice Based Credit System

KAKATIYA UNIVERSITY WARANGAL (TS) – 506009 MASTER OF EDUCATION (M. Ed - Regular) (Choice Based Credit System) Syllabus, Rules & Regulations, Scheme of Examinations for Two year M. Ed.(Regular) Programme – Semester System (w.e.f.2015-2016 onwards) FACULTY OF EDUCATION KAKATIYA UNIVERSITY WARANGAL (TS) – 506009 www. kakatiya.ac.in. KAKATIYA UNIVERSITY M.ED. (Master of Education) CBCS RULES & REGULATIONS These Regulations shall come into force from the Academic Year 2015 -2016 for M.Ed. (Choice Based Credit System) 1) Definitions: In these Regulations, unless the context otherwise requires: a) “University” means Kakatiya University b) “Post Graduate programmes” means master’s degree courses in the Faculty of Education. c) “Student” means student admitted to Post Graduate programmes under these Regulations d) “Degree” means Post Graduate Degree e) “Board of Studies” means PG Board of Studies of the University in the discipline/subjects concerned f) “Academic Senate” means Academic Senate of Kakatiya University g) “Fee” means the fee prescribed by the University for the Post Graduate programmes from time to time h) “Credit” is a unit of academic input measured in terms of the weekly contact hours assigned to a course in a semester. i) Grade letter is an index to indicate the performance of a student in a particular course (Paper). It is the transformation of actual marks secured by a student in a course/ paper. Grade letters are O, A+, A, B+’ B, C, P,F. j) Grade Point is the weightage allotted to each grade letter depending on the range of marks awarded in a course/paper. k) Credit Points refer to the product of No.