Space-Charge-Limited Currents in Silicon Using Gold Contacts

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

P1-Extreme Amplifier by David Sorlien, Revised and Updated by Stephen Keller

Introduction to Tube Amplifier Theory: 10.02.15 Featuring the AX84 P1-eXtreme Amplifier by David Sorlien, revised and updated by Stephen Keller The P1-eX amplifier is a simple three-stage vacuum tube electric guitar amplifier. As outlined in Fig. 1, it consists of two preamp stages driving a power amp stage. Depending on the choice of output tube, this amp is can deliver between 7 and 15 watts into a 4-, 8-, or 16-ohm load. Fig. 1: P1-eX block diagram Placed between the two preamp stages is a preamp volume control. In a similar manner, the bass, middle, and treble tone controls and a master volume control are placed between the preamp and the final power amp stage. The guitar amplifier performs two primary functions: One, it amplifies the small voltages and currents produced by the guitar pickup into a signal powerful enough to drive a speaker. Two, it shapes the frequency response, tonality, and distortion characteristics of the raw guitar signal into a form pleasing to the musician. To better grasp how a guitar amplifier accomplishes these functions, let©s take a walk through the inner workings of the AX84 P1-eXtreme amp (P1-eX). For reference, there is copy of revision 06.03.16 of the schematic provided in Appendix 1 at the end of this document. To fully understand how a guitar amp works, even a simple one like the P1-eX, you must know how to read schematic diagrams, and understand what things like resistors and capacitors are. You also need some knowledge of basic algebra and electronic theory. -

The Beginner's Handbook of Amateur Radio

FM_Laster 9/25/01 12:46 PM Page i THE BEGINNER’S HANDBOOK OF AMATEUR RADIO This page intentionally left blank. FM_Laster 9/25/01 12:46 PM Page iii THE BEGINNER’S HANDBOOK OF AMATEUR RADIO Clay Laster, W5ZPV FOURTH EDITION McGraw-Hill New York San Francisco Washington, D.C. Auckland Bogotá Caracas Lisbon London Madrid Mexico City Milan Montreal New Delhi San Juan Singapore Sydney Tokyo Toronto McGraw-Hill abc Copyright © 2001 by The McGraw-Hill Companies. All rights reserved. Manufactured in the United States of America. Except as per- mitted under the United States Copyright Act of 1976, no part of this publication may be reproduced or distributed in any form or by any means, or stored in a database or retrieval system, without the prior written permission of the publisher. 0-07-139550-4 The material in this eBook also appears in the print version of this title: 0-07-136187-1. All trademarks are trademarks of their respective owners. Rather than put a trademark symbol after every occurrence of a trade- marked name, we use names in an editorial fashion only, and to the benefit of the trademark owner, with no intention of infringe- ment of the trademark. Where such designations appear in this book, they have been printed with initial caps. McGraw-Hill eBooks are available at special quantity discounts to use as premiums and sales promotions, or for use in corporate training programs. For more information, please contact George Hoare, Special Sales, at [email protected] or (212) 904-4069. TERMS OF USE This is a copyrighted work and The McGraw-Hill Companies, Inc. -

6\ M?L/ K7 Gmwy 4 I ' + /‘4 I- E 7 4-‘1 :"I'yl’‘‘‘‘ ‘N I ‘ 7'0 LP 2: J- = ' '

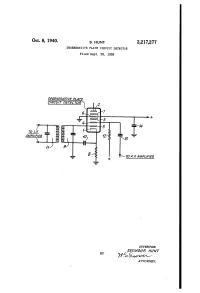

Oct.’ 8, 1940. s. HUNT £2,217,277 ' ‘ DEGENERATIVE PLATE cmcun: DETECTOR Filed Sept. '28, 19:8 DEGENERAT/VE PLATE __———_C/RCU/T DETECTOR | /2 6\ M?l/ k7 gmwy 4 i ' + /‘4 i- E 7 4-‘1 :"I'Yl’‘‘‘‘ ‘n I ‘ 7'0 LP 2: J- = ' ' a . °~ I ?|__' I ~ 70 A. E AMPLIFIER INVENTOR. Ilse MOUR HUNT BY ATTORNEY. Patented Oct. 8, 1940 2,2l7,277 UNITED STATES F ICE 2,217,277 DEGENERAT'IVE PLATE CIRCUIT DETECTOR Seymour Hunt, Jackson Heights, Long llsland, N. Y., assignor to Radio Corporation of Amer ica, a corporation of Delaware Application September 28, 1938, Serial No. 232,075 6 Claims. (Cl. 256-4237) My present invention relates to detector cir art are fully acquainted with the construction of cuits, and more particularly to degenerative plate superheterodyne receivers, it is not believed nec circuit detectors capable of substantially ampli essary to explain the construction thereof at any fying the audio voltage output thereof. greater length. The output electrode for the 5 One of the main objects of this invention is to detector circuit includes electrode 4. Preferably, provide a detector of the in?nite impedance type this electrode is a wound grid. The latter is con which includes an electronic section having a nected through load resistor 52 to the plus B negative mutual conductance characteristic terminal of any desired direct current source, which functions to amplify the audio output of such as the usual direct current energizing source 10 the detector. of a radio receiver. The coupling condenser l3 Another important object is to provide in a transmits the audio voltage, in ampli?ed form, biased plate circuit detector of the degenerative to the following audio ampli?er for ?nal repro type a negative mutual conductance section duction. -

Electrostatic Design and Characterization of a 200 Kev Photogun and Wien Spin Rotator

Old Dominion University ODU Digital Commons Electrical & Computer Engineering Theses & Dissertations Electrical & Computer Engineering Spring 2021 Electrostatic Design and Characterization of a 200 keV Photogun and Wien Spin Rotator Gabriel G. Palacios Serrano Old Dominion University, [email protected] Follow this and additional works at: https://digitalcommons.odu.edu/ece_etds Part of the Computer Engineering Commons, Electrical and Computer Engineering Commons, and the Physics Commons Recommended Citation Palacios Serrano, Gabriel G.. "Electrostatic Design and Characterization of a 200 keV Photogun and Wien Spin Rotator" (2021). Doctor of Philosophy (PhD), Dissertation, Electrical & Computer Engineering, Old Dominion University, DOI: 10.25777/mf9f-r453 https://digitalcommons.odu.edu/ece_etds/224 This Dissertation is brought to you for free and open access by the Electrical & Computer Engineering at ODU Digital Commons. It has been accepted for inclusion in Electrical & Computer Engineering Theses & Dissertations by an authorized administrator of ODU Digital Commons. For more information, please contact [email protected]. ELECTROSTATIC DESIGN AND CHARACTERIZATION OF A 200 keV PHOTOGUN AND WIEN SPIN ROTATOR by Gabriel G. Palacios Serrano B.S. August 2014, Universidad Autónoma Metropolitana, Mexico M.S. May 2017, Old Dominion University A Dissertation Submitted to the Faculty of Old Dominion University in Partial Fulfillment of the Requirements for the Degree of DOCTOR OF PHILOSOPHY ELECTRICAL AND COMPUTER ENGINEERING OLD DOMINION UNIVERSITY May 2021 Approved by: Helmut Baumgart (Director) Carlos Hernández (Member) Linda Vahala (Member) Mohammad Obeid (Member) Gon Namkoong (Member) ABSTRACT ELECTROSTATIC DESIGN AND CHARACTERIZATION OF A 200 keV PHOTOGUN AND WIEN SPIN ROTATOR Gabriel G. Palacios Serrano Old Dominion University, 2021 Director: Dr. -

ECE 340 Lecture 22 : Space Charge at a Junction

ECE 340 Lecture 22 : Space Charge at a Junction Class Outline: •Space Charge Region Things you should know when you leave… Key Questions • What is the space charge region? • What are the important quantities? • How are the important quantities related to one another? • How would bias change my analysis? M.J. Gilbert ECE 340 – Lecture 22 10/12/11 Space Charge Region To gain a qualitative understanding of the solution for the electrostatic variables we need Poisson’s equation: Most times a simple closed form solution will not be possible, so we need an approximation from which we can derive other relations. Consider the following… Doping profile is known •To obtain the electric field and potential we need to integrate. •However, we don’t know the electron and hole concentrations as a function of x. •Electron and hole concentrations are a function of the potential which we do not know until we solve Poisson’s equation. Use the depletion approximation… M.J. Gilbert ECE 340 – Lecture 22 10/12/11 Space Charge Region What does the depletion approximation tell us… 1. The carrier concentrations are assumed to be negligible compared to the net doping concentrations in the junction region. 2. The charge density outside the depletion region is taken to be identically zero. Poisson equation becomes… Must xp = xn? M.J. Gilbert ECE 340 – Lecture 22 10/12/11 Space Charge Region We are already well aware of the formation of the space charge region… The space charge region is characterized by: Na < Nd •Electrons and holes moving across the junction. -

Varian Mw 3 % H

ORNL/Sub-75/49438/2 BP n ^TfFl varian mw 3 % h NOTICE PORTIONS OF TV'!? HFTL0'' SHE M.I.HGIB'.E. IF lT~~rvnrT;irri*"rr?.--p. tf.3 iwaito'jia 1 co1;;/ -o psrrnii the broadest possible avail- ability. FINAL REPORT MILLIMETER WAVE STUDY PROGRAM u by H.R. JORY, E.L. LIEN and R.S. SYMONS ft, 0 {I Order No. Y-12 11Y-49438V j November 1975 report prepared by Varian Associates Palo Alto Microwave Tube Division 611 Hansen Way o Palo Alto, California 94303 under subcontract number 11Y-49438V ; for ' ' r>4 OAK RIDGE NATIONAL LABORATORY * ° Oak Ridge, Tennessee 37830 operated by UNION CARBIDE CORPORATION for the nrsTKIUUTiON 01? 'ijl;.;?!---''--^-'.^-^''' UNLLMIT DEPARTMENTS ENERGY FINAL REPORT MILLIMETER WAVE STUDY PROGRAM by H. R. Jory, E. L Lien and R, S. Symons - NOTICE- Urn report Mas piepated as an account, of worl; sponsored by die Untied Stales Government. Neither Die United State* not the United States Pepastment of l.nergy, tiar any of1 their employees, nnr any of then contractors. subcontractor or their employees, makes any warranty, express or implied, or assumes any legal liability oi responsibility for tlie accuracy, completeness of usefulness of any information, apparatus, product or process disclovd. or represents that its use would not mUmfe pnvately owned npjits. Order No, Y-12UY-49438V November 1975 « 0 " report prepared by Varian Associates Palo Alto Microwave Tube Division 611 Hansen Way Palo Alto, California 94303 K< under subcontract number 11Y-49438V for OAK RIDGE NATIONAL LABORATORY Oak.RitJge-J'ennessee 37830 c.-..operatedjby U N 10N CARBiDE^G0RP0RATI0N, o <J>c l . -

Cre|4|L-Feuhis ATTORNEYS Nov

Nov. 28, 1961 M. V. SULLIVAN 3,011,018 HIGHLIGHT APERTURE CORRECTION SYSTEM Filed Sept. 26, 1956 3 Sheets-Sheet 1 NVENTOR MICHAEL V.SULL VAN cre|4|l-feuHIS ATTORNEYS Nov. 28, 1961 M. W. SULLIVAN 3,011,018 HIGHLIGHT APERTURE CORRECTION SYSTEM Filed Sept. 26, 1956 3 Sheets-Sheet 2 aa- ?-s? ? O ???? S I INVENTOR MICHAEL V. SULLIVAN -a?.--77. ? ????? ??? HIS AT TORNEYS Nov. 28, 1961 M. V. SULLIVAN 3,011,018 HIGHLIGHT APERTURE CORRECTION SYSTEM Filed Sept. 26, 1956 3 Sheets-Sheet 3 NVENTOR MiCHAEL V. SULLIVAN Y Cit...!!* His A ?????? la? 3,011,018 United States Patent Office Patented Nov. 28, 1961 3,011,018 FIG. 2 illustrates the waveform of the television pic HIGHLIGHT APERTURE CORRECTION SYSTEM ture signal at various points in the aperture equalization Michael V. Sullivan, Florham Park, N.J., assignor to system shown in FIG. 1; Columbia Broadcasting System, Inc., New York, N.Y., FIG. 3 is a circuit diagram of the input and white a corporation of New York clipper portions of the system shown in FIG. 1; Filed Sept. 26, 1956, Ser. No. 612,221 FIG. 4 is ? circuit diagram of the difference ampli 7 Claims. (Cl. 178-6) fier portion of the system shown in FIG. 1; and FIG. 5 is a circuit diagram of the summing amplifier This invention relates to television, and more particu and output portions of the system shown in FIG.1. larly to a new and improved aperture equalization O Referring first to the block diagram of FIG. 1 and method and means for correcting aperture distortion in the graphic representations of the signal waveform of the highlight regions of the television picture, without FIG.2, a television picture information signal as illus increasing the high frequency noise which is inherent in trated in FIG. -

BY 7% É Arrórney Patent-Ed Nov

Nov. 24, 1942. s. HUNT 2,302,867 COMÈINED MIXER AND INTERMEDIATE FREQUENCY STAGE l Filed Oct. 25, 1941 Q/ T - l INVENToR ’ SEYMOUR BY 7% é ArróRNEY Patent-ed Nov. 24, 1942 2,302,867 . UNITED STATES PATENT OFFICE tratas@r COMBINED MIXER AND INTÉRMEDIATE FREQUENCY STAGE Seymour Hunt, Flushing, N. Y., assîgnor to Radio Corporation of America, a corporation of Dela Ware Application october 25, 1941, serial No. 416,438 8 Claims. (>Cl. 250-20) This invention is concerned with an improve ` accelerate the electron stream and to shield elec ment in radio receivers of the superheterodyne trostatically the signal control grid G4 from volt type and more particularly with a combined first age fluctuations on the oscillator anode-grid G2 detector-oscillator or mixer and intermediate fre and the output anode P. quency stage that may be used with advantage in Cl According to my invention the functions of such receivers. the several electrodes and the connections there In the present state of the art it isknown to tol of the circuit elements are modified somewhat use in superheterodyne circuits a multi-electrode ~ as will now be pointed out more particularly. In type of tube designed to perform simultaneously the circuit of Fig. 1 the grid G1 serves as the the functions of a mixer tube and of an oscillator signal control grid as well as the oscillator grid. tube. According to my present invention the ` Connected between the signal grid G1 and cath same or equivalent multi-electrode tube is made ode 'is the circuit L1-C1 which is tuned to the to perform in addition the function of interme received signal oscillations. -

Lee De Forest Claimet\He Got the Idea for His Triode ''Audion" From

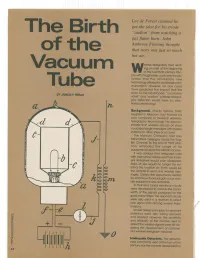

Lee de Forest claimet\he got the idea for his triode h ''audion" from wntching a gas flame bum. John Ambrose Flen#ng thought that story ·~just so much hot air. lreJess telegraphy held excit m WIng promise at the beginning of the twentieth century. Peo ~With Imagination could seethe po.. tentlal thot 'the rematkoble new technology offered forworlct1Nk:le com munfcotion. However, no one could hove predicted the impact that the soon-to-be-developed "osdllotlon volve" ond "oudlon" Wireless-telegra phy detector& wauid have on elec tronics technology. Backpouncl. Shortly before 1900, · Guglielmo Morconl had formed his own company to develop wireless telegraphy technology. He demon strated that wireless set-ups on ships eot~ld~messageswlth nearby stations on other ships or on land. t The Marconi Company hOd also j transmitted messages across the EhQ Jish Channel. By the end of 1901. Mar coni extended the range of his equipmenttospantheAtlan1tcOcean. It was obvlgus. 1hot ~raph ~MeS with subrhatlrie cables and ihelr lnber ent flmltations woUld soon disappear, Ships· at sea would no longer be iso la1ed. No locatlon on Eorth would. be too remote to send and receive mes sages. Clear1y; the opportunity existed tor enormous tiOOnciql gain once Jelio ble equlprrient was avoltable. To that end, 1Uned electrical circuits were developed to reduce the band width of the signals produced by ,the spark transrnlf'tirs. The resonont clfcults were also used in a receiver to select one signal from omong several trans missions. Slm~deslgn principles for resonont ontennas were also being explored and applied, However, the senstflvlty and reUabltlty of the devices used to ctetectthe Wireless signals were still hln cterlng the development of commer () cial wireless-telegraph nefWorks. -

Short Wave Radio

Short Wave Radio A Working Electronic Sculpture Honoring the History of Radio Please note: This radio picks up short wave stations, but for your best satisfaction it will require a little time and attention, both to learn how to operate it and to appreciate the principles and history that it embodies. You’ll find bare-bones instructions on this page and more details inside the notebook. To turn the radio on, rotate the volume control clockwise until you hear a click, then set its dial to 3 or 4. If the radio was not already turned on, you’ll have to wait about 30 seconds for its vacuum tubes to warm up. •Put on the headphones. •Set the radio’s other controls as follows: •RF Gain: Fully clockwise. •Preselector: 1 •Tuning: 20 •Fine Tuning: 5.0 (This works like a clock, only with ten “hours” instead of 12) •Regeneration: 7 (Or advance slowly clockwise from zero until just after the point you hear a louder hiss in the headphones.) •Volume: Set to a comfortable level, usually about 4. Now, slowly adjust the TUNING control back and forth looking for squeals that indicate signals. (The shortwave broadcast band with 31 meter wavelength is located between about 10 and 30 on the dial.) You’ll should find a few unless ionospheric conditions are particularly poor on this day. Leave the TUNING control set on a loud squeal. Then slowly adjust the FINE TUNING to “zero beat.” (You’ll notice as you move the dial across a signal, it starts with a high-pitched note, moving down to a low-pitched or zero note, then back up to high pitch again. -

RESEARCH for DEVELOPMENT of THIN-FILM SPACE-CHARGE-LIMITED TRIODE DEVICES (U) by Kenneth G. Aubuchon, Peter Knoll and Rainer

RESEARCH FOR DEVELOPMENT OF THIN-FILM SPACE-CHARGE-LIMITED TRIODE DEVICES (U) BY Kenneth G. Aubuchon, Peter Knoll and Rainer Zuleeg May 1967 Distribution of this report is provided in the interest of information exchange and should not be construed as endorse- ment by NASA of the material presented. Responsibility for the contents resides in the organization that prepared it. Prepared under Contract No. NAS 12-144 by: Hughes Aircraft Company Applied Solid State Research Department Newport Beach, California Electronics Research Center National Aeronautics & Space Administration RESEARCH FOR DEVELOPMENT OF THIN-FILM SPACE-CHARGE-LIMITED TRIODE DEVICES (U) BY Kenneth G. Aubuchon, Peter Knoll and Rainer Zuleeg May 1967 Prepared under Contract No. NAS 12-144 by: Hughes Air craft Company Applied Solid State Research Department Newport Beach, California for Electronics Research Center National Aeronautics & Space Administration TABLE OF CONTENTS SECTION TITLE PAGE NO: ABSTRACT ii FORE WORD iii LIST OF ILLUSTRATIONS iv I MATERIAL PREPARATION AND ANALYSIS 1 A. Introduction 1 B. Literature Survey 1 C. Experimental 3 D. Results 6 E. Discussion 13 I1 DEVICE THEORY 18 I11 DEVICE DESIGN AND FABRICATION 20 A. Mask Design 20 B. Silicon Processing 24 C. Discussion of Processing Problems 25 D. Summary of Lots Fabricated 27 E. Discussion of Yield 29 IV DEVICE EVALUATION 32 A. Correlation Between Theory and Experiment 32 B. High Frequency Performance 42 C. Modes of Operation 49 D. High Temperature Stability 54 E. Radiation Effects 54 F. Noise 62 V CONCLUSION 64 LIST OF REFERENCES 66 ABSTRACT Silicon-on- sapphire space - charge-limited triodes were de signed and fabricated. -

Sept. 17, 1935. A. H. TAYLOR 2,04,913 CIRCUIT for PRECISION CONTRO of MASTER OSCILLATORS Filed Feb

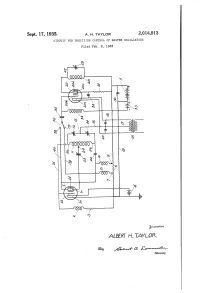

Sept. 17, 1935. A. H. TAYLOR 2,04,913 CIRCUIT FOR PRECISION CONTRO OF MASTER OSCILLATORS Filed Feb. 8, 1933 rvuorvov ALBERT H.TAYLOR &tkow, Patented Sept. 17, 1935 2014,913 UNITED STATES PATENT OFFICE 2,014,913 CIRCUIT FOR PRECISION CONTROL OF MASTER, CSCELLATORS Albert H. Taylor, Washington, D. C., assignor to Wired Radio, Inc., New York, N. Y., a corpora tion of Belaware Application February 8, 1933, Serial No. 655,829 4 Claims. (C. 250-36) My invention relates broadly to high frequency oscillation systems and more particularly to a screen grid electrode of the tetrode Oscillator and circuit for the precision control of master Oscil another of the taps at higher potential leading to lators in a high frequency OScillation System. the plate electrode. A high frequency inductance One of the objects of my invention is to pro system is connected in circuit between the control vide a simplified circuit for a high frequency grid and the anode. A pair of balancing con Oscillation system which is constructed to deliver densers is connected in series across the induc Oscillations of high frequency and efficiency. tance and a connection taken from a midpoint Another object of my invention is to provide between the condensers to a return circuit lead 0. a circuit arrangement for a high frequency OScil ing to the Cathode. Provision is made for con lator and amplifier System having a high degree necting a balance condenser between the Screen O of freedom from variation in frequency brought grid and any point in the coil system.