Getting Ready for Indium Gallium Arsenide High-Mobility Channels

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

TR-499: Indium Phosphide (CASRN 22398-80-7) in F344/N Rats And

NTP TECHNICAL REPORT ON THE TOXICOLOGY AND CARCINOGENESIS STUDIES OF INDIUM PHOSPHIDE (CAS NO. 22398-80-7) IN F344/N RATS AND B6C3F1 MICE (INHALATION STUDIES) NATIONAL TOXICOLOGY PROGRAM P.O. Box 12233 Research Triangle Park, NC 27709 July 2001 NTP TR 499 NIH Publication No. 01-4433 U.S. DEPARTMENT OF HEALTH AND HUMAN SERVICES Public Health Service National Institutes of Health FOREWORD The National Toxicology Program (NTP) is made up of four charter agencies of the U.S. Department of Health and Human Services (DHHS): the National Cancer Institute (NCI), National Institutes of Health; the National Institute of Environmental Health Sciences (NIEHS), National Institutes of Health; the National Center for Toxicological Research (NCTR), Food and Drug Administration; and the National Institute for Occupational Safety and Health (NIOSH), Centers for Disease Control and Prevention. In July 1981, the Carcinogenesis Bioassay Testing Program, NCI, was transferred to the NIEHS. The NTP coordinates the relevant programs, staff, and resources from these Public Health Service agencies relating to basic and applied research and to biological assay development and validation. The NTP develops, evaluates, and disseminates scientific information about potentially toxic and hazardous chemicals. This knowledge is used for protecting the health of the American people and for the primary prevention of disease. The studies described in this Technical Report were performed under the direction of the NIEHS and were conducted in compliance with NTP laboratory health and safety requirements and must meet or exceed all applicable federal, state, and local health and safety regulations. Animal care and use were in accordance with the Public Health Service Policy on Humane Care and Use of Animals. -

Discovering Amorphous Indium Phosphide Nanostructures with High-Temperature Ab Initio Molecular Dynamics

Discovering Amorphous Indium Phosphide Nanostructures with High-Temperature ab Initio Molecular Dynamics The MIT Faculty has made this article openly available. Please share how this access benefits you. Your story matters. Citation Zhao, Qing, Lisi Xie, and Heather J. Kulik. “Discovering Amorphous Indium Phosphide Nanostructures with High-Temperature Ab Initio Molecular Dynamics.” The Journal of Physical Chemistry C 119.40 (2015): 23238–23249. As Published http://dx.doi.org/10.1021/acs.jpcc.5b07264 Publisher American Chemical Society (ACS) Version Author's final manuscript Citable link http://hdl.handle.net/1721.1/105155 Terms of Use Article is made available in accordance with the publisher's policy and may be subject to US copyright law. Please refer to the publisher's site for terms of use. Discovering Amorphous Indium Phosphide Nanostructures with High-Temperature Ab Initio Molecular Dynamics Qing Zhao1,2, Lisi Xie1, and Heather J. Kulik1,* 1Department of Chemical Engineering, Massachusetts Institute of Technology, Cambridge, MA 02139 2Department of Mechanical Engineering, Massachusetts Institute of Technology, Cambridge, MA 02139 ABSTRACT: We employ high-temperature ab initio molecular dynamics (AIMD) as a sampling approach to discover low-energy, semiconducting, indium phosphide nanostructures. Starting from under-coordinated models of InP (e.g. a single layer of InP(111)), rapid rearrangement into a stabilized, higher-coordinate but amorphous cluster is observed across the size range considered (In3P3 to In22P22). These clusters exhibit exponential decrease in energy per atom with system size as effective coordination increases, which we define through distance-cutoff coordination number assignment and partial charge analysis. The sampling approach is robust to initial configuration choice as consistent results are obtained when alternative crystal models or computationally efficient generation of structures from sequential addition and removal of atoms are employed. -

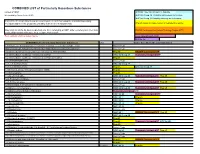

COMBINED LIST of Particularly Hazardous Substances

COMBINED LIST of Particularly Hazardous Substances revised 2/4/2021 IARC list 1 are Carcinogenic to humans list compiled by Hector Acuna, UCSB IARC list Group 2A Probably carcinogenic to humans IARC list Group 2B Possibly carcinogenic to humans If any of the chemicals listed below are used in your research then complete a Standard Operating Procedure (SOP) for the product as described in the Chemical Hygiene Plan. Prop 65 known to cause cancer or reproductive toxicity Material(s) not on the list does not preclude one from completing an SOP. Other extremely toxic chemicals KNOWN Carcinogens from National Toxicology Program (NTP) or other high hazards will require the development of an SOP. Red= added in 2020 or status change Reasonably Anticipated NTP EPA Haz list COMBINED LIST of Particularly Hazardous Substances CAS Source from where the material is listed. 6,9-Methano-2,4,3-benzodioxathiepin, 6,7,8,9,10,10- hexachloro-1,5,5a,6,9,9a-hexahydro-, 3-oxide Acutely Toxic Methanimidamide, N,N-dimethyl-N'-[2-methyl-4-[[(methylamino)carbonyl]oxy]phenyl]- Acutely Toxic 1-(2-Chloroethyl)-3-(4-methylcyclohexyl)-1-nitrosourea (Methyl-CCNU) Prop 65 KNOWN Carcinogens NTP 1-(2-Chloroethyl)-3-cyclohexyl-1-nitrosourea (CCNU) IARC list Group 2A Reasonably Anticipated NTP 1-(2-Chloroethyl)-3-cyclohexyl-1-nitrosourea (CCNU) (Lomustine) Prop 65 1-(o-Chlorophenyl)thiourea Acutely Toxic 1,1,1,2-Tetrachloroethane IARC list Group 2B 1,1,2,2-Tetrachloroethane Prop 65 IARC list Group 2B 1,1-Dichloro-2,2-bis(p -chloropheny)ethylene (DDE) Prop 65 1,1-Dichloroethane -

IEEE Spectrum Gaas

Proof #4 COLOR 8/5/08 @ 5:15 pm BP BEYOND SILICON’S ELEMENTAL LOGICIN THE QUEST FOR SPEED, KEY PARTS OF MICRO- PROCESSORS MAY SOON BE MADE OF GALLIUM ARSENIDE OR OTHER “III-V” SEMICONDUCTORS BY PEIDE D. YE he first general-purpose lithography, billions of them are routinely microprocessor, the Intel 8080, constructed en masse on the surface of a sili- released in 1974, could execute con wafer. about half a million instructions As these transistors got smaller over the T per second. At the time, that years, more could fit on a chip without rais- seemed pretty zippy. ing its overall cost. They also gained the abil- Today the 8080’s most advanced descen- ity to turn on and off at increasingly rapid dant operates 100 000 times as fast. This phe- rates, allowing microprocessors to hum along nomenal progress is a direct result of the semi- at ever-higher speeds. ALL CHRISTIEARTWORK: BRYAN DESIGN conductor industry’s ability to reduce the size But shrinking MOSFETs much beyond their of a microprocessor’s fundamental building current size—a few tens of nanometers—will be blocks—its many metal-oxide-semiconductor a herculean challenge. Indeed, at some point in field-effect transistors (MOSFETs), which act the next several years, it may become impossi- as tiny switches. Through the magic of photo- ble to make them more minuscule, for reasons WWW.SPECTRUM.IEEE.ORG SEPTEMBER 2008 • IEEE SPECTRUM • INT 39 TOMIC-LAYER DEPOSITION provides one means for coating a semiconductor wafer with a high-k aluminum oxide insulator. The Abenefit of this technique is that it offers atomic-scale control of the coating thickness without requiring elaborate equipment. -

![Crystal Structure of Hexabarium Mononitride Pentaindide,(Ba6n)[In5]](https://docslib.b-cdn.net/cover/8477/crystal-structure-of-hexabarium-mononitride-pentaindide-ba6n-in5-638477.webp)

Crystal Structure of Hexabarium Mononitride Pentaindide,(Ba6n)[In5]

Z. Kristallogr. NCS 219 (2004) 349-350 349 © by Oldenbourg Wissenschaftsverlag, München Crystal structure of hexabarium mononitride pentaindide, (Ba6N)[In5] A. Schlechte, Yu. Prots and R. Niewa* Max-Planck-Institut für Chemische Physik fester Stoffe, Nöthnitzer Str. 40, 01187 Dresden, Germany Received October 1, 2004, accepted and available on-line November 12, 2004; CSD no. 409805 Discussion Indium, when combined with alkaline-earth elements forms a va- riety of ternary nitrides. The compounds known so far may be de- scribed as built from indium clusters and octahedra of alkaline- earth cations surrounding nitride ions. In the latter cationic sub- structure the polyhedra might be isolated, vertex-, and/or edge- sharing. The variety of In arrangements extends from isolated In species in (Ca7N4)Ini.o4 [1], isolated tetrahedral units in (AI9N7)[ID4]2 (A = Ca, Sr, Ba) [2,3], trigonal bipyramidal [Ins] clusters next to [Ins] ions of more complicated geometry in (Ba38Ni8)[In5]2[In8] [4], and infinite chains in (A4N)[In2] (A = Ca, Sr) [5] and (Ca2N)In [6]. None of these metallic compounds follows Zintl-like counting. The new compound (Ba6N)[Ins] is an isotype of (¿6N)[Ga5] (A = Sr, Ba) [7]. The crystal structure of (Ba6N)tIns] is characterized as rocksalt type motif of N-centred octahedra (BaiN) and trigonal bi- pyramidal clusters [Ins]. The trigonal bipyramidal units [Ins] might be described as [Ins]7- ions, quite the same according to Zintl-type electronic counting and using the Wade-rules for closo-cluster. The isotypes (AeN)[Gas] were previously de- scribed by the formula (A2+)6(N3-)[Ga5]7~ • 2e_ based on elec- tronic structure calculations. -

Binary and Ternary Transition-Metal Phosphides As Hydrodenitrogenation Catalysts

Research Collection Doctoral Thesis Binary and ternary transition-metal phosphides as hydrodenitrogenation catalysts Author(s): Stinner, Christoph Publication Date: 2001 Permanent Link: https://doi.org/10.3929/ethz-a-004378279 Rights / License: In Copyright - Non-Commercial Use Permitted This page was generated automatically upon download from the ETH Zurich Research Collection. For more information please consult the Terms of use. ETH Library Diss. ETH No. 14422 Binary and Ternary Transition-Metal Phosphides as Hydrodenitrogenation Catalysts A dissertation submitted to the Swiss Federal Institute of Technology Zurich for the degree of Doctor of Natural Sciences Presented by Christoph Stinner Dipl.-Chem. University of Bonn born February 27, 1969 in Troisdorf (NRW), Germany Accepted on the recommendation of Prof. Dr. Roel Prins, examiner Prof. Dr. Reinhard Nesper, co-examiner Dr. Thomas Weber, co-examiner Zurich 2001 I Contents Zusammenfassung V Abstract IX 1 Introduction 1 1.1 Motivation 1 1.2 Phosphides 4 1.2.1 General 4 1.2.2 Classification 4 1.2.3 Preparation 5 1.2.4 Properties 12 1.2.5 Applications and Uses 13 1.3 Scope of the Thesis 14 1.4 References 16 2 Characterization Methods 1 2.1 FT Raman Spectroscopy 21 2.2 Thermogravimetric Analysis 24 2.3 Temperature-Programmed Reduction 25 2.4 X-Ray Powder Diffractometry 26 2.5 Nitrogen Adsorption 28 2.6 Solid State Nuclear Magnetic Resonance Spectroscopy 28 2.7 Catalytic Test 33 2.8 References 36 3 Formation, Structure, and HDN Activity of Unsupported Molybdenum Phosphide 37 3.1 Introduction -

Indium Gallium Arsenide Detectors

TELEDYNE JUDSON TECHNOLOGIES A Teledyne Technologies Company Indium Gallium Arsenide Detectors Teledyne Judson Technologies LLC 221 Commerce Drive Montgomeryville, PA 18936 USA Tel: 215-368-6900 Fax: 215-362-6107 Visit us on the web. ISO 9001 Certified www.teledynejudson.com 1/9 J22 and J23 Detector Operating Notes (0.8 to 2.6 µm) TELEDYNE JUDSON TECHNOLOGIES A Teledyne Technologies Company General Accessories The J22 and J23 series are high For a complete system, Teledyne Judson performance InGaAs detectors offers low noise transimpedance amp- operating over the spectral range lifier modules, heat sink/preamp assem- from 0.8µm to 2.6µm. These blies and temperature controllers. For detectors provide fast rise time, further details, please visit our uniformity of response, excellent website. sensitivity, and long term reliability for a wide range of applications. For Call us enhanced performance or temperature stability of response Let our team of application engineers near the cutoff wavelength, Teledyne assist you in selecting the best Judson offers a variety of thermoele detector design for your application. ctrically cooled detector options. Or visit our website for additional Applications information on all of Teledyne Judson’s products. Device Options · Gas analysis · NIR-FTIR Teledyne Judson’s standard InGaAs · Raman spectroscopy detectors, the J22 series, offers high · IR fluorescence reliability and performance in the · Blood analysis spectral range from 0.8 μm to 1.7μm. · Optical sorting In addition, the J23 series extended · Radiometry InGaAs detectors are available in · Chemical detection four cutoff options at 1.9μm, 2.2μm, · Optical communication 2.4μm and 2.6μm. Figure 1 shows the · Optical power monitoring typical response for the J22 and J23 · Laser diode monitoring series at room temperature operation. -

High Hazard Chemical Policy

Environmental Health & Safety Policy Manual Issue Date: 2/23/2011 Policy # EHS-200.09 High Hazard Chemical Policy 1.0 PURPOSE: To minimize hazardous exposures to high hazard chemicals which include select carcinogens, reproductive/developmental toxins, chemicals that have a high degree of toxicity. 2.0 SCOPE: The procedures provide guidance to all LSUHSC personnel who work with high hazard chemicals. 3.0 REPONSIBILITIES: 3.1 Environmental Health and Safety (EH&S) shall: • Provide technical assistance with the proper handling and safe disposal of high hazard chemicals. • Maintain a list of high hazard chemicals used at LSUHSC, see Appendix A. • Conduct exposure assessments and evaluate exposure control measures as necessary. Maintain employee exposure records. • Provide emergency response for chemical spills. 3.2 Principle Investigator (PI) /Supervisor shall: • Develop and implement a laboratory specific standard operation plan for high hazard chemical use per OSHA 29CFR 1910.1450 (e)(3)(i); Occupational Exposure to Hazardous Chemicals in Laboratories. • Notify EH&S of the addition of a high hazard chemical not previously used in the laboratory. • Ensure personnel are trained on specific chemical hazards present in the lab. • Maintain Material Safety Data Sheets (MSDS) for all chemicals, either on the computer hard drive or in hard copy. • Coordinate the provision of medical examinations, exposure monitoring and recordkeeping as required. 3.3 Employees: • Complete all necessary training before performing any work. • Observe all safety -

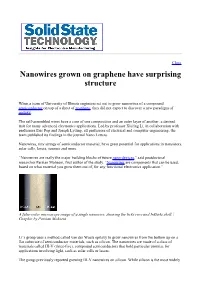

Nanowires Grown on Graphene Have Surprising Structure

Close Nanowires grown on graphene have surprising structure When a team of University of Illinois engineers set out to grow nanowires of a compound semiconductor on top of a sheet of graphene, they did not expect to discover a new paradigm of epitaxy. The self-assembled wires have a core of one composition and an outer layer of another, a desired trait for many advanced electronics applications. Led by professor Xiuling Li, in collaboration with professors Eric Pop and Joseph Lyding, all professors of electrical and computer engineering, the team published its findings in the journal Nano Letters. Nanowires, tiny strings of semiconductor material, have great potential for applications in transistors, solar cells, lasers, sensors and more. “Nanowires are really the major building blocks of future nano-devices,” said postdoctoral researcher Parsian Mohseni, first author of the study. “Nanowires are components that can be used, based on what material you grow them out of, for any functional electronics application.” A false-color microscope image of a single nanowire, showing the InAs core and InGaAs shell. | Graphic by Parsian Mohseni Li’s group uses a method called van der Waals epitaxy to grow nanowires from the bottom up on a flat substrate of semiconductor materials, such as silicon. The nanowires are made of a class of materials called III-V (three-five), compound semiconductors that hold particular promise for applications involving light, such as solar cells or lasers. The group previously reported growing III-V nanowires on silicon. While silicon is the most widely used material in devices, it has a number of shortcomings. -

Structural and Electronic Properties of Indium Rich Nitride Nanostructures

francesco ivaldi STRUCTURALANDELECTRONICPROPERTIESOF INDIUMRICHNITRIDENANOSTRUCTURES STRUCTURALANDELECTRONICPROPERTIESOFINDIUM RICHNITRIDENANOSTRUCTURES francesco ivaldi Institute of Physics Polish Academy of Science Laboratory of X-Ray and electron microscopy research Group of electron microscopy Promotor: Prof. nzw. dr hab. Piotr Dłuzewski˙ Warsaw, September 2015 Francesco Ivaldi: Structural and electronic properties of indium rich ni- tride nanostructures, III-V heterostructures investigated by TEM and connected methods, c September 2015 ABSTRACT New materials such as III-N ternary alloys are object of increasing interest in the field of micro- and nanotechnology due to their rel- evant optical and electronical properties. Those alloys are especially appealing to be used to form quantum nanostructures for various de- vice applications such as laser emitting diodes, high electron mobility transistors and solar cells. This thesis investigates the properties of InGaN and AlInN alloys with high indium content (> 25 %). TEM and STEM combined with EELS and EDX investigations have been used to correlate the struc- tural changes with the local electronic and optical properties of In- GaN quantum wells and InN quantum dots as a consequence of ther- mal processes. Annealing of InGaN quantum wells and capping of both InN quan- tum dots and quantum wells under different conditions have been investigated. Image processing techniques such as geometric phase analysis of HR-TEM images were used to reveal significant fluctua- tions in the indium distribution on a nanometric scale inside the wells. The growth parameters leading to improved photoemission proper- ties have been determined. MBE and MOCVD grown samples have been used to analyze the influence of the temperature of the quantum barrier growth on the structural and electronic properties of the samples. -

Indium Nitride Growth by Metal-Organic Vapor Phase Epitaxy

INDIUM NITRIDE GROWTH BY METAL-ORGANIC VAPOR PHASE EPITAXY By TAEWOONG KIM A DISSERTATION PRESENTED TO THE GRADUATE SCHOOL OF THE UNIVERSITY OF FLORIDA IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY UNIVERSITY OF FLORIDA 2006 Copyright 2006 by Taewoong Kim ACKNOWLEDGMENTS The author wishes first to thank his advisor, Dr. Timothy J. Anderson, for providing five years of valuable advice and guidance. Dr. Anderson always encouraged the author to approach his research from the highest scientific level. He is deeply thankful to his co-advisor, Dr. Olga Kryliouk, for her valuable guidance, sincere advice, and consistent support for the past five years. Secondly, the author wishes to thank the remaining committee members of Dr. Steve Pearton and Dr. Fan Ren for their advice and guidance The author is grateful to Scott Gapinski, the staff at Microfabritech, and Eric Lambers, the staff at the Major Analytical Instrumentation Center, especially for Auger characterization. Acknowledgement needs to be given to Sangwon Kang who worked with the author for the past year and provided valuable assistance. Thanks go to Youngsun Won for his useful discussion of quantum calculation and SEM characterization, and to Dr. Jianyun Shen for her assistance about how to use the ThermoCalc. The author wishes to thank Hyunjong Park for useful discussion and Youngseok Kim for his kindness and friendship. Most importantly, the author is grateful to Moonhee Choi, his beloved wife, for her endless support, trust, love, sacrifice and encouragement. Without her help, he would have not finished the Ph.D. course. iii The author is grateful to his mother, father, mother-in-law, father-in-law, sisters, and brother for providing love, support and guidance throughout his life. -

Organometallic Pnictogen Chemistry

Institut für Anorganische Chemie 2014 Fakultät für Chemie und Pharmazie | Sabine Reisinger aus Regensburg, geb. Scheuermayer am 15.07.1983 Studium: Chemie, Universität Regensburg Abschluss: Diplom Promotion: Prof. Dr. Manfred Scheer, Institut für Anorganische Chemie Sabine Reisinger Die vorliegende Arbeit enthält drei Kapitel zu unterschiedlichen Aspekten der metallorganischen Phosphor- und Arsen-Chemie. Zunächst werden Beiträge zur supramolekularen Chemie mit 5 Pn-Ligandkomplexen basierend auf [Cp*Fe(η -P5)] und 5 i [Cp*Fe(η - Pr3C3P2)] gezeigt, gefolgt von der Eisen-vermittelten Organometallic Pnictogen Aktivierung von P4, die zu einer selektiven C–P-Bindungsknüpfung führt, während das dritte Kapitel die Verwendung von Phosphor Chemistry – Three Aspects und Arsen als Donoratome in mehrkernigen Komplexen mit paramagnetischen Metallionen behandelt. Sabine Reisinger 2014 Alumniverein Chemie der Universität Regensburg E.V. [email protected] http://www.alumnichemie-uniregensburg.de Aspects Three – Chemistry Pnictogen Organometallic Fakultät für Chemie und Pharmazie ISBN 978-3-86845-118-4 Universität Regensburg Universitätsstraße 31 93053 Regensburg www.uni-regensburg.de 9 783868 451184 4 Sabine Reisinger Organometallic Pnictogen Chemistry – Three Aspects Organometallic Pnictogen Chemistry – Three Aspects Dissertation zur Erlangung des Doktorgrades der Naturwissenschaften (Dr. rer. nat.) der Fakultät für Chemie und Pharmazie der Universität Regensburg vorgelegt von Sabine Reisinger, geb. Scheuermayer Regensburg 2014 Die Arbeit wurde von Prof. Dr. Manfred Scheer angeleitet. Das Promotionsgesuch wurde am 20.06.2014 eingereicht. Das Kolloquium fand am 11.07.2014 statt. Prüfungsausschuss: Vorsitzender: Prof. Dr. Helmut Motschmann 1. Gutachter: Prof. Dr. Manfred Scheer 2. Gutachter: Prof. Dr. Henri Brunner weiterer Prüfer: Prof. Dr. Bernhard Dick Dissertationsreihe der Fakultät für Chemie und Pharmazie der Universität Regensburg, Band 4 Herausgegeben vom Alumniverein Chemie der Universität Regensburg e.V.