Wideband Low Distortion Unity-Gain Stable Voltage-Feedback Op Amp

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

12 Studio Equipment (898-1021)

Section12 PHOTO - VIDEO - PRO AUDIO STUDIO EQUIPMENT Allen Avionics....................................900-901 Analog Way .......................................902-908 Barco...........................................................909 CSI ........................................................910-913 Comprehensive .................................914-919 Ensemble Designs ............................920-929 Gefen ..................................................930-933 Grass Valley .......................................934-935 Horita .................................................936-949 Video Hotronics ...........................................950-953 Keywest Technology........................954-955 Knox Video.........................................956-961 Kramer................................................962-973 Link Electronics.................................974-993 Miranda ............................................994-1007 Reflecmedia....................................1008-1011 SourceBook Rosco.........................................................1012 Teranex.....................................................1013 TV One.............................................1014-1021 Obtaining information and ordering from B&H is quick and easy. When you call us, just punch in the corresponding Quick Dial number anytime during our welcome message. The Quick Dial code then directs you to the specific The professional sales associates in our order department. For Section12, Studio Equipment use Quick Dial #: 821 Professional -

Analog/SDI to SDI/Optical Converter with TBC/Frame Sync User Guide

Analog/SDI to SDI/Optical Converter with TBC/Frame Sync User Guide ENSEMBLE DESIGNS Revision 6.0 SW v1.0.8 This user guide provides detailed information for using the BrightEye™1 Analog/SDI to SDI/Optical Converter with Time Base Corrector and Frame Sync. The information in this user guide is organized into the following sections: • Product Overview • Functional Description • Applications • Rear Connections • Operation • Front Panel Controls and Indicators • Using The BrightEye Control Application • Warranty and Factory Service • Specifications • Glossary BrightEye-1 BrightEye 1 Analog/SDI to SDI/Optical Converter with TBC/FS PRODUCT OVERVIEW The BrightEye™ 1 Converter is a self-contained unit that can accept both analog and digital video inputs and output them as optical signals. Analog signals are converted to digital form and are then frame synchronized to a user-supplied video reference signal. When the digital input is selected, it too is synchronized to the reference input. Time Base Error Correction is provided, allowing the use of non-synchronous sources such as consumer VTRs and DVD players. An internal test signal generator will produce Color Bars and the pathological checkfield test signals. The processed signal is output as a serial digital component television signal in accordance with ITU-R 601 in both electrical and optical form. Front panel controls permit the user to monitor input and reference status, proper optical laser operation, select video inputs and TBC/Frame Sync function, and adjust video level. Control and monitoring can also be done using the BrightEye PC or BrightEye Mac application from a personal computer with USB support. -

4430+ Composite Analogue to SDI ADC

DTL MiniBlox™ 4430+ Composite analogue to SDI ADC Features • Analogue composite to SDI ADC • Dual high speed oversampling 11-bit ADC’s • Digital TBC and jitter filter for greater output stability • Temporal frame recursive noise reduction • Motion adaptive 3D YC separation using a 5 line comb filter • Automatic gain control Description • Differential input to eliminate common mode ‘hum’ up to 6Vp-p The 4430+ is a broadcast quality composite analogue to SDI converter. • Extremely compact and rugged It uses dual 11 bit over sampling ADCs with 5 line • Locking connector for PSU adaptive comb filtering. Temporal noise reduction and Control switches 3D motion adaptive YC separation offer the highest • Pedestal control quality conversion on the market. The unit accepts PAL, • VBI blanking NTSC and SECAM analogue inputs. The input format is • Disable AGC automatically detected. • Disable jitter filter It is housed in an extremely compact and rugged aluminium case ideally suited to both studio and portable • Enable noise reduction applications. • Enable motion adaptive YC separation www.miniblox.com Specifications Analogue input Performance Standards Composite NTSC (J, M, 4.43), PAL (B, D, G, H, I, Differential gain <1.5% M, N, Nc, 60) and SECAM (B, D, G, K, K1, L) Composite PAL, NTSC & SECAM Differential phase <0.4° Connector 75Ω BNCs Power Signal level 1V p-p nominal Voltage 6-12V DC Return loss >40dB to 5.5MHz Current 600mA at 6V CMR >6Vp-p Power connector Locking 2.5mm jack connector (centre +ve) SDI output Other Standards SMPTE 259M 270Mb/s 525/625 SDI LED Shows power and signal Connector 75Ω BNC Temperature range 0˚C to 40˚C Number 2 Dimensions 63.5mm x84mm x30mm (excluding connectors) Signal level 800mV p-p ±10% (terminated) Weight 180g Jitter <0.15UI with colour bars input Return loss >18dB to 270MHz Ordering information 4430+ Composite analogue to SDI ADC 4006 Desktop power supply with IEC320 C14 inlet 4010 1U rack mounting frame for up to 5 units including PSU We reserve the right to change technical specifications without prior notice. -

FMS6404 — Precision Composite Video Output with Sound Trap And

FMS6404 — Precision Composite October 2011 FMS6404 Precision Composite Video Output with Sound Trap and Group Delay Compensation Features Description The FMS6404 is a single composite video 5th-order Video Output with Sound Trap 7.6MHz 5th-Order Composite Video Filter . Butterworth low-pass video filter optimized for minimum . 14dB Notch at 4.425MHz to 4.6MHz for Sound Trap overshoot and flat group delay. The device contains an Capable of Handling Stereo audio trap that removes video information in a spectral location of the subsequent RF audio carrier. The group 50dB Stopband Attenuation at 27MHz on . delay compensation circuit pre-distorts the signal to CV Output compensate for the inherent receiver intermediate . > 0.5dB Flatness to 4.2MHz on CV Output frequency (IF) filter’s group delay distortion. Equalizer and Notch Filter for Driving RF Modulator In a typical application, the composite video from the with Group Delay of -180ns DAC is AC coupled into the filter. The CV input has DC- restore circuitry to clamp the DC input levels during No External Frequency Selection Components . video synchronization. The clamp pulse is derived from or Clocks the CV channel. < 5ns Group Delay on CV Output All outputs are capable of driving 2VPP, AC- or DC- . AC-Coupled Input coupled, into either a single or dual video load. A single video load consists of a series 75Ω impedance . AC- or DC-Coupled Output matching resistor connected to a terminated 75Ω line. and Group Delay Compensation . Capable of PAL Frequency for CV This presents a total of 150Ω of loading to the part. -

Preview - Click Here to Buy the Full Publication IEC 60728-5

This is a preview - click here to buy the full publication IEC 60728-5 Edition 2.0 2007-08 INTERNATIONAL STANDARD Cable networks for television signals, sound signals and interactive services – Part 5: Headend equipment INTERNATIONAL ELECTROTECHNICAL COMMISSION PRICE CODE XC ICS 33.060.40 ISBN 2-8318-9263-5 This is a preview - click here to buy the full publication – 2 – 60728-5 © IEC:2007(E) CONTENTS FOREWORD...........................................................................................................................8 INTRODUCTION...................................................................................................................10 1 Scope.............................................................................................................................11 2 Normative references .....................................................................................................13 3 Terms, definitions, symbols and abbreviations................................................................14 3.1 Terms and definitions ............................................................................................14 3.2 Symbols ................................................................................................................19 3.3 Abbreviations ........................................................................................................19 4 Methods of measurement ...............................................................................................21 4.1 Methods of measurement -

4-Channel Video Multiplexers Transmit Four Channels of Full-Frame, • One-Way Transmission of Four Real-Time, Full Frame Video Real-Time Video Over a Single fiber

GE Fiber Optic Security Video Transmitters and Receivers Overview Standard Features 4-Channel Video Multiplexers transmit four channels of full-frame, • One-way transmission of four real-time, full frame video real-time video over a single fiber. They accept monochrome and channels over one fiber color signals in NTSC and PAL formats. The multiplexers consist of • Single and multimode models available a four-channel transmitter and receiver, with both units available in standalone and rack configurations. S704V models feature • Supports all major video formats multimode operation, while S7704V models operate over one single • 640 TV lines resolution mode fiber. • 60 dB Video SNR • 8 MHz video bandwidth Exceptional Performance • Optical AGC Full-frame, real-time video transmission delivers all the video • 13 dB optical budget captured by the camera. A bandwidth of 8 MHz enable the multiplexers to transmit extremely clear, high-resolution images. FM • Operating distance up to 20 miles (32 km), depending on the modulation assures that the image quality remains high over the model full operating distance. • Standalone or rack configurations Superior Diagnostics The SMARTS™ diagnostic technology provides built-in diagnostic tools including LEDs that monitor the operating status of the video and optical signals. 4-Channel Video Multiplexer S704V and S7704V GE Specifications Security Video S704V (Multimode) S7704V (Single Mode) Channels 4 Format NTSC, PAL, SECAM, EIA, CCIR U.S. Input/Output Signal 1.0 V p-p composite T (561) 998-6100 T 888-GE-SECURITY -

Analysis of Dual-Channel Broadcast Antennas

Analysis of Dual-Channel Broadcast Antennas Myron D. Fanton, PE Electronics Research, Inc. Abstract—The design concept is discussed for slotted UHF antennas to be located on the side of the tower, then the coverage needs of that allows the combining of a high power NTSC channel with an the station must be reviewed prior to making a decision on the adjacent DTV channel assignment using a single transmission line antenna type. Slotted antenna designs have been used and antenna. extensively for directional side mounted antennas and for extremely high power (200 kW NTSC) side mounted omni- Index Terms—Antenna Array, Slot Antennas, Antenna Bandwidth. directional antennas. I. INTRODUCTION 1.10 or UHF channels in the United States, slotted antenna 1.09 designs are typically used [1]. A primary factor in their use F 1.08 has been the ability to make the support structure of the antenna an integral part of the transmitting components. Because the 1.07 frequencies assigned to UHF allow the use of relatively small 1.06 antenna elements, the removal of part of the pipe wall to create 1.05 slots was possible with only a minimal impact an its structural VSWR integrity. This resulted in an antenna with low wind-load 1.04 characteristics and was relatively economical to fabricate. 1.03 As television markets expanded, demographics changed 1.02 and competitive pressures fostered the need for UHF stations to increase their coverage. This required higher effective radiated 1.01 1.00 powers (ERP). And as higher power transmitters came to 572 574 576 578 580 582 584 market, other benefits unique to the slotted antenna design Frequency (MHz) became evident: exceptional reliability even at extremely high Figure 1: Dual Channel Antenna VSWR input power levels and more precise control over the shaping of the elevation pattern. -

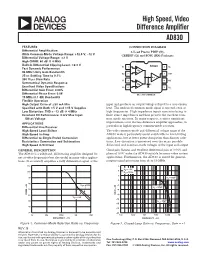

AD830 High Speed, Video Difference Amplifier Data Sheet

High Speed, Video Difference Amplifier AD830 FEATURES CONNECTION DIAGRAM Differential Amplification 8-Lead Plastic PDIP (N), Wide Common-Mode Voltage Range: +12.8 V, –12 V CERDIP (Q) and SOIC (RN) Packages Differential Voltage Range: ؎2 V High CMRR: 60 dB @ 4 MHz Built-In Differential Clipping Level: ؎2.3 V X1 1 AD830 8 V Fast Dynamic Performance P G 85 MHz Unity Gain Bandwidth M X2 2 7 OUT 35 ns Settling Time to 0.1% A = 1 360 V/ s Slew Rate Y1 3 6 NC Symmetrical Dynamic Response GM C Excellent Video Specifications Y2 4 5 VN Differential Gain Error: 0.06% ؇ Differential Phase Error: 0.08 NC = NO CONNECT 15 MHz (0.1 dB) Bandwidth Flexible Operation High Output Drive of ؎50 mA Min input and produces an output voltage referred to a user-chosen Specified with Both ؎5 V and ؎15 V Supplies level. The undesired common-mode signal is rejected, even at Low Distortion: THD = –72 dB @ 4 MHz high frequencies. High impedance inputs ease interfacing to Excellent DC Performance: 3 mV Max Input finite source impedances and thus preserve the excellent com- Offset Voltage mon-mode rejection. In many respects, it offers significant APPLICATIONS improvements over discrete difference amplifier approaches, in Differential Line Receiver particular in high frequency common-mode rejection. High Speed Level Shifter The wide common-mode and differential voltage range of the High Speed In-Amp AD830 make it particularly useful and flexible in level shifting Differential to Single-Ended Conversion applications, but at lower power dissipation than discrete solu- Resistorless Summation and Subtraction tions. -

Ultrahigh Frequency Operational Amplifier AD5539

Ultrahigh Frequency a Operational Amplifier AD5539 FEATURES CONNECTION DIAGRAM Improved Replacement for Signetics SE/NE5539 Plastic DIP (N) Package or Cerdip (Q) Package AC PERFORMANCE Gain Bandwidth Product: 1.4 GHz typ Unity Gain Bandwidth: 220 MHz typ High Slew Rate: 600 V/ms typ Full Power Response: 82 MHz typ Open-Loop Gain: 47 dB min, 52 dB typ DC PERFORMANCE All Guaranteed DC Specifications Are 100% Tested For Each Device Over Its Full Temperature Range – For All Grades and Packages VOS: 5 mV max Over Full Temperature Range OBSOLETE(AD5539S) IB: 20 mA max (AD5539J) CMRR: 70 dB min, 85 dB typ PSRR: 100 mV/V typ MIL-STD-883B Parts Available PRODUCT HIGHLIGHTS 1. All guaranteed dc specifications are 100% tested. PRODUCT DESCRIPTION 2. The AD5539 drives 50 Ω and 75 Ω loads directly. The AD5539 is an ultrahigh frequency operational amplifier de- signed specifically for use in video circuits and RF amplifiers. 3. Input voltage noise is less than 4 nV√Hz. Requiring no external compensation for gains greater than 5, it 4. Low cost RF and video speed performance. may be operated at lower gains with the addition of external 5. ±2 volt output range into a 150 Ω load. compensation. 6. Low cost. As a superior replacement for the Signetics NE/SE5539, each AD5539 is 100% dc tested to meet all of its guaranteed dc 7. Chips available. specifications over the full temperature range of the device. The high slew rate and wide bandwidth of the AD5539 provide low cost solutions to many otherwise complex and expensive high frequency circuit design problems. -

Strategies for Enhancing DC Gain and Settling Performance of Amplifiers Jie Yan Iowa State University

Iowa State University Capstones, Theses and Retrospective Theses and Dissertations Dissertations 2002 Strategies for enhancing DC gain and settling performance of amplifiers Jie Yan Iowa State University Follow this and additional works at: https://lib.dr.iastate.edu/rtd Part of the Electrical and Electronics Commons Recommended Citation Yan, Jie, "Strategies for enhancing DC gain and settling performance of amplifiers " (2002). Retrospective Theses and Dissertations. 490. https://lib.dr.iastate.edu/rtd/490 This Dissertation is brought to you for free and open access by the Iowa State University Capstones, Theses and Dissertations at Iowa State University Digital Repository. It has been accepted for inclusion in Retrospective Theses and Dissertations by an authorized administrator of Iowa State University Digital Repository. For more information, please contact [email protected]. INFORMATION TO USERS This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer. The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction. In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion. Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps. -

Channelplus Channel Injector the H511 Channel Injector Creates a New Channel to Add to Existing Television Channels

ChannelPlus Channel Injector The H511 channel injector creates a new channel to add to existing television channels. OpenHousetm modules attach from the top The H511 is designed to work with an existing installation without the need to add additional hardware 1 such as a coax panel or additional coax wiring to the video source. The H511 creates this new channel from a video signal it receives via a single CAT-5 cable connected to one of its companion m a products such as the H721 camera or H110 wall plate. 1) Hook from the top gr o r p V T 2) Swing into place A C Telephone Master Hub (4 lines linesx6phones)x 6 phones) CAT-5 video 3) Push button to lock Output 3 ChannelPlus model H616 From Expansion Telephones Two models are available: Telco Ports R RJ31X 4 T jector ) R 3 AT-5 T C R nnel In 2 T ha el via Out C TheH511HHR has the isolation required by the FCC R ann 1 ch 1HHR T (single el H51 r s mod nnel Injecto lu for a system with an antenna. Cha ChannelP 2 TheH511BID has a 5-42MHz reverse channel to support bidirectional cable systems (cable modems, pay-per-view and interactive cable). Programming the H511 Program the new channel using theProgram push button to enter channel digits into the H511. This new channel should be an unused channel. It should have no interference or Typical Installation trace of a picture - just “snow”. There must also be one unused channel both above and Connect to a camera or wall plate using onlyone method: below the selected channel to avoid interference. -

Analog Waveform Monitors

Analog Waveform Monitors 1740A Series • 1750A Series • 1760 Series Data Sheet Applications Analog Baseband Video Monitoring for Broadcast and Postproduction Applications The 1740A/1750A/1760 Series make up a family of analog video waveform/vector monitors with progressive features in support of today’s demanding television environment. Each model in the series provides improved video performance and ease of operation and incorporates application-specific features. The family includes the 1740A Series composite analog waveform/vector monitors, the 1750A Series, which adds SCH and color frame verification capabilities, and the 1760 Series for mixed-format component/composite applications. (While the 1740A and 1750A do provide basic component waveform monitoring capabilities with parade and overlay displays, only the 1760 provides full component monitoring capabilities.) 1740A Series NTSC, PAL, and dual-standard models in accessory 1700F02 portable Each series includes models for NTSC, PAL, or dual-standard NTSC/PAL cases. operation. For NTSC models, the last digit of the model number is ’0’ (1740A, 1750A, or 1760); ’1’ for PAL (1741A, 1751A, or 1761); and ’5’ for Features & Benefits dual-standard NTSC/PAL (1745A, 1755A, or 1765). The family features a common, straightforward operator interface, allowing Composite or Component Waveform Monitoring the operator to take immediate advantage of the instrument’s extensive Composite Vector Display feature set. Each operating mode provides a full set of operating controls, Picture Display clearly labeled and within easy reach. Key controls are always available, Stereo Audio Display with bezel buttons and knobs identified by intuitive on-screen labels. Time Code Phasing and Amplitude SCH and Color Framing Display Component Vector, Lightning, Diamond, and Bowtie Data Sheet Selection Guide in a production suite or outside production vehicle.