User Manual Issue 2.0.2 September 2017

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Interrupt Handling in Linux

Department Informatik Technical Reports / ISSN 2191-5008 Valentin Rothberg Interrupt Handling in Linux Technical Report CS-2015-07 November 2015 Please cite as: Valentin Rothberg, “Interrupt Handling in Linux,” Friedrich-Alexander-Universitat¨ Erlangen-Nurnberg,¨ Dept. of Computer Science, Technical Reports, CS-2015-07, November 2015. Friedrich-Alexander-Universitat¨ Erlangen-Nurnberg¨ Department Informatik Martensstr. 3 · 91058 Erlangen · Germany www.cs.fau.de Interrupt Handling in Linux Valentin Rothberg Distributed Systems and Operating Systems Dept. of Computer Science, University of Erlangen, Germany [email protected] November 8, 2015 An interrupt is an event that alters the sequence of instructions executed by a processor and requires immediate attention. When the processor receives an interrupt signal, it may temporarily switch control to an inter- rupt service routine (ISR) and the suspended process (i.e., the previously running program) will be resumed as soon as the interrupt is being served. The generic term interrupt is oftentimes used synonymously for two terms, interrupts and exceptions [2]. An exception is a synchronous event that occurs when the processor detects an error condition while executing an instruction. Such an error condition may be a devision by zero, a page fault, a protection violation, etc. An interrupt, on the other hand, is an asynchronous event that occurs at random times during execution of a pro- gram in response to a signal from hardware. A proper and timely handling of interrupts is critical to the performance, but also to the security of a computer system. In general, interrupts can be emitted by hardware as well as by software. Software interrupts (e.g., via the INT n instruction of the x86 instruction set architecture (ISA) [5]) are means to change the execution context of a program to a more privileged interrupt context in order to enter the kernel and, in contrast to hardware interrupts, occur synchronously to the currently running program. -

Faux Disk Encryption: Realities of Secure Storage on Mobile Devices August 4, 2015 – Version 1.0

NCC Group Whitepaper Faux Disk Encryption: Realities of Secure Storage On Mobile Devices August 4, 2015 – Version 1.0 Prepared by Daniel A. Mayer — Principal Security Consultant Drew Suarez — Senior Security Consultant Abstract In this paper, we discuss the challenges mobile app developers face in securing data stored on devices including mobility, accessibility, and usability requirements. Given these challenges, we first debunk common misconceptions about full-disk encryption and show why it is not sufficient for many attack scenarios. We then systematically introduce the more sophisticated secure storage techniques that are available for iOS and Android respectively. For each platform, we discuss in-depth which mechanisms are available, how they technically operate, and whether they fulfill the practical security and usability requirements. We conclude the paper with an analysis of what still can go wrong even when current best-practices are followed and what the security and mobile device community can do to address these shortcomings. Table of Contents 1 Introduction ......................................................................... 3 2 Challenges in Secure Mobile Storage .................................................. 4 3 Threat Model Considerations ......................................................... 5 4 Secure Data Storage on iOS .......................................................... 6 4.1 Fundamentals of iOS Data Protection .................................................. 7 4.2 Filesystem Encryption .............................................................. -

Linux Kernel and Driver Development Training Slides

Linux Kernel and Driver Development Training Linux Kernel and Driver Development Training © Copyright 2004-2021, Bootlin. Creative Commons BY-SA 3.0 license. Latest update: October 9, 2021. Document updates and sources: https://bootlin.com/doc/training/linux-kernel Corrections, suggestions, contributions and translations are welcome! embedded Linux and kernel engineering Send them to [email protected] - Kernel, drivers and embedded Linux - Development, consulting, training and support - https://bootlin.com 1/470 Rights to copy © Copyright 2004-2021, Bootlin License: Creative Commons Attribution - Share Alike 3.0 https://creativecommons.org/licenses/by-sa/3.0/legalcode You are free: I to copy, distribute, display, and perform the work I to make derivative works I to make commercial use of the work Under the following conditions: I Attribution. You must give the original author credit. I Share Alike. If you alter, transform, or build upon this work, you may distribute the resulting work only under a license identical to this one. I For any reuse or distribution, you must make clear to others the license terms of this work. I Any of these conditions can be waived if you get permission from the copyright holder. Your fair use and other rights are in no way affected by the above. Document sources: https://github.com/bootlin/training-materials/ - Kernel, drivers and embedded Linux - Development, consulting, training and support - https://bootlin.com 2/470 Hyperlinks in the document There are many hyperlinks in the document I Regular hyperlinks: https://kernel.org/ I Kernel documentation links: dev-tools/kasan I Links to kernel source files and directories: drivers/input/ include/linux/fb.h I Links to the declarations, definitions and instances of kernel symbols (functions, types, data, structures): platform_get_irq() GFP_KERNEL struct file_operations - Kernel, drivers and embedded Linux - Development, consulting, training and support - https://bootlin.com 3/470 Company at a glance I Engineering company created in 2004, named ”Free Electrons” until Feb. -

Linux Kernal II 9.1 Architecture

Page 1 of 7 Linux Kernal II 9.1 Architecture: The Linux kernel is a Unix-like operating system kernel used by a variety of operating systems based on it, which are usually in the form of Linux distributions. The Linux kernel is a prominent example of free and open source software. Programming language The Linux kernel is written in the version of the C programming language supported by GCC (which has introduced a number of extensions and changes to standard C), together with a number of short sections of code written in the assembly language (in GCC's "AT&T-style" syntax) of the target architecture. Because of the extensions to C it supports, GCC was for a long time the only compiler capable of correctly building the Linux kernel. Compiler compatibility GCC is the default compiler for the Linux kernel source. In 2004, Intel claimed to have modified the kernel so that its C compiler also was capable of compiling it. There was another such reported success in 2009 with a modified 2.6.22 version of the kernel. Since 2010, effort has been underway to build the Linux kernel with Clang, an alternative compiler for the C language; as of 12 April 2014, the official kernel could almost be compiled by Clang. The project dedicated to this effort is named LLVMLinxu after the LLVM compiler infrastructure upon which Clang is built. LLVMLinux does not aim to fork either the Linux kernel or the LLVM, therefore it is a meta-project composed of patches that are eventually submitted to the upstream projects. -

Singularityce User Guide Release 3.8

SingularityCE User Guide Release 3.8 SingularityCE Project Contributors Aug 16, 2021 CONTENTS 1 Getting Started & Background Information3 1.1 Introduction to SingularityCE......................................3 1.2 Quick Start................................................5 1.3 Security in SingularityCE........................................ 15 2 Building Containers 19 2.1 Build a Container............................................. 19 2.2 Definition Files.............................................. 24 2.3 Build Environment............................................ 35 2.4 Support for Docker and OCI....................................... 39 2.5 Fakeroot feature............................................. 79 3 Signing & Encryption 83 3.1 Signing and Verifying Containers.................................... 83 3.2 Key commands.............................................. 88 3.3 Encrypted Containers.......................................... 90 4 Sharing & Online Services 95 4.1 Remote Endpoints............................................ 95 4.2 Cloud Library.............................................. 103 5 Advanced Usage 109 5.1 Bind Paths and Mounts.......................................... 109 5.2 Persistent Overlays............................................ 115 5.3 Running Services............................................. 118 5.4 Environment and Metadata........................................ 129 5.5 OCI Runtime Support.......................................... 140 5.6 Plugins................................................. -

Linux GPIO: Evolution and Current State of the User

Linux GPIO: Evolution and Current State of the User API Embedded Linux Conference 2020 Bartosz Golaszewski About us ● Embedded Linux Engineering Firm ● ~40 senior engineers, coming from the semiconductor world ● HW and SW products: from concept to manufacturing ● Upstream Linux kernel development and maintenance ● Founding developers of kernelCI.org project About me ● 10 years experience ● Kernel and user-space developer ● Maintainer of libgpiod and co-maintainer of the GPIO kernel sub-system 2 A lot can change in a couple months... 3 A lot can change in a couple months... The GPIO character device has been extended with new features in linux v5.5 and final new additions before declaring it feature-complete are planned for v5.6 & v5.7. 4 A lot can change in a couple months... The GPIO character device has been extended with new features in linux v5.5 but due to shortcomings in the first version of the ABI, the existing ioctl() calls are being retired and v2 of the ABI is being introduced aiming at a release as part of linux v5.9. 5 Linux GPIO: A Lesson in user API design Embedded Linux Conference 2020 Bartosz Golaszewski Agenda 1. Current state of user API a. sysfs = bad b. Character device c. Recently added features d. GPIO aggregator 2. Upcoming overhaul a. What’s wrong? b. What’s new? c. Advice on designing good uAPI 3. libgpiod a. what’s new b. Future 7 Current state of GPIO uAPI 8 GPIO in userspace ● Writing drivers for devices using GPIOs is encouraged wherever possible, but.. -

Fabric Manager for NVIDIA Nvswitch Systems

Fabric Manager for NVIDIA NVSwitch Systems User Guide / Virtualization / High Availability Modes DU-09883-001_v0.7 | January 2021 Document History DU-09883-001_v0.7 Version Date Authors Description of Change 0.1 Oct 25, 2019 SB Initial Beta Release 0.2 Mar 23, 2020 SB Updated error handling and bare metal mode 0.3 May 11, 2020 YL Updated Shared NVSwitch APIs section with new API information 0.4 July 7, 2020 SB Updated MIG interoperability and high availability details. 0.5 July 17, 2020 SB Updated running as non-root instructions 0.6 Aug 03, 2020 SB Updated installation instructions based on CUDA repo and updated SXid error details 0.7 Jan 26, 2021 GT, CC Updated with vGPU multitenancy virtualization mode Fabric Ma nager fo r NVI DIA NVSwitch Sy stems DU-09883-001_v0.7 | ii Table of Contents Chapter 1. Overview ...................................................................................................... 1 1.1 Introduction .............................................................................................................1 1.2 Terminology ............................................................................................................1 1.3 NVSwitch Core Software Stack .................................................................................2 1.4 What is Fabric Manager?..........................................................................................3 Chapter 2. Getting Started With Fabric Manager ...................................................... 5 2.1 Basic Components...................................................................................................5 -

Documentation and Analysis of the Linux Random Number Generator

Documentation and Analysis of the Linux Random Number Generator Version: 3.6 Document history Version Date Editor Description 2.0 2018-03-21 Stephan Müller Covering kernel 4.15 Re-running all tests of chapters 6 and following on 4.15 2.1 2018-04-11 Stephan Müller Updating the test results for the reboot tests on bare metal with 50,000 reboot cycles 2.2 2018-04-11 Stephan Müller Covering kernel 4.16 2.3 2018-06-18 Stephan Müller Covering kernel 4.17 2.4 2018-08-24 Stephan Müller Covering kernel 4.18 2.5 2018-11-12 Stephan Müller Covering kernel 4.19 Updated seeding process ChaCha20 DRNG documented 2.6 2019-01-11 Stephan Müller Covering kernel 4.20 3.0 2019-04-05 Stephan Müller Covering kernel 5.0 Re-running all tests of chapters 6 and following on 5.0 3.1 2019-04-12 Stephan Müller Adding results of reboot-tests for 5.0 3.2 2019-05-17 Stephan Müller Addressing comments from BSI Covering kernel 5.1 3.3 2019-08-13 Stephan Müller Covering kernel 5.2 3.4 2019-09-26 Stephan Müller Covering kernel 5.3 3.5 2019-12-13 Stephan Müller Covering kernel 5.4 3.6 2020-04-07 Stephan Müller Covering kernel 5.5 Federal Office for Information Security Post Box 20 03 63 D-53133 Bonn Internet: https://www.bsi.bund.de © Federal Office for Information Security 2020 Document history This analysis was prepared for BSI by atsec information security GmbH. -

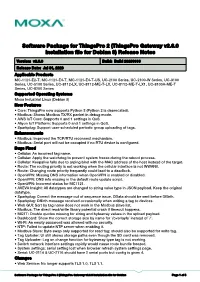

(Thingspro Gateway V2.6.0 Installation File for Debian 9) Release Notes

Software Package for ThingsPro 2 (ThingsPro Gateway v2.6.0 installation file for Debian 9) Release Notes Version: v2.6.0 Build: Build 20200616 Release Date: Jul 31, 2020 Applicable Products MC-1121-E2-T, MC-1121-E4-T, MC-1121-E4-T-US, UC-2100 Series, UC-2100-W Series, UC-3100 Series, UC-5100 Series, UC-8112-LX, UC-8112-ME-T-LX, UC-8112-ME-T-LX1, UC-8100A-ME-T Series, UC-8200 Series Supported Operating Systems Moxa Industrial Linux (Debian 9) New Features • Core: ThingsPro now supports Python 3 (Python 2 is deprecated). • Modbus: Shows Modbus TX/RX packet in debug mode. • AWS IoT Core: Supports 0 and 1 settings in QoS. • Aliyun IoT Platform: Supports 0 and 1 settings in QoS. • Sparkplug: Support user-scheduled periodic group uploading of tags. Enhancements • Modbus: Improved the TCP/RTU reconnect mechanism. • Modbus: Serial port will not be occupied if no RTU device is configured. Bugs Fixed • Cellular: An incorrect tag name. • Cellular: Apply the watchdog to prevent system freeze during the reboot process. • Cellular: Keepalive fails due to arping bind with the MAC address of the host instead of the target. • Route: The routing priority is not working when the cellular interface is not WWAN0. • Route: Changing route priority frequently could lead to a deadlock. • OpenVPN: Missing DNS information when OpenVPN is enabled or disabled. • OpenVPN: DNS info missing in the default route update script. • OpenVPN: Incorrect status for MC1121. • AVEVA Insight: All datatypes are changed to string value type in JSON payload. Keep the original datatype. -

Designing a Fast Index Format for Git

Free University of Bolzano - Bozen Bachelor Thesis Designing a Fast Index Format for Git Author: Supervisor: Thomas Gummerer Dr. Johann Gamper A thesis submitted in fulfillment of the requirements for the degree of Bachelor in Computer Science in July 2013 Contents List of Figures iv Abstract v 1 Introduction1 1.1 Motivation...................................1 1.2 Problem Description and Objectives.....................2 1.3 Organization of the Thesis...........................2 2 Related Work4 2.1 Version Control Systems............................4 2.2 Types of Version Control Systems.......................4 2.3 Git........................................5 3 A New Index for Git7 3.1 The Git Index File...............................7 3.2 Index v2.....................................8 3.3 The New Index File Format v5........................ 11 4 Implementation 15 4.1 Convert Index.................................. 15 4.2 Read Index................................... 15 4.3 Internal Implementation............................ 16 4.4 New In-memory Format............................ 18 4.5 Index Reading API............................... 19 4.6 Writing the New Index Format........................ 20 5 Discussion 22 5.1 Alternative Solutions.............................. 22 5.1.1 B-tree Format............................. 22 5.1.2 Append-only Data Structure..................... 22 5.1.3 Database Format............................ 23 5.1.4 Padded Structure............................ 23 5.2 Discussion.................................... 24 6 -

A Technical Companion to Windows Embedded Automotive 7 Proven Technology Adapted for the Automotive Industry

A Technical Companion to Windows Embedded Automotive 7 Proven technology adapted for the automotive industry Published: July 2010 For the latest information, please see: www.windowsembedded.com/auto Abstract Windows® Embedded Automotive 7―based on the newest generation of embedded operating systems from Microsoft and combining the award-winning Windows® Automotive and Microsoft® Auto platforms―is designed specifically for developing state-of-the-art, in-vehicle infotainment systems. It offers a standardized, industry-proven platform for building communication, entertainment, and service-enabled location-based solutions. This release of Windows Embedded Automotive includes a large set of integrated, tested, and flexible middleware components and tools, in addition to hundreds of components that are available with Windows® Embedded Compact 7. These components make it possible for Windows Embedded Automotive 7–based systems to scale across a broad range of automotive makes and models. By capitalizing on these tools and on the broad Microsoft partner ecosystem, suppliers can reduce development costs and speed time-to-market while extending customers’ lifestyles into the vehicles that they drive. Table of Contents TABLE OF FIGURES ................................................................................................................................... 4 OVERVIEW ............................................................................................................................................... 5 THE BUSINESS CASE FOR WINDOWS -

Power Management on DICE Desktops Chris Cooke [email protected] What I’Ll Talk About

Power Management on DICE desktops Chris Cooke [email protected] What I’ll talk about Power management What the project will deliver Main areas to look at Money Power management Basically - making computers use less electricity. Or, better - making them use it more efficiently. on PCs Formerly - APM Now - ACPI APM It was fairly simple. It worked (eventually). APM Control: APM was done at the BIOS level - the OS had little or no control. Hardware: the BIOS reckoned it knew exactly what hardware the machine had. APM worked ... ... but it wasn’t very flexible. ACPI The OS is in charge The ACPI spec defines multiple “states” - sleep states, CPU power states, etc. The OS asks the BIOS to do things ACPI Very flexible Lots more interaction between OS and BIOS Lots of chances for BIOS bugs to mess things up BIOS bugs According to Avery Pennarun: “BIOS programmers are crackheaded morons who can't implement an API correctly to save their lives.” http://www.advogato.org/person/apenwarr/ diary.html?start=167 ACPI It’s far more flexible than APM. It’s far more complicated than APM. It sometimes works ... ... sort of. ACPI on Linux It’s Open Source, so... Projects compete Projects fork and rename pm-utils, Powersave, swsusp, uswsusp, suspend, suspend2, TuxOnIce, gnome-power- manager, acpid, ... The project Just a report. Just looking at DICE desktops. Main Areas Could we make our DICE desktops... “sleep” at night? operate more efficiently when running? Sleeping at night What normally happens at night? Could it happen at other times? Or could we automatically wake up at night, perform maintenance (e.g.