Using Practical Examples in Teaching Digital Logic Design

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

75324T-Instructions.Pdf

Atomic Digital Clock with indoor/outdoor temperature, calendar and moon phase MODEL # 75324T USER GUIDE Package Contents: (1) Atomic Digital Clock (1) Wireless Outdoor Temperature Sensor (1) User Guide NOTE: A clear protective flm is applied to the LCD at the What You’ll Need: factory that must be removed prior to using this product. (8) AA Batteries Locate the clear tab and simply peel to remove. Thank you for purchasing this quality TIMEX® brand product. Please read these instructions COMPLETELY to fully understand the features and functions of this clock, and to enjoy its benefts. Make sure to keep this guide handy for future reference. To receive product information, register your product online. It's quick & easy! Log on to http://www.chaneyinstrument.com/ProductReg.aspx WHAT IS AN ATOMIC CLOCK? An Atomic clock is a timepiece that maintains accuracy up to one second per million years using the most precise method of time synchronization, radio signals. In North America, the National Institute of Standards and Technologies (NIST) operates an Atomic clock in Fort Collins, Colorado, that transmits the time codes via the radio station WWVB. Please DO NOT return product to the retail store. For technical assistance This quality TIMEX® clock includes a built-in receiver that picks up the Atomic radio signal from WWVB. To and product return information, please call technical support @ 877-221-1252 maintain the best possible reception, place the unit so that the backside faces in the general direction of Monday - Friday -- 8:00 a.m. - 4:30 p.m. CST Colorado. What's more, the IntelliTime® technology built into this clock makes for hassle-free automatic setting and resetting for daylight saving time. -

Flexible. Affordable. Built to Last. 2 It’S a Good Bet There’S Not a Single Person in America, Who’S Listened to The

D-75 STANDALONE AND D-75N NETWORKABLE DIGITAL AUDIO CONSOLES Flexible. Affordable. Built To Last. 2 It’s a good bet there’s not a single person in America, who’s listened to the radio in the last 10 years, who hasn’t heard an Audioarts radio console in action. That’s how pervasive and powerful this product line is. 3 Wheatstone D-75 STANDALONE DIGITAL AUDIO CONSOLE When it comes to radio consoles, Wheatstone’s Audioarts is Individual plug-in the de facto standard. And our D-75 is the state of the art. modules make It’s got everything you need to produce, air and manage all of installation and your programs. It’s powerful and flexible enough to please any service a breeze. engineer, simple enough that even guest talent feel at home and Configuration is as cost-effective enough to make management smile. simple as setting the front panel dipswitches Available in two frame sizes, 12 input (13 max) and 18 input concealed under the (21 max), the D-75 comes standard with 4 mic preamps and hinged meterbridge. gives you plenty of stereo busses, dual phone caller capability Digital and analog input channel daughtercards make field and a comprehensive monitor section that provides separate conversions simple and fast. Easy access logic programming feeds to control room/headphone and studio monitor outputs. dipswitches make configuration changes a snap. Plus, the D-75 gives you an output module, external power supply, two LED meter pairs, digital clock and timer, headphone Best of all, the D-75 is designed by the Wheatstone engineering jack, and built-in cue speaker (dual phone module and line team so you know its construction quality and performance selector module shown are optional). -

Please Replace the Following Pages in the Book. 26 Microcontroller Theory and Applications with the PIC18F

Please replace the following pages in the book. 26 Microcontroller Theory and Applications with the PIC18F Before Push After Push Stack Stack 16-bit Register 0120 143E 20C2 16-bit Register 0120 SP 20CA SP 20C8 143E 20C2 0703 20C4 0703 20C4 F601 20C6 F601 20C6 0706 20C8 0706 20C8 0120 20CA 20CA 20CC 20CC 20CE 20CE Bottom of Stack FIGURE 2.12 PUSH operation when accessing a stack from the bottom Before POP After POP Stack 16-bit Register A286 16-bit Register 0360 Stack 143E 20C2 SP 20C8 SP 20CA 143E 20C2 0705 20C4 0705 20C4 F208 20C6 F208 20C6 0107 20C8 0107 20C8 A286 20CA A286 20CA 20CC 20CC Bottom of Stack FIGURE 2.13 POP operation when accessing a stack from the bottom Note that the stack is a LIFO (last in, first out) memory. As mentioned earlier, a stack is typically used during subroutine CALLs. The CPU automatically PUSHes the return address onto a stack after executing a subroutine CALL instruction in the main program. After executing a RETURN from a subroutine instruction (placed by the programmer as the last instruction of the subroutine), the CPU automatically POPs the return address from the stack (previously PUSHed) and then returns control to the main program. Note that the PIC18F accesses the stack from the top. This means that the stack pointer in the PIC18F holds the address of the bottom of the stack. Hence, in the PIC18F, the stack pointer is incremented after a PUSH, and decremented after a POP. 2.3.2 Control Unit The main purpose of the control unit is to read and decode instructions from the program memory. -

Design and Implementation of a Broadband RF-DAC Transmitter for Wireless Communications

Design and Implementation of a Broadband RF-DAC Transmitter for Wireless Communications Von der Fakultät für Elektrotechnik und Informationstechnik der Rheinisch-Westfälischen Technischen Hochschule Aachen zur Erlangung des akademischen Grades eines Doktors der Ingenieurwissenschaften genehmigte Dissertation vorgelegt von Diplom-Ingenieur Niklas Zimmermann aus Münster Berichter: Universitätsprofessor Dr.-Ing. Stefan Heinen Universitätsprofessor Dr.-Ing. Gerd Ascheid Tag der mündlichen Prüfung: 1. Juli 2011 Diese Dissertation ist auf den Internetseiten der Hochschulbibliothek online verfügbar. Bibliografische Information der Deutschen Nationalbibliothek Die Deutsche Nationalbibliothek verzeichnet diese Publikation in der Deutschen Nationalbibliografie; detaillierte bibliografische Daten sind im Internet über http://dnb.d-nb.de abrufbar. ISBN 978-3-8439-0042-3 D 82 (Diss. RWTH Aachen University, 2011) © Verlag Dr. Hut, München 2011 Sternstr. 18, 80538 München Tel.: 089/66060798 www.dr.hut-verlag.de Die Informationen in diesem Buch wurden mit großer Sorgfalt erarbeitet. Dennoch können Fehler nicht vollständig ausgeschlossen werden. Verlag, Autoren und ggf. Übersetzer übernehmen keine juristische Verantwortung oder irgendeine Haftung für eventuell verbliebene fehlerhafte Angaben und deren Folgen. Alle Rechte, auch die des auszugsweisen Nachdrucks, der Vervielfältigung und Verbreitung in besonderen Verfahren wie fotomechanischer Nachdruck, Fotokopie, Mikrokopie, elektronische Datenaufzeichnung einschließlich Speicherung und Übertragung auf weitere Datenträger sowie Übersetzung in andere Sprachen, behält sich der Autor vor. 1. Auflage 2011 To the memory of my father, Gebhard Zimmermann Acknowledgment First of all, I want to thank Prof. Dr.-Ing. Stefan Heinen. This thesis would not have been possible without him, as he gave me the opportunity to work on this exciting topic and shared his rich experience in the field of RF and analog circuit and system design with me. -

Electronic LED Digital Clock Model:CX-808 User Manual

Electronic LED Digital Clock Model:CX-808 User Manual Operation: (1) Butting (2) Setting Of Time and Date: 1- Under normal situation, press SET to begin the setting of date and time, and you will see the hour and minute displays showing the year with flash at the same time; 2- Press MODIFY to change year (if you don’t want to change the flashing number, do not press modify, the following steps are in the same way); press flash on month display, and then change the month by press MODIFY; press SHIFT to move the flash on day display, and then change the day by pressing MODIFY. During the process of setting, the week follows the date changing automatically; 3- Press SHIFT again, the date disappears and the hour flashes, then change the hour by pressing MODIFY; press SHIFT to more the flash or minute display, and then change the minute by pressing MODIFY. 4- Press SET again to resume the normal situation. (3) 12 and 24 hour mode, under normal situation, press MODIFY for 3 second to switch between 12 and 24-hour mode. (4) Hour Notice Setting: Under normal situation press MODIFY to open or close the hour notice function, and you will see the indicator on or off. (5) Setting Of Alarm: 1- Under normal situation, press ALARM to view the set alarm time, the alarm indicator light is bright. When you see “A1” on the temperature display position, it means what you see on time display is the first group of alarm time. If the time display shows”-:--“it means this group of alarm is workable when it shows time, press MODIFY to switch between workable and unworkable. -

DIGITAL WALL CLOCK with Indoor Temp and Calendar

DIGITAL WALL CLOCK OVERVIEW POWER UP ALARM SETTING 1. Insert 1-AA battery into the clock. • Hold the ALM button to enter Alarm Settings. 2. Configure basic settings. • Press the +/HR or - ºF/ºC button to adjust values. Alarm & Snooze SETTINGS • Press the ALM button to confirm and move to the DIGITAL WALL CLOCK AM or PM Indicators Indicator • Hold the SET button to enter the Settings Menu. next item or exit. with Indoor Temp and Calendar Time Display • Press the +/HR or - ºF/ºC button to adjust values. QUICK START GUIDE Month | Date Indoor • Press the SET button to confirm and move to the Display Temperature ACTIVATE | DEACTIVATE ALARM Weekday Display next item or exit. Display (°F/°C) • Press the ALM button to activate or deactivate the alarm. The Alarm Indicator will display when active. Settings Menu Order: • 12/24 Hour Time Format Note: The alarm will automatically be activated after • Hour setting a new alarm time. • Minutes Buttons • Year SNOOZE • Month • When the alarm sounds, press the SNZ button to • Date silence the alarm for 5 minutes. The Alarm and Mounting Hole Snooze Indicators will flash. Note: The Weekday will set automatically as Year, Month, and Date are set correctly. • Press any button except SNZ to stop the alarm for 24 hours. Pull Out Battery Stand Compartment Model: WT-8002U FAHRENHEIT | CELSIUS • This is a crescendo alarm that will sound for 120 • Press the - ºF/ºC button to select Fahrenheit or seconds if not deactivated. DC:050818 Celsius temperature display. Full Manual can be found under the Support Tab here: http://bit.ly/WT-8002U Page | 2 Page | 3 Page | 4 POSITIONING YOUR CLOCK WE’RE HERE TO HELP! WARRANTY INFO FCC STATEMENT This equipment has been tested and found to comply with the limits for a Class • Use the Mounting Hole on the back for placement on a wall. -

11-R55e PARTS LIST/CLK-55

AAAUDIOARTSUDIOARTSUDIOARTSUDIOARTS EEENGINEERINGNGINEERINGNGINEERINGNGINEERING RRR---555555EEEE RRRADIOADIOADIOADIO CCCONSOLEONSOLEONSOLEONSOLE ENGINEERED BY WHEATSTONE, this latest This console has been designed for EASY analog radio on-air console from Audioarts is a installation and maintenance: a tabletop mount fully modular, straightforward design aimed at board with flip-up meterbridge for direct access stations with tight budgets but no desire to to I/O connectors (DB-25 multipin) and logic compromise on audio standards. programming dipswitches, it has connectorized The R-55e delivers high performance audio faders and ON/OFF switches, gold contact bus with all the basic features you need for 24/7 on- connectors, electronic switching, and solid state air use: 8, 12 or 21 input faders plus one caller, illumination—the R-55e is a rugged performer control room and studio monitoring, stereo well suited for day-in and day-out operation. Program and Audition busses (plus two mono IF YOU’RE LOOKING TO UPGRADE, or simply outputs), opto-isolated mic and machine logic, shopping for a basic analog on-air mixer from a built-in timer, talkback, cue and headphone company you can trust, check out the R-55e— functions. Two VU meter pairs (Program and the console both engineers and accountants can Switched) keep clear track of level settings. agree on! 600 Industrial Drive, New Bern, North Carolina, USA 28562 copyright © 2004 by Wheatstone Corporation www.audioarts.net / sales @ wheatstone.com tel 252-638-7000 / fax 252-635-4857 R-55e Audio Console TECHNICAL Guide July 2004 INSTALLATION and POWER Installation and Power Unpacking the Console The R-55e console is shipped as two packages. -

Digital Clock Distributor Dcd-400, Dcd-St2, and Dcd-Cim General Description and Specifications

TELECOM TMSL 097-40000-55 SOLUTIONS Issue 2: Nov 94 DIGITAL CLOCK DISTRIBUTOR DCD-400, DCD-ST2, AND DCD-CIM GENERAL DESCRIPTION AND SPECIFICATIONS CONTENTS PAGE Tables Page 1. GENERAL . 1 A. Card Quantities (Maximum) . 6 B. Modular Mounting Panel Output Kits . 11 2. INTRODUCTION . 2 C. System Specifications . 16 D. Card Specifications . 18 3. DESCRIPTION . 3 A. Master Shelf . 3 B. Input Reference Signals . 3 1. GENERAL C. DCD-ST2 and DCD-400 . 3 D. DCD-CIM . 4 1.01 This practice provides descriptions, specifica- E. System Expansion . 5 tions, and typical applications for the Digital Clock F. Output Panels . 10 Distributor (DCD) family of products. G. System Power . 12 H. System Diagnostics and Protection 1.02 This practice has been reissued due to editori- Switching . 12 al changes. No change bars are used. 4. APPLICATIONS . 12 1.03 Information common to the DCD-ST2 and A. DCD Applications . 12 DCD-400 Systems is referenced as “DCD”. The B. SCIU Applications . 13 DCD-ST2 is referred to as the “ST2” System, and the DCD-400 as the “400” System. Information unique 5. SPECIFICATIONS . 16 to the DCD-CIM System is referenced as “CIM”. Un- less otherwise specified by direct reference, other in- Figures formation is common to all systems. 1. DCD-ST2 Master Shelf . 7 1.04 The Synchronization Monitor System (SMS) 2. DCD-400 Master Shelf . 8 may be installed in the DCD Systems to implement 3. DCD-CIM Master Shelf . 8 DS1 performance monitoring. For details regarding 4. DCD System Configuration . 9 the installation and operation of the SMS option, in- 5. -

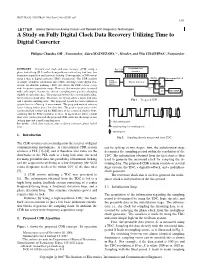

A Study on Fully Digital Clock Data Recovery Utilizing Time to Digital Converter

IEICE TRANS. ELECTRON., VOL.E90–C, NO.6 JUNE 2007 1311 LETTER Special Section on Analog Circuits and Related SoC Integration Technologies A Study on Fully Digital Clock Data Recovery Utilizing Time to Digital Converter Philipus Chandra OH†, Nonmember, Akira MATSUZAWA†a), Member, and Win CHAIVIPAS†, Nonmember SUMMARY Conventional clock and data recovery (CDR) using a phase locked loop (PLL) suffers from problems such as long lock time, low frequency acquisition and harmonic locking. Consequently, a CDR system using a time to digital converter (TDC) is proposed. The CDR consists of simple arithmetic calculation and a TDC, allowing a fully digital real- ization. In addition, utilizing a TDC also allows the CDR to have a very wide frequency acquisition range. However, deterministic jitter is caused with each sample, because the system’s sampling time period is changing slightly at each data edge. The proposed system does not minimize jitter, but it tolerates small jitter. Therefore, the system offers a faster lock time Fig. 1 Proposed CDR. and a smaller sampling error. This proposed system has been verified on system level in a Verilog-A environment. The proposed method achieves faster locking within just a few data bits. The peak to peak jitter of the recovered clock is 60 ps and the RMS jitter of the recovered clock is 30 ps, assuming that the TDC resolution is 10 ps. In applications where a small jitter error can be tolerated, the proposed CDR offers the advantage of fast locking time and a small sampling error. key words: clock data recovery, time to digital converter, phase locked loop 1. -

Clocks Brochure

Master, Wired, and Wireless Time Systems Table of Contents MASTER CLOCKS...................................................1 WIRED CLOCKS......................................................13 Bogen BCMA Master Clocks........................................2 Bogen 2-Wire System.................................................14 Receiving Accurate Time from NTP Server...............3-4 Bogen 2-Wire System Advantages.............................15 Master Clock Setup..................................................5-8 2-Wire System: One Run Line Drawing......................16 BCMA Series Master Clock.......................................8-9 2-Wire System: Multiple Runs Line Drawing..............17 The Bogen Advantage..............................................10 Bogen Sync-Wire System............................................18 BCMA Controlling Third Party Wired System............11 Sync-Wire System Line Drawing.................................19 Wireless BCMA Synchronizing...................................12 Bogen Sync-Wire System Advantages........................20 BCAM Analog.............................................................21 BCBD Digital..........................................................22-23 BCMA Series Master Clock....................................24-25 Accessories.................................................................26 WIRELESS CLOCKS................................................27 Bogen Wireless System..............................................28 Bogen Wireless System Advantages...........................29 -

Valcom Wired Digital Clock V-D11025B, V-D11040B, V-D2425B, V-D2440B, V-2425B-6, and V-D2440B-6

Installation Manual V10.5 Valcom Wired Digital Clock V-D11025B, V-D11040B, V-D2425B, V-D2440B, V-2425B-6, and V-D2440B-6 Valcom, Inc. P. 540-563-2000 5614 Hollins Road F. 540-362-9800 Roanoke, VA 24019 www.valcom.com Current as of February 2017 USA Valcom, Inc. P. 540-563-2000 5614 Hollins Road F. 540-362-9800 Roanoke, VA 24019 www.valcom.com USA Valcom Digital Series 2-Wire and 3-Wire Clocks Table of Contents Table of Contents 2 Important Safety Instructions 3 Wall Mount Installation 4 - 10 Flag Mount Installation 11 - 19 Double Mount Installation 20 - 28 Adjustable Jumper Settings 29 Inputs System Side - 2-Wire Digital Communication 30 - 3-Wire Synchronous (Sync-Wire) Communication 110VAC 31 Clock Side - Sync-Wire 32-35 Outputs 36 Manual Controls 37-43 Reading the Display 44 Frequently Asked Questions 45 Available with V-D110XXB models only Troubleshooting 46 Warranty 47 Manuals may change without prior notice 2 Valcom, Inc. P. 540-563-2000 Valcom, Inc. P. 540-563-2000 5614 Hollins Road F. 540-362-9800 5614 Hollins Road F. 540-362-9800 Roanoke, VA 24019 www.valcom.com Roanoke, VA 24019 www.valcom.com USA USA Important Safety Instructions VERY IMPORTANT: KNOW YOUR COMMUNICATION PROTOCOL The Valcom V-D110XXB Digital clocks are designed to support various 3-wire (sync-wire) communication protocols. To run each protocol properly, the clock requires the correct wiring format. It is very important that you only follow the wiring instructions appropriate to your clock’s communication protocol. Using the wrong wiring format may damage the clock. -

Digital Electronics: Logic and Clocks

DIGITAL ELECTRONICS: LOGIC AND CLOCKS LAB 9 INTRO: INTRODUCTION TO DISCRETE DIGITAL LOGIC, MEMORY, AND CLOCKS GOALS In this experiment, we will learn about the most basic elements of digital electronics, from which more complex circuits, including computers, can be constructed. Proficiency with new equipment and approaches: o Logic gates, memory circuits, digital clocks o Combining components & Boolean logic DEFINITIONS Duty cycle – percentage of time during one cycle that a system is active (+5V in the case of digital logic) Truth table – table that shows all possible input combinations and the resulting outputs of digital logic components Flip-flop - a circuit that has two stable states and can be used to store state information. Logic gates – a physical device that implements some Boolean logic operation DIGITAL CIRCUITS - GENERAL In almost all experiments in the physical sciences, the signals that represent physical quantities start out as analog waveforms. To display and analyze the information contained in these signals, they most often are converted into digital data. Often this is done inside a commercial instrument such as an oscilloscope or a lock-in amplifier, which is then connected to a computer through a digital interface. In other cases, data acquisition cards are added to a computer chassis, allowing analog signals to be input directly to the computer. Scientists usually buy their data acquisition equipment rather than build it, so they usually don’t have to know too much about the digital circuitry that makes it work. Almost all data are eventually analyzed digitally with a computer. Analog information can be translated into digital form by a device called an Analog-to-Digital Converter (A/D converter or ADC).