The ENIAC: the Grandfather of All Computers

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Women in Computing History

Women in Computing History Denise Gfirer ACM-W0) Co-Chair EMD Consulting Scotts Valley, California 95066 USA <[email protected]> Introduction Exciting inventions, innovative technology, human interac- tion, and intriguing politics fill computing history. However, the recorded history is mainly composed of male achieve- ments and involvements, even though women have played substantial roles. This situation is not unusual. Most science fields are notorious for excluding, undervaluing, or over- looking the accomplishments of their female scientists [1, 16, 17, 22]. As J.A.N. Lee points out, it is up to the histori- ans and others to remedy this imbalance (see this issue [14]). Some steps have been taken towards this goal through pub- lishing biographies on women in technology [2, 5, 6, 8, 10, 12, 13, 18, 20, 21, 23, 24], also see this issue [7], and through honoring the pioneers with various awards such as the GHC'97 Pioneering Awards(z) (Figure 1), the WITI Hall of Fame(3), and the AWC Lovelace Award(n). A few online sites Figure 1: Computer Science Pioneer Celebration, at the Grace Hopper contain biographies of women in technology, shown in Table Celebration of Women in Computing '97. Left to right: (Fran Allen, Ruzena Bajcsy, Adele Mildred Koss, Denise Gtirer, Anita Borg, Jean 1 below. However, even with these resources, many women Jennings Bartik, Judy Levenson Clapp, Thelma Estrin, Joyce Currie Little who have contributed significantly to computer science are (Courtesy Institute for Women in Technology, Palo Alto, California) still to be discovered. preprogrammed software for needed tasks (in particular word processing, email, and database access). -

Oral History of Captain Grace Hopper

Oral History of Captain Grace Hopper Interviewed by: Angeline Pantages Recorded: December, 1980 Naval Data Automation Command, Maryland CHM Reference number: X5142.2009 © 1980 Computer History Museum Table of Contents BACKGROUND HISTORY ...........................................................................................................3 1943-1949: MARK I, II, AND III COMPUTERS AT HARVARD....................................................6 1949-1964: ECKERT AND MAUCHLY, UNIVAC, AND THE ONE-PASS COMPILER ................7 The Need for User-Friendly Languages ..................................................................................10 DEMANDS FOR THE FUTURE..................................................................................................12 Application Processors, Database Machines, Distributed Processing ....................................12 Demand for Programmers and System Analysts ....................................................................14 The Value and Cost of Information..........................................................................................14 The Navy’s Dilemma: Micros and Software Creation..............................................................15 The Murray Siblings: Brilliant Communicators.........................................................................18 Common Sense and Distributed Computing ...........................................................................19 BACK TO 1943-1949: HOWARD AIKEN....................................................................................21 -

Women in Computing

History of Computing CSE P590A (UW) PP190/290-3 (UCB) CSE 290 291 (D00) Women in Computing Katherine Deibel University of Washington [email protected] 1 An Amazing Photo Philadelphia Inquirer, "Your Neighbors" article, 8/13/1957 2 Diversity Crisis in Computer Science Percentage of CS/IS Bachelor Degrees Awarded to Women National Center for Education Statistics, 2001 3 Goals of this talk ! Highlight the many accomplishments made by women in the computing field ! Learn their stories, both good and bad 4 Augusta Ada King, Countess of Lovelace ! Translated and extended Menabrea’s article on Babbage’s Analytical Engine ! Predicted computers could be used for music and graphics ! Wrote the first algorithm— how to compute Bernoulli numbers ! Developed notions of looping and subroutines 5 Garbage In, Garbage Out The Analytical Engine has no pretensions whatever to originate anything. It can do whatever we know how to order it to perform. It can follow analysis; but it has no power of anticipating any analytical relations or truths. — Ada Lovelace, Note G 6 On her genius and insight If you are as fastidious about the acts of your friendship as you are about those of your pen, I much fear I shall equally lose your friendship and your Notes. I am very reluctant to return your admirable & philosophic 'Note A.' Pray do not alter it… All this was impossible for you to know by intuition and the more I read your notes the more surprised I am at them and regret not having earlier explored so rich a vein of the noblest metal. -

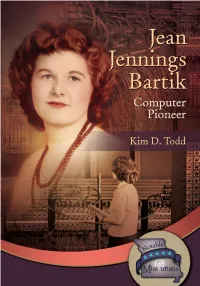

Computer Pioneer / Kim Todd

Copyright © 2015 Truman State University Press, Kirksville, Missouri, 63501 All rights reserved tsup.truman.edu Cover art: Betty Jean Jennings, ca. 1941; detail of ENIAC, 1946. Cover design: Teresa Wheeler Library of Congress Cataloging-in-Publication Data Todd, Kim D., author. Jean Jennings Bartik : computer pioneer / Kim Todd. pages cm—(Notable Missourians) Summary: “As a young girl in the 1930s, Jean Bartik dreamed of adventures in the world beyond her family’s farm in northwestern Missouri. After college, she had her chance when she was hired by the U.S. Army to work on a secret project. At a time when many people thought women could not work in technical fields like science and mathematics, Jean became one of the world’s first computer programmers. She helped program the ENIAC, the first successful stored-program computer, and had a long career in the field of computer science. Thanks to computer pioneers like Jean, today we have computers that can do almost anything.”—Provided by publisher. Audience: Ages 10-12. Audience: Grades 4 to 6. Includes bibliographical references and index. ISBN 978-1-61248-145-6 (library binding : alk. paper)—ISBN 978-1-61248-146-3 (e-book) 1. Bartik, Jean--Juvenile literature. 2. Women computer scientists—United States—Biography—Juvenile literature. 3. Computer scientists— United States—Biography—Juvenile literature. 4. Women computer programmers— United States—Biography—Juvenile literature. 5. Computer programmers—United States—Biography—Juvenile literature. 6. ENIAC (Computer)—History—Juvenile literature. 7. Computer industry—United States—History—Juvenile literature. I. Title. QA76.2.B27T63 2015 004.092--dc23 2015011360 No part of this work may be reproduced or transmitted in any format by any means without written permission from the publisher. -

Working on ENIAC: the Lost Labors of the Information Age

Working on ENIAC: The Lost Labors of the Information Age Thomas Haigh www.tomandmaria.com/tom University of Wisconsin—Milwaukee & Mark Priestley www.MarkPriestley.net This Research Is Sponsored By • Mrs L.D. Rope’s Second Charitable Trust • Mrs L.D. Rope’s Third Charitable Trust Thanks for contributions by my coauthors Mark Priestley & Crispin Rope. And to assistance from others including Ann Graf, Peter Sachs Collopy, and Stephanie Dick. www.EniacInAction.com CONVENTIONAL HISTORY OF COMPUTING www.EniacInAction.com The Battle for “Firsts” www.EniacInAction.com Example: Alan Turing • A lone genius, according to The Imitation Game – “I don’t have time to explain myself as I go along, and I’m afraid these men will only slow me down” • Hand building “Christopher” – In reality hundreds of “bombes” manufactured www.EniacInAction.com Isaacson’s “The Innovators” • Many admirable features – Stress on teamwork – Lively writing – References to scholarly history – Goes back beyond 1970s – Stresses role of liberal arts in tech innovation • But going to disagree with some basic assumptions – Like the subtitle! www.EniacInAction.com Amazon • Isaacson has 7 of the top 10 in “Computer Industry History” – 4 Jobs – 3 Innovators www.EniacInAction.com Groundbreaking for “Pennovation Center” Oct, 2014 “Six women Ph.D. students were tasked with programming the machine, but when the computer was unveiled to the public on Valentine’s Day of 1946, Isaacson said, the women programmers were not invited to the black tie event after the announcement.” www.EniacInAction.com Teams of Superheroes www.EniacInAction.com ENIAC as one of the “Great Machines” www.EniacInAction.com ENIAC Life Story • 1943: Proposed and approved. -

Programming Women: Gender at the Birth of the Computing Age

Feras 1 Programming Women: Gender at the Birth of the Computing Age Allie Feras ID#: 1914546 Honors in History Honors Capstone Advisor: Kimberly Sim 29 April 2010 In the spring of 1946, the public got its first glimpse of the Electronic Numerical Integrator and Computer (ENIAC) at a press demonstration of a ballistics trajectory Feras 2 problem created by Frances Elizabeth Snyder Holberton and Betty Jean Bartik, who had labored all night in preparation. However, when stories of the first electronic computer, which was faster than any existing analog computer, made their way into the morning papers neither woman received any credit. Instead, reporters focused on the ENIAC’s male inventors, John Mauchly and J. Presper Eckert, who had built the machine to keep up with the demand World War II had created for faster and faster computation of firing tables to be used on the front. The omission of these women was the beginning of a long history in which women’s contributions to computing were marginalized. Holberton, a graduate of the University of Pennsylvania who had previously worked as a statistician for The Farm Journal , and Bartik, a graduate of Northwest Missouri State Teachers College in math and English, were among a group of women who were the first to program an electronic computer. 1 These women, all of whom had at least some mathematics experience, were drawn into the war effort to work compute firing tables by hand and were later assigned to the ENIAC where they shaped this newly created technological field. Although the ENIAC, housed at the Moore School of Engineering at the University of Pennsylvania, had been classified, when the war ended the “electronic brain” captured the public’s imagination and the computer age began. -

Oral History Interview with Frances E. Holberton

An Interview with FRANCES E. HOLBERTON OH 50 Conducted by James Ross on 14 April 1983 Charles Babbage Institute Center for the History of Information Processing University of Minnesota, Minneapolis Copyright, Charles Babbage Institute 1 Frances E. Holberton Interview 14 April 1983 Abstract Holberton discusses her education from 1940 through the 1960s and her experiences in the computing field. These include work with the Eckert-Mauchly Computer Corporation, David Taylor Model Basin, and the National Bureau of Standards. She discusses her perceptions of cooperation and competition between members of these organizations and the difficulties she encountered as a woman. She recounts her work on ENIAC and LARC, her design of operating systems, and her applications programming. 2 FRANCES E. HOLBERTON INTERVIEW DATE: April 14, 1983 INTERVIEWER: James Ross LOCATION: Potomac, Maryland ROSS: This is a tape-recorded interview with Betty Holberton in her home conducted by the Charles Babbage Institute and I'm Jim Ross. Betty, how did you get into information processing, and how well did your previous education prepare you for what you found? HOLBERTON: Well, information processing was not even conceived of as a discipline actually at the time I got into it. Originally, my family were scientis ts and teachers--mathematics, physics, astronomy. I was fortunate enough to go to a very good prep school, George School, which is a coeducational Friends boarding school in Bucks County and got a good founding in essentially the thinking process. I received a scholarship in the University of Pennsylvania and looked for a job. However, when I was in college I was told to major in mathematics. -

Doing Mathematics on the ENIAC. Von Neumann's and Lehmer's

Doing Mathematics on the ENIAC. Von Neumann's and Lehmer's different visions.∗ Liesbeth De Mol Center for Logic and Philosophy of Science University of Ghent, Blandijnberg 2, 9000 Gent, Belgium [email protected] Abstract In this paper we will study the impact of the computer on math- ematics and its practice from a historical point of view. We will look at what kind of mathematical problems were implemented on early electronic computing machines and how these implementations were perceived. By doing so, we want to stress that the computer was in fact, from its very beginning, conceived as a mathematical instru- ment per se, thus situating the contemporary usage of the computer in mathematics in its proper historical background. We will focus on the work by two computer pioneers: Derrick H. Lehmer and John von Neumann. They were both involved with the ENIAC and had strong opinions about how these new machines might influence (theoretical and applied) mathematics. 1 Introduction The impact of the computer on society can hardly be underestimated: it affects almost every aspect of our lives. This influence is not restricted to ev- eryday activities like booking a hotel or corresponding with friends. Science has been changed dramatically by the computer { both in its form and in ∗The author is currently a postdoctoral research fellow of the Fund for Scientific Re- search { Flanders (FWO) and a fellow of the Kunsthochschule f¨urMedien, K¨oln. 1 its content. Also mathematics did not escape this influence of the computer. In fact, the first computer applications were mathematical in nature, i.e., the first electronic general-purpose computing machines were used to solve or study certain mathematical (applied as well as theoretical) problems. -

To Give WITI Members Some Perspective, Jean and Timothy

OLYMPIC PLAZA 11500 Olympic Blvd., Suite 400 Los Angeles, CA 90064 (818) 788-9484 To give WITI Members some perspective, Jean and Timothy Bartik revisited how the six "Women of the ENIAC," WITI Hall of Fame Inductees Kay Antonelli, Jean Bartik, Betty Holberton, Marlyn Meltzer, Frances Spence and Ruth Teitelbaum, fit the criteria for induction into the WITI Hall of Fame in 2005. All the Women of the ENIAC were already inducted to the WITI Hall of Fame in 1997. WITI audaciously asked the Bartiks, as a writing exercise, to fill in the nomination form once again. They graciously agreed to take the WITI challenge with pride. Below are the questions from the 2005 Nomination Form and the responses from Jean and Timothy. WITI Hall of Fame Criteria and Required Questions Hall of Fame recipients include women who have made outstanding contributions based on one or more of the following criteria: 1. Directly made an exceptional contribution to the advancement of science and/or technology. 2. Facilitated and created programs that motivate young women to choose careers in science and technology. 3. Enabled and encouraged other scientific and technical women to advance in their careers 4. Created scientific or technological innovations, which promote environmental harmony, support humanitarian endeavors or improve the human condition. Based on the above recipient criteria, please answer the following questions. Answering these questions is required. Please give thorough and complete answers to questions below. 1. Based on the criteria above, which of these criteria best describes the outstanding contributions of the nominee and why? The Women of the ENIAC, Kay Antonelli, Jean Bartik, Betty Holberton, Marlyn Meltzer, Frances Spence and Ruth Teitelbaum, directly made a contribution to the advancement of science and technology by developing the first programs or software for the first electronic computer, the ENIAC, in the mid 1940s. -

Making Programming Masculine 6

Making Programming Masculine 6 NATHAN ENSMENGER I n the April 1967 issue of Cosmopolitan magazine, sandwiched between “ The Bachelor Girls of Japan ” and “ A Dog Speaks: Why a Girl Should Own a Pooch, ” there appeared a curious little essay entitled simply “ The Computer Girls.” As the article explained, these were the female “ computer programmers ” who taught the dazzling new “ miracle machines” called computers “ what to do and how to do it. ” There were already more than 20,000 women working as com- puter programmers in the United States, argued the article ’ s author, Lois Mandel, and there was an immediate demand for 20,000 more. Not only could a talented “ computer girl” command as much $20,000 a year, but the opportunities for women in computing were effectively “ unlimited. ” The rapid expansion of the computer industry meant that “ sex discrimination in hiring ” was unheard of, Mandel confi dently declared, and anyone with aptitude — male or female, college educated or not — could succeed in the fi eld. And not only were women in computing treated as equals, but they actually had many advantages over their male colleagues. Programming was “ just like planning a dinner, ” Mandel quoted the noted computer scientist Dr. Grace Hopper as saying, “ You have to plan ahead and schedule everything so it ’ s ready when you need it. Programming requires patience and the ability to handle detail. Women are ‘ naturals ’ at computer programming ” [1] . It would be easy to dismiss “ The Computer Girls ” as a fl uff piece, a half - hearted attempt by Cosmopolitan to capitalize on contemporary interest in the computer revolution. -

The Women of ENIAC

The Women of ENIAC W. BARKLEY FRITZ A group of young women college graduates involved with the EFJIAC are identified. As a result of their education, intelligence, as well as their being at the right place and at the right time, these young women were able to per- form important computer work. Many learned to use effectively “the machine that changed the world to assist in solving some of the important scientific problems of the time. Ten of them report on their background and experi- ences. It is now appropriate that these women be given recognition for what they did as ‘pioneers” of the Age of Computing. introduction any young women college graduates were involved in ties of some 50 years ago, you will note some minor inconsiskn- NI[ various ways with ENIAC (Electronic Numerical Integra- cies, which arc to be expected. In order to preserve the candor and tor And Computer) during the 1942-195.5 period covering enthusiasm of these women for what they did and also to provide ENIAC’s pre-development, development, and 10-year period of today’s reader and those of future generations with their First-hand its operational usage. ENIAC, as is well-known, was the first accounts, I have attempted to resolve only the more serious incon- general purpose electronic digital computer to be designed, built, sistencies. Each of the individuals quoted, however, has been and successfully used. After its initial use for the Manhattan Proj- given an opportunity to see the remarks of their colleagues and to ect in the fall of 194.5 and its public demonstration in February modify their own as desired. -

John W. Mauchly Papers Ms

John W. Mauchly papers Ms. Coll. 925 Finding aid prepared by Holly Mengel. Last updated on April 27, 2020. University of Pennsylvania, Kislak Center for Special Collections, Rare Books and Manuscripts 2015 September 9 John W. Mauchly papers Table of Contents Summary Information....................................................................................................................................3 Biography/History..........................................................................................................................................4 Scope and Contents....................................................................................................................................... 6 Administrative Information........................................................................................................................... 7 Related Materials........................................................................................................................................... 8 Controlled Access Headings..........................................................................................................................8 Collection Inventory.................................................................................................................................... 10 Series I. Youth, education, and early career......................................................................................... 10 Series II. Moore School of Electrical Engineering, University of Pennsylvania.................................