C-Based Hardware Design of Imdct Accelerator for Ogg Vorbis Decoder

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

CD/DVD Player

4-277-895-11(1) CD/DVD Player Operating Instructions DVP-NS638P DVP-NS648P © 2011 Sony Corporation Precautions Notes about the discs Safety • To keep the disc clean, handle WARNING To prevent fire or shock hazard, do the disc by its edge. Do not touch not place objects filled with the surface. Dust, fingerprints, or To reduce the risk of fire or liquids, such as vases, on the scratches on the disc may cause electric shock, do not expose apparatus. it to malfunction. this apparatus to rain or moisture. Installing To avoid electrical shock, do • Do not install the unit in an not open the cabinet. Refer inclined position. It is designed servicing to qualified to be operated in a horizontal personnel only. position only. The mains lead must only be • Keep the unit and discs away changed at a qualified from equipment with strong service shop. magnets, such as microwave Batteries or batteries ovens, or large loudspeakers. installed apparatus shall not • Do not place heavy objects on be exposed to excessive heat the unit. such as sunshine, fire or the like. Lightning For added protection for this set • Do not expose the disc to direct CAUTION during a lightning storm, or when it sunlight or heat sources such as is left unattended and unused for hot air ducts, or leave it in a car The use of optical instruments with long periods of time, unplug it parked in direct sunlight as the this product will increase eye from the wall outlet. This will temperature may rise hazard. As the laser beam used in prevent damage to the set due to considerably inside the car. -

Blackberry QNX Multimedia Suite

PRODUCT BRIEF QNX Multimedia Suite The QNX Multimedia Suite is a comprehensive collection of media technology that has evolved over the years to keep pace with the latest media requirements of current-day embedded systems. Proven in tens of millions of automotive infotainment head units, the suite enables media-rich, high-quality playback, encoding and streaming of audio and video content. The multimedia suite comprises a modular, highly-scalable architecture that enables building high value, customized solutions that range from simple media players to networked systems in the car. The suite is optimized to leverage system-on-chip (SoC) video acceleration, in addition to supporting OpenMAX AL, an industry open standard API for application-level access to a device’s audio, video and imaging capabilities. Overview Consumer’s demand for multimedia has fueled an anywhere- o QNX SDK for Smartphone Connectivity (with support for Apple anytime paradigm, making multimedia ubiquitous in embedded CarPlay and Android Auto) systems. More and more embedded applications have require- o Qt distributions for QNX SDP 7 ments for audio, video and communication processing capabilities. For example, an infotainment system’s media player enables o QNX CAR Platform for Infotainment playback of content, stored either on-board or accessed from an • Support for a variety of external media stores external drive, mobile device or streamed over IP via a browser. Increasingly, these systems also have streaming requirements for Features at a Glance distributing content across a network, for instance from a head Multimedia Playback unit to the digital instrument cluster or rear seat entertainment units. Multimedia is also becoming pervasive in other markets, • Software-based audio CODECs such as medical, industrial, and whitegoods where user interfaces • Hardware accelerated video CODECs are increasingly providing users with a rich media experience. -

Detail Streaming Support Protocols

Encore+ User Guide Detail Streaming Support Protocols Supported Audio Codecs Supported Container Formats • MP3 • WAV • AAC • M4A • FLAC • OGG • LPCM/WAV/AIFF • AIFF • ALAC Supported Protocols • WMA, WMA9 • SHOUTcast • Ogg Vorbis • HTTPS Supported Playlist • WMA streaming • ASX • RTSP/SDP • M3U • PLS • WPL 43 Detail Audio Codec Support Encore+ User Guide Supported MP3 encoding parameters • Sampling rates [kHz]: 32, 44.1, 48 • Resolution [bits]: 16 • Bit rate [kbps]: 32, 40, 48, 56, 64, 80, 96, 112, 128, 160, 192, 224, 256, 320, VBR • Channels: stereo, joined stereo, mono • MP3PRO playback • MP3 File extensions: *.mp3 • Decoding of ID3v1, ID3v2, MP3 ID tags including optional album art in .jpeg format up to 2 megapixels • Gapless MP3: Playback is gapless if the container provides LAME encoder delay and padding tags. Supported Vorbis encoding parameters • Sampling rates [kHz]: 32, 44.1, 48 • Resolution [bits]: 16 • Nominal bit rate [kbps] (quality level): 80 (Q1), 96 (Q2), 112 (Q3), 128 (Q4), 160 (Q5), 192 (Q6), • Channels: stereo • The audio player supports reading of Vorbis content stored in Ogg containers. Supported file name extensions: *.ogg and *.oga. • The audio player supports decoding of Vorbis comments. NOTE: There is no specification for tag names. The system relies on the OSS implementation. • Tag names decoded: TITLE, ALBUM, ARTIST, GENRE. • Binary data (e.g. for album art) is not supported. • The audio player supports gapless Vorbis playback. Supported FLAC encoding parameters • Sampling rates [kHz]: 44.1, 48, 88.2, 96, 176.4, 192 • Resolution [bits]: 16, 24 • Channels: stereo, mono • The audio player supports reading of FLAC content stored in native FLAC containers. -

Ogg Audio Codec Download

Ogg audio codec download click here to download To obtain the source code, please see the xiph download page. To get set up to listen to Ogg Vorbis music, begin by selecting your operating system above. Check out the latest royalty-free audio codec from Xiph. To obtain the source code, please see the xiph download page. Ogg Vorbis is Vorbis is everywhere! Download music Music sites Donate today. Get Set Up To Listen: Windows. Playback: These DirectShow filters will let you play your Ogg Vorbis files in Windows Media Player, and other OggDropXPd: A graphical encoder for Vorbis. Download Ogg Vorbis Ogg Vorbis is a lossy audio codec which allows you to create and play Ogg Vorbis files using the command-line. The following end-user download links are provided for convenience: The www.doorway.ru DirectShow filters support playing of files encoded with Vorbis, Speex, Ogg Codecs for Windows, version , ; project page - for other. Vorbis Banner Xiph Banner. In our effort to bring Ogg: Media container. This is our native format and the recommended container for all Xiph codecs. Easy, fast, no torrents, no waiting, no surveys, % free, working www.doorway.ru Free Download Ogg Vorbis ACM Codec - A new audio compression codec. Ogg Codecs is a set of encoders and deocoders for Ogg Vorbis, Speex, Theora and FLAC. Once installed you will be able to play Vorbis. Ogg Vorbis MSACM Codec was added to www.doorway.ru by Bjarne (). Type: Freeware. Updated: Audiotags: , 0x Used to play digital music, such as MP3, VQF, AAC, and other digital audio formats. -

Game Audio the Role of Audio in Games

the gamedesigninitiative at cornell university Lecture 18 Game Audio The Role of Audio in Games Engagement Entertains the player Music/Soundtrack Enhances the realism Sound effects Establishes atmosphere Ambient sounds Other reasons? the gamedesigninitiative 2 Game Audio at cornell university The Role of Audio in Games Feedback Indicate off-screen action Indicate player should move Highlight on-screen action Call attention to an NPC Increase reaction time Players react to sound faster Other reasons? the gamedesigninitiative 3 Game Audio at cornell university History of Sound in Games Basic Sounds • Arcade games • Early handhelds • Early consoles the gamedesigninitiative 4 Game Audio at cornell university Early Sounds: Wizard of Wor the gamedesigninitiative 5 Game Audio at cornell university History of Sound in Games Recorded Basic Sound Sounds Samples Sample = pre-recorded audio • Arcade games • Starts w/ MIDI • Early handhelds • 5th generation • Early consoles (Playstation) • Early PCs the gamedesigninitiative 6 Game Audio at cornell university History of Sound in Games Recorded Some Basic Sound Variability Sounds Samples of Samples • Arcade games • Starts w/ MIDI • Sample selection • Early handhelds • 5th generation • Volume • Early consoles (Playstation) • Pitch • Early PCs • Stereo pan the gamedesigninitiative 7 Game Audio at cornell university History of Sound in Games Recorded Some More Basic Sound Variability Variability Sounds Samples of Samples of Samples • Arcade games • Starts w/ MIDI • Sample selection • Multiple -

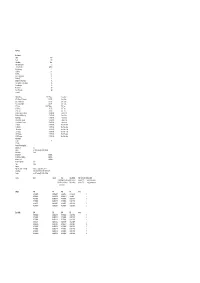

File Name Benchmark Width 1024 Height 768 Anti-Aliasing None

File Name Benchmark Width 1024 Height 768 Anti-Aliasing None Anti-Aliasing Quality 0 Texture Filtering Optimal Max Anisotropy 4 VS Profile 3_0 PS Profile 3_0 Force Full Precision No Disable DST No Disable Post-Processing No Force Software Vertex Shader No Color Mipmaps No Repeat Tests Off Fixed Framerate Off Comment 3DMark Score 4580 3DMarks Game Tests GT1 - Return To Proxycon 18.5 FPS Game Tests GT2 - Firefly Forest 11.7 FPS Game Tests GT3 - Canyon Flight 28.4 FPS Game Tests CPU Score 2184 CPUMarks CPU Tests CPU Test 1 1.1 FPS CPU Tests CPU Test 2 1.9 FPS CPU Tests Fill Rate - Single-Texturing 0.0 FPS N/A Feature Tests Fill Rate - Multi-Texturing 0.0 FPS N/A Feature Tests Pixel Shader 0.0 FPS N/A Feature Tests Vertex Shader - Simple 0.0 FPS N/A Feature Tests Vertex Shader - Complex 0.0 FPS N/A Feature Tests 8 Triangles 0.0 FPS N/A Batch Size Tests 32 Triangles 0.0 FPS N/A Batch Size Tests 128 Triangles 0.0 FPS N/A Batch Size Tests 512 Triangles 0.0 FPS N/A Batch Size Tests 2048 Triangles 0.0 FPS N/A Batch Size Tests 32768 Triangles 0.0 FPS N/A Batch Size Tests System Info Version 3.5 CPU Info Central Processing Unit Manufacturer Intel Family Intel(R) Pentium(R) 4 CPU 3.40GHz Architecture 32-bit Internal Clock 3400 MHz Internal Clock Maximum 3400 MHz External Clock 800 MHz Socket Designation CPU 1 Type Central Upgrade HyperThreadingTechnology Available - 2 Logical Processors Capabilities MMX, CMov, RDTSC, SSE, SSE2, PAE Version Intel(R) Pentium(R) 4 CPU 3.40GHz Caches Level Capacity Type Type Details Error Correction TyAssociativity 1 -

6/8/2018, 16:56:57 Machine Name: LAPTOP

------------------ System Information ------------------ Time of this report: 6/8/2018, 16:56:57 Machine name: LAPTOP-DL519BUJ Machine Id: {6A4BAB40-8615-4F88-B9C6-14E85D02B1B3} Operating System: Windows 10 Famille 64-bit (10.0, Build 17134) (17134.rs4_release.180410-1804) Language: French (Regional Setting: French) System Manufacturer: Acer System Model: Predator G9-791 BIOS: V1.11 (type: UEFI) Processor: Intel(R) Core(TM) i7-6700HQ CPU @ 2.60GHz (8 CPUs), ~2.6GHz Memory: 16384MB RAM Available OS Memory: 16266MB RAM Page File: 5726MB used, 12970MB available Windows Dir: C:\WINDOWS DirectX Version: DirectX 12 DX Setup Parameters: Not found User DPI Setting: 96 DPI (100 percent) System DPI Setting: 96 DPI (100 percent) DWM DPI Scaling: Disabled Miracast: Available, with HDCP Microsoft Graphics Hybrid: Supported DxDiag Version: 10.00.17134.0001 64bit Unicode ------------ DxDiag Notes ------------ Display Tab 1: No problems found. Display Tab 2: No problems found. Sound Tab 1: No problems found. Input Tab: No problems found. -------------------- DirectX Debug Levels -------------------- Direct3D: 0/4 (retail) DirectDraw: 0/4 (retail) DirectInput: 0/5 (retail) DirectMusic: 0/5 (retail) DirectPlay: 0/9 (retail) DirectSound: 0/5 (retail) DirectShow: 0/6 (retail) --------------- Display Devices --------------- Card name: Intel(R) HD Graphics 530 Manufacturer: Intel Corporation Chip type: Intel(R) HD Graphics Family DAC type: Internal Device Type: Full Device (POST) Device Key: Enum\PCI\VEN_8086&DEV_191B&SUBSYS_105B1025&REV_06 Device Status: 0180200A -

Directshow Codecs On

DirectShow Codecs (Reported) Version RVG 0.5754 Windows Vista X86 Windows Vista X64 Codec Company Description Reported Windows XP Pro WindowsXP Starter Business N Business HomeBasic N HomeBasic HomePremium Ultimate Business N Business HomeBasic N HomeBasic HomePremium Ultimate AVI Decompressor Microsoft Corporation DirectShow Runtime AVI Draw Microsoft Corporation DirectShow Runtime Cinepak Codec by Radius Radius Inc. Cinepak® Codec DV Splitter Microsoft Corporation DirectShow Runtime DV Video Decoder Microsoft Corporation DirectShow Runtime DV Video Encoder Microsoft Corporation DirectShow Runtime Indeo® video 4.4 Decompression Filter Intel Corporation Intel Indeo® Video 4.5 Indeo® video 5.10 Intel Corporation Intel Indeo® video 5.10 Indeo® video 5.10 Compression Filter Intel Corporation Intel Indeo® video 5.10 Indeo® video 5.10 Decompression Filter Intel Corporation Intel Indeo® video 5.10 Intel 4:2:0 Video V2.50 Intel Corporation Microsoft H.263 ICM Driver Intel Indeo(R) Video R3.2 Intel Corporation N/A Intel Indeo® Video 4.5 Intel Corporation Intel Indeo® Video 4.5 Intel Indeo(R) Video YUV Intel IYUV codec Intel Corporation Codec Microsoft H.261 Video Codec Microsoft Corporation Microsoft H.261 ICM Driver Microsoft H.263 Video Codec Microsoft Corporation Microsoft H.263 ICM Driver Microsoft MPEG-4 Video Microsoft MPEG-4 Video Decompressor Microsoft Corporation Decompressor Microsoft RLE Microsoft Corporation Microsoft RLE Compressor Microsoft Screen Video Microsoft Screen Video Decompressor Microsoft Corporation Decompressor Video -

Dune HD Duo 4K Is a New Premium Full-Sized 4K Network Media Player

Dune HD Duo 4K is a new premium full-sized 4K network media player, based on the famous SMP8758 Hi-End chip from Sigma Designs, with professional-grade picture quality, audiophile-grade hardware, advanced media playback features, advanced connectivity and integration options, Smart Home support. The new model is equipped with two hot swap 3.5” SATA HDD racks each supporting up to 10TB+ HDD, three USB ports, SD card slot, 1Gbit Ethernet, 802.11ac Dual Band 2T2R Wi-Fi, built-in DVB-T/T2/C tuner (for non-US version), built-in Z-Wave controller. Additionally, Duo 4K has a variety of advanced audiophile features, including the famous ESS SABRE32 Reference DAC (ES9018K2M), XLR balanced stereo audio output, S/PDIF audio input. ESS SABRE32 Reference DAC (ES9018K2M), XLR outputs Decoding 4K and converting SD/HD to 4K VXP professional-grade video processing engine Two hot swap 3.5” SATA HDD racks, Wi-Fi 802.11ac, 1Gbit Ethernet Full Blu-ray menu navigation Built-in Movies Collections Management True 24p output, 3D video, HD audio, Hi-End music DVB-T/T2/C tuner, Smart Home, Z-Wave Specifications Dune HD Duo 4K Media processor Sigma Designs SMP8758 (ARM) RAM 2 GB Flash 8 GB 3xUSB host, SD card slot, HDMI output, optical S/PDIF audio output, coaxial S/PDIF audio output, composite video output, RCA stereo audio output, XLR balanced stereo audio Connectors output, coaxial S/PDIF audio input, external IR port, Ethernet (10/100/1000Mbit), two external Wi-Fi antennas, DVB-T/T2/C RF input/output, 100V-240V AC input Internal storage Two internal HDD racks -

Lossy Audio Compression Identification

2018 26th European Signal Processing Conference (EUSIPCO) Lossy Audio Compression Identification Bongjun Kim Zafar Rafii Northwestern University Gracenote Evanston, USA Emeryville, USA [email protected] zafar.rafi[email protected] Abstract—We propose a system which can estimate from an compression parameters from an audio signal, based on AAC, audio recording that has previously undergone lossy compression was presented in [3]. The first implementation of that work, the parameters used for the encoding, and therefore identify the based on MP3, was then proposed in [4]. The idea was to corresponding lossy coding format. The system analyzes the audio signal and searches for the compression parameters and framing search for the compression parameters and framing conditions conditions which match those used for the encoding. In particular, which match those used for the encoding, by measuring traces we propose a new metric for measuring traces of compression of compression in the audio signal, which typically correspond which is robust to variations in the audio content and a new to time-frequency coefficients quantized to zero. method for combining the estimates from multiple audio blocks The first work to investigate alterations, such as deletion, in- which can refine the results. We evaluated this system with audio excerpts from songs and movies, compressed into various coding sertion, or substitution, in audio signals which have undergone formats, using different bit rates, and captured digitally as well lossy compression, namely MP3, was presented in [5]. The as through analog transfer. Results showed that our system can idea was to measure traces of compression in the signal along identify the correct format in almost all cases, even at high bit time and detect discontinuities in the estimated framing. -

What Is Ogg Vorbis?

Ogg Vorbis Audio Compression Format Norat Rossello Castilla 5/18/2005 Ogg Vorbis 1 What is Ogg Vorbis? z Audio compression format z Comparable to MP3, VQF, AAC, TwinVQ z Free, open and unpatented z Broadcasting, radio station and television by internet ( = Streaming) 5/18/2005 Ogg Vorbis 2 1 About the name… z Ogg = name of Xiph.org container format for audio, video and metadata z Vorbis = name of specific audio compression scheme designed to be contained in Ogg FOR MORE INFO... https://www.xiph.org 5/18/2005 Ogg Vorbis 3 Some comercial characteristics z The official mime type was approved in February 2003 z Posible to encode all music or audio content in Vorbis z Designed to not be proprietary or patented audio format z Patent and licensed-free z Specification in public domain 5/18/2005 Ogg Vorbis 4 2 Audio Compression z Two classes of compression algorithms: - Lossless - Lossy FOR MORE INFO... http://www.firstpr.com.au/audiocomp 5/18/2005 Ogg Vorbis 5 Lossless algorithms z Produce compressed data that can be decoded to output that is identical to the original. z Zip, FLAC for audio 5/18/2005 Ogg Vorbis 6 3 Lossy algorithms z Discard data in order to compress it better than would normally be possible z VORBIS, MP3, JPEG z Throw away parts of the audio waveform that are irrelevant. 5/18/2005 Ogg Vorbis 7 Ogg Vorbis - Compression Factors z Vorbis is an audio codec that generates 16 bit samples at 16KHz to 48KHz, providing variable bit rates from 16 to 128 Kbps per channel FOR MORE INFO.. -

System Information ---Time of This Report: 7/30/2013, 15:28:13 Machine Name

Downloaded from: justpaste.it/39ad ------------------ System Information ------------------ Time of this report: 7/30/2013, 15:28:13 Machine name: ERIKDC-HP Operating System: Windows 7 Home Premium 64-bit (6.1, Build 7601) Service Pack 1 (7601.win7sp1_gdr.130318-1533) Language: English (Regional Setting: English) System Manufacturer: Hewlett-Packard System Model: HP Pavilion g6 Notebook PC BIOS: InsydeH2O Version CCB.03.61.17F.46 Processor: AMD A4-3300M APU with Radeon(tm) HD Graphics (2 CPUs), ~1.9GHz Memory: 4096MB RAM Available OS Memory: 3562MB RAM Page File: 3257MB used, 3866MB available Windows Dir: C:\Windows DirectX Version: DirectX 11 DX Setup Parameters: Not found User DPI Setting: Using System DPI System DPI Setting: 96 DPI (100 percent) DWM DPI Scaling: Disabled DxDiag Version: 6.01.7601.17514 32bit Unicode ------------ DxDiag Notes ------------ Display Tab 1: No problems found. Sound Tab 1: No problems found. Sound Tab 2: No problems found. Input Tab: No problems found. -------------------- DirectX Debug Levels -------------------- Direct3D: 0/4 (retail) DirectDraw: 0/4 (retail) DirectInput: 0/5 (retail) DirectMusic: 0/5 (retail) DirectPlay: 0/9 (retail) DirectSound: 0/5 (retail) DirectShow: 0/6 (retail) --------------- Display Devices --------------- Card name: AMD Radeon(TM) HD 6480G Manufacturer: ATI Technologies Inc. Chip type: ATI display adapter (0x9648) DAC type: Internal DAC(400MHz) Device Key: Enum\PCI\VEN_1002&DEV_9648&SUBSYS_169B103C&REV_00 Display Memory: 2022 MB Dedicated Memory: 497 MB Shared Memory: 1525 MB