A Vertical Sic JFET with a Monolithically Integrated JBS Diode

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

LSK489 Application Note

LSK489 Application Note Low Noise Dual Monolithic JFET Bob Cordell Introduction For circuits designed to work with high impedance sources, ranging from electrometers to microphone preamplifiers, the use of a low-noise, high-impedance device between the input and the op amp is needed in order to optimize performance. At first glance, one of Linear Systems’ most popular parts, the LSK389 ultra-low-noise dual JFET would appear to be a good choice for such an application. The part’s high input impedance (1 T Ω) and low noise (1 nV/ √Hz at 1kHz and 2mA drain current) enables power transfer while adding almost no noise to the signal. But further examination of the LSK389’s specification shows an input capacitance of over 20pF. This will cause intermodulation distortion as the circuit’s input signal increases in frequency if the source impedance is high. This is because the JFET junction capacitances are nonlinear. This will be especially the case where common source amplifier arrangements allow the Miller effect to multiply the effective value of the gate-drain capacitance. Further, the LSK389’s input impedance will fall to a lower value as the frequency increases relative to a part with lower input capacitance. A better design choice is Linear Systems’ new offering, the LSK489. Though the LSK489 has slightly higher noise (1.5 nV/ √Hz vs. 1.0 nV/ √Hz) its much lower input capacitance of only 4pF means that it will maintain its high input impedance as the frequency of the input signal rises. More importantly, using the lower-capacitance LSK489 will create a circuit that is much less susceptible to intermodulation distortion than one using the LSK389. -

A GUIDE to USING FETS for SENSOR APPLICATIONS by Ron Quan

Three Decades of Quality Through Innovation A GUIDE TO USING FETS FOR SENSOR APPLICATIONS By Ron Quan Linear Integrated Systems • 4042 Clipper Court • Fremont, CA 94538 • Tel: 510 490-9160 • Fax: 510 353-0261 • Email: [email protected] A GUIDE TO USING FETS FOR SENSOR APPLICATIONS many discrete FETs have input capacitances of less than 5 pF. Also, there are few low noise FET input op amps Linear Systems that have equivalent input noise voltages density of less provides a variety of FETs (Field Effect Transistors) than 4 nV/ 퐻푧. However, there are a number of suitable for use in low noise amplifier applications for discrete FETs rated at ≤ 2 nV/ 퐻푧 in terms of equivalent photo diodes, accelerometers, transducers, and other Input noise voltage density. types of sensors. For those op amps that are rated as low noise, normally In particular, low noise JFETs exhibit low input gate the input stages use bipolar transistors that generate currents that are desirable when working with high much greater noise currents at the input terminals than impedance devices at the input or with high value FETs. These noise currents flowing into high impedances feedback resistors (e.g., ≥1MΩ). Operational amplifiers form added (random) noise voltages that are often (op amps) with bipolar transistor input stages have much greater than the equivalent input noise. much higher input noise currents than FETs. One advantage of using discrete FETs is that an op amp In general, many op amps have a combination of higher that is not rated as low noise in terms of input current noise and input capacitance when compared to some can be converted into an amplifier with low input discrete FETs. -

Junction Field Effect Transistor (JFET)

Junction Field Effect Transistor (JFET) The single channel junction field-effect transistor (JFET) is probably the simplest transistor available. As shown in the schematics below (Figure 6.13 in your text) for the n-channel JFET (left) and the p-channel JFET (right), these devices are simply an area of doped silicon with two diffusions of the opposite doping. Please be aware that the schematics presented are for illustrative purposes only and are simplified versions of the actual device. Note that the material that serves as the foundation of the device defines the channel type. Like the BJT, the JFET is a three terminal device. Although there are physically two gate diffusions, they are tied together and act as a single gate terminal. The other two contacts, the drain and source, are placed at either end of the channel region. The JFET is a symmetric device (the source and drain may be interchanged), however it is useful in circuit design to designate the terminals as shown in the circuit symbols above. The operation of the JFET is based on controlling the bias on the pn junction between gate and channel (note that a single pn junction is discussed since the two gate contacts are tied together in parallel – what happens at one gate-channel pn junction is happening on the other). If a voltage is applied between the drain and source, current will flow (the conventional direction for current flow is from the terminal designated to be the gate to that which is designated as the source). The device is therefore in a normally on state. -

EE-202 Electronics-I- Field-Effect Transistors JFET

EE-202 Electronics-I- Chapter 10 Field-Effect Transistors JFET 1 FET FET (Field-Effect Transistors) - BJTs (Bipolar Junction Transistors). Similarities: • Amplifiers • Switching devices • Impedance matching circuits Differences: • FETs are voltage controlled devices, BJTs are current controlled devices. • FETs have a higher input impedance, BJTs have higher gains. • FETs are less sensitive to temperature variations and they are more easily integrated on ICs. • FETs are generally more sensitive to static than BJTs. 2 FET Types •JFET–– Junction Field-Effect Transistor •MOSFET –– Metal-Oxide Field-Effect Transistor .D-MOSFET –– Depletion MOSFET .E-MOSFET –– Enhancement MOSFET 3 JFET Construction There are two types of JFETs •n-channel •p-channel The n-channel is more widely used. There are three terminals. •Drain (D) and source (S) are connected to the n-channel •Gate (G) is connected to the p-type material 4 JFET Operating Characteristics Three basic operating conditions for a JFET: • VGS = 0, VDS increasing to some positive value • VGS < 0, VDS at some positive value • Voltage-controlled resistor 5 JFET Operating Characteristics VGS = 0, VDS increasing to some positive value When VGS = 0 and VDS is increased from 0 to a more positive voltage; • The depletion region between p-gate and n-channel increases • Increasing the depletion region, decreases the size of the n-channel • Increasing in the n-channel resistance, the ID current increases. 6 JFET Operating Characteristics VGS = 0, VDS increasing to some positive value: Pinch Off VGS = 0 and VDS is increased to a more positive voltage, the depletion zone gets so large that it pinches off the n-channel. -

Field Effect Transistors

Module www.learnabout-electronics.org 4 Field Effect Transistors Module 4.1 Junction Field Effect Transistors What you´ll learn in Module 4 Field Effect Transistors Section 4.1 Field Effect Transistors. Although there are lots of confusing names for field • FETs JFETs, JUGFETs, and IGFETS effect transistors (FETs) there are basically two main • The JFET. types: • Diffusion JFET Construction. • Planar JFET Construction. 1. The reverse biased PN junction types, the JFET or • JFET Circuit Symbols. Junction FET, (also called the JUGFET or Junction Unipolar Gate FET). Section 4.2 How a JFET Works. • Operation Below Pinch Off. 2. The insulated gate FET devices (IGFET). • Operation Above Pinch Off. • JFET Output Characteristic. All FETs can be called UNIPOLAR devices because • JFET Transfer Characteristic. the charge carriers that carry the current through the • JFET Video. device are all of the same type i.e. either holes or electrons, but not both. This distinguishes FETs from Section 4.3 The Enhancement Mode MOSFET. the bipolar devices in which both holes and electrons • The IGFET (Insulated Gate FET). • MOSFET(IGFET) Construction. are responsible for current flow in any one device. • MOSFET(IGFET) Operation. The JFET • MOSFET (IGFET) Circuit Symbols. • Handling Precautions for MOSFETS This was the earliest FET device available. It is a voltage-controlled device in which current flows Section 4.4 The Depletion Mode MOSFET. from the SOURCE terminal (equivalent to the • Depletion Mode MOSFET Operation. emitter in a bipolar transistor) to the DRAIN • MOSFE (IGFET) Circuit Symbols. (equivalent to the collector). A voltage applied • Applications of MOSFETS • High Power MOSFETS between the source terminal and a GATE terminal (equivalent to the base) is used to control the source - Section 4.5 Power MOSFETs. -

Notes on BJT & FET Transistors

Phys2303 L.A. Bumm [ver 1.1] Transistors (p1) Notes on BJT & FET Transistors. Comments. The name transistor comes from the phrase “transferring an electrical signal across a resistor.” In this course we will discuss two types of transistors: The Bipolar Junction Transistor (BJT) is an active device. In simple terms, it is a current controlled valve. The base current (IB) controls the collector current (IC). The Field Effect Transistor (FET) is an active device. In simple terms, it is a voltage controlled valve. The gate-source voltage (VGS) controls the drain current (ID). Regions of BJT operation: Cut-off region: The transistor is off. There is no conduction between the collector and the emitter. (IB = 0 therefore IC = 0) Active region: The transistor is on. The collector current is proportional to and controlled by the base current (IC = βIC) and relatively insensitive to VCE. In this region the transistor can be an amplifier. Saturation region: The transistor is on. The collector current varies very little with a change in the base current in the saturation region. The VCE is small, a few tenths of volt. The collector current is strongly dependent on VCE unlike in the active region. It is desirable to operate transistor switches will be in or near the saturation region when in their on state. Rules for Bipolar Junction Transistors (BJTs): • For an npn transistor, the voltage at the collector VC must be greater than the voltage at the emitter VE by at least a few tenths of a volt; otherwise, current will not flow through the collector-emitter junction, no matter what the applied voltage at the base. -

BJT JFET MOSFET Circa 1960 1970 1980 Gm/I (Signal Gain) Best Better Good

• Crossover Distortion •FETS • Spec sheets • Configurations • Applications Acknowledgements: Neamen, Donald: Microelectronics Circuit Analysis and Design, 3rd Edition 6.101 Spring 2020 Lecture 6 1 Three Stage Amplifier – Crossover Distortion Hole Feedback 6.101 Spring 2020 Lecture 5 2 Crossover Distortion Analysis 6.101 Spring 2020 Lecture 5 3 Crossover Distortion Analysis 11 1 v v v e 10 in 10 out • The distortion 0.6v in each direction or 1.2v total vg 570ve resulting in a hole that is: 11 1 0.0172*1.2 ~ 0.02v vout 570 vin vout vn 10 10 • Increasing open loop gain 11 570 will reduce the crossover 1 v 10 v v 10.81v 0.0172v distortion. out 1 in 1 n in n 1 570 1 570 10 10 6.101 Spring 2020 Lecture 5 4 BJT ‐ FET Bipolar Junction Transistor Field Effect Transistor • Three terminal device • Three terminal device • Collector current controlled • Channel conduction by base current ib= f(Vbe) controlled by electric field • Think as current amplifier • No forward biased junction • NPN and PNP i.e. no current • JFETs, MOSFETs • Depletion mode, enhancement mode 6.101 Spring 2020 Lecture 6 5 BJT ‐ JFETS ‐ MOSFETS BJT JFET MOSFET Circa 1960 1970 1980 Gm/I (signal gain) Best Better Good Isolation PN Junction Metal Oxide* ESD Low Moderate Very sensitive Control Current Voltage Voltage Power YES No Yes *silicon dioxide 6.101 Spring 2020 Lecture 6 6 Voltage Noise * * Horowitz & Hill, Art of Electronics 3rd Edition p 170 6.101 Spring 2020 Lecture 6 7 FET Family Tree FET JFET depletion MOSFET n-channel p-channel depletion enhancement n-channel Vgs(off) gate source cutoff or n-channel p-channel Vp pinch-off voltage Vgs(th) gate source threshold voltage 6.101 Spring 2020 Lecture 6 8 Transistor Polarity Mapping* + output n-channel depletion n-channel enhancment n-channel JFET npn bjt input - + p-channel enhancment p-channel JFT pnp bjt - * Horwitz & Hill, the Art of Electronics, 3rd Edition 6.101 Spring 2020 Lecture 6 9 MOSFET & JFETS • MOSFETS – Much more finicky difficult process (to make) than JFET’s. -

Fabrication and Characterization of Polymeric P-Channel Junction Fets Tianhong Cui, Yuxin Liu, and Kody Varahramyan

IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. 51, NO. 3, MARCH 2004 389 Fabrication and Characterization of Polymeric P-Channel Junction FETs Tianhong Cui, Yuxin Liu, and Kody Varahramyan Abstract—Polymer materials are attracting more and more polymer devices. The possibility of processing conducting attention for the applications to microelectronic/optoelectronic polymers based on coating techniques has enabled researchers devices due to their flexibility, lightweight, low cost, etc. In this to fabricate various electronic/optoelectronic devices such as paper, fabrication and characterization of a polymer junction field-effect transistor (JFET), using poly (3,4-ethylenedioxythio- thin film transistors, diodes, LEDs, capacitors, organic inte- phene) poly (styrenesulfonate) (PEDT/PSS) as the channel and grated circuits, organic wires, and electroluminescent devices poly (2,5-hexyloxy p-phenylene cyanovinylene) (CNPPV) as the [8]–[14]. Polymer thin films can be coated on substrates such gate layer, are reported. The all-polymer JFET was fabricated as glass, plastic, silicon, wood, or paper. by the conventional ultraviolet (UV) lithography techniques. The In this paper, a p-channel polymer JFET fabricated with ultra- fabricated device was measured and characterized electrically. In the meantime, the comparisons were listed between polymer violet (UV) lithography was presented, and its operation mech- JFET and analogous inorganic semiconductor counterparts. Its anism was discussed in detail. Based on the testing results, the pinch-off voltage reaches 1 V that is in the applicable range, and polymer JFET and the characteristics of conducting polymers the current is IQ V e at zero gate bias. It demonstrates that were analyzed. the device operates in a very similar fashion to its conventional counterparts. -

Chapter 6: Field-Effect Transistors Fets Vs

www.getmyuni.com Chapter 6: Field-Effect Transistors www.getmyuni.com FETs vs . BJTsFETs BJTs Similarities:Similarities:Similarities: • Amplifiers • Switching devices • Impedance matching circuits Differences:Differences: • FETs are voltage controlled devices. BJTs are current controlled devices. • FETs have a higher input impedance. BJTs have higher gains. • FETs are less sensitive to temperature variations and are more easily integrated on ICs. • FETs are generally more static sensitive than BJTs. Electronic Devices and Circuit Theory, 10/e 22 Robert L. Boylestad and Louis Nashelsky www.getmyuni.com FET ypesTFET Types FET ypesT : JFET•• :Junction JFET FET ••MOSFET: Metal–Oxide–Semiconductor FET MOSFETDD--MOSFET: MOSFETDltiMOSFETDepletion MOSFET EE--MOSFET:MOSFET: Enhancement MOSFET Electronic Devices and Circuit Theory, 10/e 33 Robert L. Boylestad and Louis Nashelsky www.getmyuni.com JFET ConstructionJFET Construction There are two types of JFETs channel••nn- -channel channel••pp- -channel The n-chliidldhannel is more widely used. There are three terminals: Drain•• (D)DrainceSour and ceSour(S) are connected to the n-channel Gate•• Gate(G) is connected to the p-type material Electronic Devices and Circuit Theory, 10/e 44 Robert L. Boylestad and Louis Nashelsky www.getmyuni.comJFET Operation: The Basic IdeaJFET Idea JFET operation can be compared to a water spigot. The sourceThe source of water pressure is the accumulation of electrons at the negatilfhdiive pole of the drain-source voltage. The dra iThdin oftithltf water is the electron deficiency (or holes) at the positive pole of the applied voltage. The controlThe control of flow of water is the gate voltage that controls the width of the n -channel and , therefore , the flow of charges from source to drain. -

Jfet and Mosfet

JFET AND MOSFET BITS Pilani Dubai Campus Dr Jagadish Nayak BITS Pilani Dubai Campus Junction Field Effect Transistors & Metal Oxide Semiconductor Field Effect Transistors JFET Construction (n channel) Symbol D G S BITS Pilani, Dubai Campus JFET Construction (p channel) Symbol BITS Pilani, Dubai Campus JFET BITS Pilani, Dubai Campus JFET Circuit analysis BITS Pilani, Dubai Campus JFET When VDD = VGG=0, two junctions with associated depletion region is shown BITS Pilani, Dubai Campus JFET When the VDD=vDS is small (positive) number, a small positive drain current results. The potential at drain vD is approximately equal to source voltage vS (vS ≈ vD =0) However if VGG is increased, since vGS= -VGG , then pn junction will become more reverse biased and depletion region gets wider. Because vS (vS ≈ vD =0) , the depletion regions are symmetrical. When the VGG is sufficiently increased , the depletion region will be widened and channel will become narrower. The value of vGS= -VGG , which eliminates the channel is called as pinchoff voltage. BITS Pilani, Dubai Campus JFET As long as VDD= vDS= vD-vS remains small , the depletion region will be essentially symmetrical and iD will be proportional to vDS, i. e channel will behave as a linear resistor. However, if VDD=vDS=vD-vS gets larger, then iD gets larger and vD becomes greater than vS Since vGS=0 V vGD=vGS-vDS= 0-vDS=-vDS BITS Pilani, Dubai Campus JFET Since gate drain voltage is negative and gate source voltage is zero, portion of the pn junction between the gate and drain is more reverse biased than portion between gate and source. -

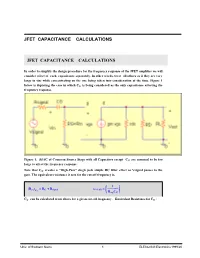

JFET Amp Capacitance Calculations-V03.Nb Prof

JFET CAPACITANCE CALCULATIONS JFET CAPACITANCE CALCULATIONS In order to simplify the design procedure for the frequency response of the JFET amplifier we will consider effect of each capacitance separately. In other words, treat all others as if they are very large in size while concentrating on the one being taken into consideration at the time. Figure 1 below is depicting the case in which CG is being considered as the only capacitance affecting the frequency response. Figure 1. SSAC of Common Source Stage with all Capacitors except CG are assumed to be too large to affect the frequency response. Note that CG creates a "High-Pass" single pole simple RC filter effect as Vsignal passes to the gate. The equivalent resistance it sees for the cut-off frequency is, 1 Req = RG + Rsignal w-3 dB = ÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄ CG Req.CG CG can be calculated from above for a given cut-off frequency.ji Eqzyuivalent Resistance for CD : H L j z k { Univ. of Southern Maine 1 ELE342/343 Electronics 1999/20 JFET Amp Capacitance Calculations-v03.nb Prof. M. G. Guven Figure 2. SSAC of Common Source Stage with all Capacitors except CD are assumed to be too large to affect the frequency response Req = RL + rds RD Rout = rds RD CD Equivalent Resistance for CS : H L H ˛ L H ˛ L Figure 3. SSAC of Common Source Stage with all Capacitors except CS are assumed to be too large to affect the frequency response ' Req = RS R CS CS eq H L ˛@H L D Univ. of Southern Maine 2 ELE342/343 Electronics 1999/20 JFET Amp Capacitance Calculations-v03.nb Prof.M.G.Guven Figure 4. -

Simplify Transimpedance Applications with High-Bandwidth, Precision JFET Op Amps

Simplify Transimpedance Applications with High- bandwidth, Precision JFET Op Amps Raphael Puzio, Luis Chioye Modern JFET-input operational amplifiers (op amps) Transimpedance Op Amp Gain, Bandwidth, and offer a combination of high input impedance, excellent Stability DC and AC performance, low noise, high bandwidth, and wide voltage supply range, making them a natural When selecting an op amp for a photodiode TIA choice for transimpedance op amp (TIA) applications. application, it is important to carefully consider the A TIA is a current-to-voltage converter, typically used three factors that dictate the minimum gain bandwidth as a front-end for optical sensors such as photodiodes, product of the op amp (fGBW) necessary for circuit commonly found in Optical Line Cards, Light Level stability: the TIA required V/I gain, the required closed- Sensors, PM 2.5 Detectors, and many more. Silicon loop TIA bandwidth, and the parasitic junction photodiodes produce a current output that changes capacitance of the photodiode (CJ). linearly with incident light, where the typical photo current ranges from a few pico-amps to a few The stability of an op amp is related to its closed-loop milliamps. The combination of high input impedance, gain and phase response over frequency. The closed- with low input bias currents of a few pico-amps at loop gain is defined as the product of the open-loop room temperature, and very low current and voltage gain of the op amp (AOL) and the feedback factor of noise, allow JFET op amps to be used in precision, the op amp (β), defined as AOL × β.