VESA® PLUG and DISPLAY STANDARD Video Electronics Standards Association

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Dell 24 USB-C Monitor - P2421DC User’S Guide

Dell 24 USB-C Monitor - P2421DC User’s Guide Monitor Model: P2421DC Regulatory Model: P2421DCc NOTE: A NOTE indicates important information that helps you make better use of your computer. CAUTION: A CAUTION indicates potential damage to hardware or loss of data if instructions are not followed. WARNING: A WARNING indicates a potential for property damage, personal injury, or death. Copyright © 2020 Dell Inc. or its subsidiaries. All rights reserved. Dell, EMC, and other trademarks are trademarks of Dell Inc. or its subsidiaries. Other trademarks may be trademarks of their respective owners. 2020 – 03 Rev. A01 Contents About your monitor ......................... 6 Package contents . 6 Product features . .8 Identifying parts and controls . .9 Front view . .9 Back view . 10 Side view. 11 Bottom view . .12 Monitor specifications . 13 Resolution specifications . 14 Supported video modes . 15 Preset display modes . 15 MST Multi-Stream Transport (MST) Modes . 16 Electrical specifications. 16 Physical characteristics. 17 Environmental characteristics . 18 Power management modes . 19 Plug and play capability . 25 LCD monitor quality and pixel policy . 25 Maintenance guidelines . 25 Cleaning your monitor. .25 Setting up the monitor...................... 26 Attaching the stand . 26 │ 3 Connecting your monitor . 28 Connecting the DP cable . 28 Connecting the monitor for DP Multi-Stream Transport (MST) function . 28 Connecting the USB Type-C cable . 29 Connecting the monitor for USB-C Multi-Stream Transport (MST) function. 30 Organizing cables . 31 Removing the stand . 32 Wall mounting (optional) . 33 Operating your monitor ..................... 34 Power on the monitor . 34 USB-C charging options . 35 Using the control buttons . 35 OSD controls . 36 Using the On-Screen Display (OSD) menu . -

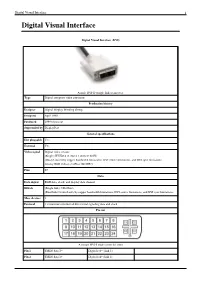

Digital Visual Interface (DVI)

Digital Visual Interface 1 Digital Visual Interface Digital Visual Interface (DVI) A male DVI-D (single link) connector. Type Digital computer video connector Production history Designer Digital Display Working Group Designed April 1999 Produced 1999 to present Superseded by DisplayPort General specifications Hot pluggable Yes External Yes Video signal Digital video stream: (Single) WUXGA (1,920 × 1,200) @ 60 Hz (Dual) Limited by copper bandwidth limitations, DVI source limitations, and DVI sync limitations. Analog RGB video (−3 dB at 400 MHz) Pins 29 Data Data signal RGB data, clock, and display data channel Bitrate (Single link) 3.96 Gbit/s (Dual link) Limited only by copper bandwidth limitations, DVI source limitations, and DVI sync limitations. Max. devices 1 Protocol 3 × transition minimized differential signaling data and clock Pin out A female DVI-I socket from the front Pin 1 TMDS data 2− Digital red− (link 1) Pin 2 TMDS data 2+ Digital red+ (link 1) Digital Visual Interface 2 Pin 3 TMDS data 2/4 shield Pin 4 TMDS data 4− Digital green− (link 2) Pin 5 TMDS data 4+ Digital green+ (link 2) Pin 6 DDC clock Pin 7 DDC data Pin 8 Analog vertical sync Pin 9 TMDS data 1− Digital green− (link 1) Pin 10 TMDS data 1+ Digital green+ (link 1) Pin 11 TMDS data 1/3 shield Pin 12 TMDS data 3- Digital blue− (link 2) Pin 13 TMDS data 3+ Digital blue+ (link 2) Pin 14 +5 V Power for monitor when in standby Pin 15 Ground Return for pin 14 and analog sync Pin 16 Hot plug detect Pin 17 TMDS data 0− Digital blue− (link 1) and digital sync Pin 18 TMDS data 0+ Digital blue+ (link 1) and digital sync Pin 19 TMDS data 0/5 shield Pin 20 TMDS data 5− Digital red− (link 2) Pin 21 TMDS data 5+ Digital red+ (link 2) Pin 22 TMDS clock shield Pin 23 TMDS clock+ Digital clock+ (links 1 and 2) Pin 24 TMDS clock− Digital clock− (links 1 and 2) C1 Analog red C2 Analog green C3 Analog blue C4 Analog horizontal sync C5 Analog ground Return for R, G, and B signals Digital Visual Interface (DVI) is a video display interface developed by the Digital Display Working Group (DDWG). -

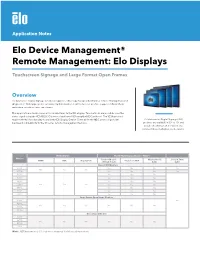

Elo Displays

Application Notes Elo Device Management® Remote Management: Elo Displays Touchscreen Signage and Large Format Open Frames Overview Elo Interactive Digital Signage products support technology that greatly simplifies remote management and diagnostics. With appropriate software implementation, it will reduce on-premise support calls and help maintain a consistent user experience. This application note discusses all local interfaces to the IDS display. Two methods are possible: over the video signal using the VESA DDC/CI protocol and over USB using the MDC protocol. The VESA protocol enables the full functionality found in the Elo Display Device Client while the MDC protocol provides Elo’s Interactive Digital Signage (IDS) backward compatibility to the 00 series remote management features. products are available in 32" to 70" and include the thinnest (3-3.5") all-in-one commercial touch displays on the market. VESA DDC/Ci RS232 (Multi-Display Channel “MDC”) Monitor Touch USB cable Physical Serial Serial 3.5mm HDMI VGA DisplayPort Y-Cable on VGA (Virtual Serial) Cable Cable Current IDS Monitors 5553L Yes No No Yes Yes No Yes 6553L Yes No No Yes 3202L Yes Yes No 4202L Yes Yes No 4602L Yes Yes No 5501LT Yes Yes Yes Yes Yes No 5551L Yes No Yes 5502L Yes Yes No 7001LT Yes Yes No Large Format Open Frame Monitors 3243L No 4243L Yes Yes Yes No No No 4343L 5543L Discontinued Models 3201L 4201L Yes Yes Yes Yes No No 5501L 7001L Note: .NET framework is 4.0 or above is required for Microsoft framework. Application Notes I. MDC Protocol All Elo Touchscreen Signage support the Eloview MDC protocol. -

Dell C7017T User's Guide

User‘s Guide Dell C7017T Regulatory model: C7017Tf NOTE: A NOTE indicates important information that helps you make better use of your computer. CAUTION: A CAUTION indicates potential damage to hardware or loss of data if instructions are not followed. WARNING: A WARNING indicates a potential for property damage, personal injury, or death. © 2016 Dell Inc. All rights reserved. Information in this document is subject to change without notice. Reproduction of these materials in any manner whatsoever without the written permission of Dell Inc. is strictly forbidden. Trademarks used in this text: Dell™ and the DELL logo are trademarks of Dell Inc.; Microsoft®, Windows®, and the Windows start button logo are either trademarks or registered trademarks of Microsoft Corporation in the United States and/or other countries. Other trademarks and trade names may be used in this document to refer to either the entities claiming the marks and names or their products. Dell Inc. disclaims any proprietary interest in trademarks and trade names other than its own. 2016 –07 Rev. A01 2 Contents About Your Monitor ..................................... 5 Package Contents . .5 Product Features . 7 Remote Control . 8 Identifying Parts and Controls. 11 Monitor Specifications . 14 Plug and Play Capability . 23 LCD Monitor Quality & Pixel Policy . 27 Maintenance Guidelines . 28 Setting Up the Monitor..................................29 Connecting Your Monitor . 29 Wall Mounting . 32 Operating the Monitor .................................. 33 Power On the Monitor . 33 Using the Front-Panel Controls . .33 Using the On-Screen Display (OSD) Menu. 34 Touch OSD Control . 47 OSD Messages . 48 Setting the Maximum Resolution . 51 Dell Web Management for Monitors . -

Understanding EDID: an Introduction to AW EDID Editor

WHITE PAPER Understanding EDID: An Introduction to AW EDID Editor 1 What does EDID look like? ............................................................................................................................... 2 2 How is EDID exchanged? .................................................................................................................................. 3 3 Managing EDID with Analog Way Switchers (Midra™ series and LiveCore™ series) ........................................... 4 4 Using AW EDID Editor ...................................................................................................................................... 6 5 Troubleshooting EDID problems ...................................................................................................................... 8 1 WP: Understanding EDID: An introduction to AW EDID Editor WHITE PAPER Introduction Extended Display Identification Data (EDID) is a data structure standardized by the Video Electronics Standard Association (VESA). Thanks to EDID, a display system provides its capabilities to a source so that the source can take them into account when delivering its content. An EDID contains information such as the manufacturer name, the product ID, the input type (analog or digital), the supported timings, the display size and the luminance characteristics. The goal is to optimize the use of the display and to make interoperability easier for displays with VGA ports (optional), as well as DisplayPort, HDMI, and DVI ports (compulsory). As consumer -

Dell P3421W Monitor User’S Guide

Dell P3421W Monitor User’s Guide Model: P3421W Regulatory model: P3421Wb NOTE: A NOTE indicates important information that helps you make better use of your computer. CAUTION: A CAUTION indicates potential damage to hardware or loss of data if instructions are not followed. WARNING: A WARNING indicates a potential for property damage, personal injury, or death. Copyright © 2020 Dell Inc. or its subsidiaries. All rights reserved. Dell, EMC, and other trademarks are trademarks of Dell Inc. or its subsidiaries. Other trademarks may be trademarks of their respective owners. 2020 - 10 Rev. A00 Contents About your monitor . 6 Package contents. 6 Product features . 8 Identifying parts and controls . 9 Front view . 9 Back view . .10 Bottom view . 11 Monitor specifications . 12 Resolution specifications. 14 Supported video modes . 14 Preset display modes . 14 Electrical specifications . .15 Physical characteristics . .16 Environmental characteristics . 18 Pin assignments . .19 Plug and play capability . 21 Universal Serial Bus (USB) interface . 21 SuperSpeed USB 5 Gbps (USB 3.2 Gen1). 21 USB 2.0 . 21 USB Type-C . 21 USB 3.2 Gen1 (5 Gbps) upstream connector . 22 USB 3.2 Gen1 (5 Gbps) downstream connector . 22 USB 2.0 downstream connector . 23 USB Type-C connector . 23 USB ports . 24 LCD monitor quality and pixel policy . 24 Maintenance guidelines . 24 │3 Cleaning your monitor . 24 Setting up the monitor . 25 Attaching the stand . 25 Connecting your monitor . 28 Connecting the DisplayPort (DisplayPort to DisplayPort) cable. 29 Connecting the HDMI cable . 30 Connecting the USB Type-C cable . 31 Connecting the USB 3.2 Gen1 (5 Gbps) cable . -

Digital Visual Interface Revision 1

Digital Visual Interface Revision 1. 0 Digital Display Working Group Digital Visual Interface DVI Revision 1.0 02 April 1999 Page 1 of 76 HTC EXHIBIT 1013 Digital Visual Interface Revision 1. 0 Digital Display Working Group The Digital Display Working Group Promoters (''DDWG Promoters") are Intel Corporation, Silicon Jmage, lnc., Compaq Computer Corporation, Fujitsu Limited, Hewlett-Packard Company, lntemational Business Macbines Corporation, and NEC Corporation TffiS SPECIFICATION IS PROVIDED "AS lS" WJTH NO WARRANTIES WHATSOEVER, INCLUDING ANY WARRANTY OF MERCHANTAB[LITY, NONlNFRlNGEMENT, FITNESS FOR ANY PARTICULAR PURPOSE, OR ANY WARRANTY OTHERWISE ARISING OUT OF ANY PROPOSAL, SPECWICATION OR SAMPLE. The DDWG Promoters disclaim all liability, including liability for infringement ofany proprietary rights, relating to usc of information in this sprxilil:ation. No license. express or implied, by estoppel or othetwise, to any intellectual property rights is granted herein. The DDWG Promoters may have patents and/or patent applications related to the Digital Visua//nteJfaoe Specification. The DDWG Promoters intend to make avai lable to the industry <Ul Adopter's Agreement that will include a limited. reciprocal, royalty-free license to tl1e electrical interfaces. mechanical interfaces. signals, si ~:,'llaling and coding protocols, and bus protocols described in, and required by, the Digita/11isual Tnte1jace Specfftcation Revision }.() finalized and published by the DDWG Promoters. To encourage early adoption. Adopters will be required to retum their executed copy of the Adopter's Agreement during an "Adoption Period" which is within one year after the DVl Specification Revision 1.0 is first published or within one year after the Adopter first sells products that comply with that specification, whichever is later. -

Alienware AW2720HF Monitor User's Guide

Alienware AW2720HF Monitor User’s Guide Model: AW2720HF Regulatory model: AW2720HFb Notes, cautions, and warnings NOTE: A NOTE indicates important information that helps you make better use of your computer. CAUTION: A CAUTION indicates potential damage to hardware or loss of data if instructions are not followed. WARNING: A WARNING indicates a potential for property damage, personal injury, or death. © 2019 Dell Inc. or its subsidiaries. All rights reserved. Dell, EMC, and other trademarks are trademarks of Dell Inc. or its subsidiaries. Other trademarks may be trademarks of their respective owners 2019 - 10 Rev. A01 Contents About your monitor . 6 Package contents . 6 Product features . 8 Identifying parts and controls . 9 Front view . .9 Back view. .10 Rear and bottom view . 11 Monitor specifications . 12 Resolution specifications . 14 Supported video modes . .14 Preset display modes . .15 Electrical specifications . .15 Physical characteristics . .16 Environmental characteristics. .17 Power management modes . .18 Pin assignments . .19 Plug and Play capability. .20 Universal Serial Bus (USB) interface . 21 USB upstream connector . .21 USB downstream connector . 22 USB ports. 22 LCD monitor quality and pixel policy. 23 Maintenance guidelines . 23 Cleaning your monitor . 23 Setting up the monitor. 24 Attaching the stand . 24 Connecting the computer . .28 |3 Removing the monitor stand . 29 VESA wall mounting (optional). .31 Operating the monitor. 32 Power on the monitor . .32 Using the joystick control . .32 Using the rear-panel controls . .33 Using the On-Screen Display (OSD) menu . .34 Accessing the menu system . .34 OSD warning message . .45 Setting the maximum resolution . 47 Using the tilt, swivel, and vertical extension . -

Dell U2413/U2713H Monitor User's Guide

Dell™ U2413/U2713H Monitor User's Guide Setting the display resolution Information in this document is subject to change without notice. © 2012 Dell Inc. All rights reserved. Reproduction of these materials in any manner whatsoever without the written permission of Dell Inc. is strictly forbidden. Trademarks used in this text: Dell and the DELL logo are trademarks of Dell Inc.; Microsoft and Windows are either trademarks or registered trademarks of Microsoft Corporation in the United States and/or other countries, Intel is a registered trademark of Intel Corporation in the U.S. and other countries; and ATI is a trademark of Advanced Micro Devices,Inc. has determined that this product meets the ENERGY STAR guidelines for energy efficiency. Other trademarks and trade names may be used in this document to refer to either the entities claiming the marks and names or their products. Dell Inc. disclaims any proprietary interest in trademarks and trade names other than its own. Model U2413f / U2713Hb November 2012 Rev. A00 Dell™ U2413/U2713H Monitor User's Guide About Your Monitor Setting Up the Monitor Operating the Monitor Troubleshooting Appendix Notes, Cautions, and Warnings NOTE: A NOTE indicates important information that helps you make better use of your computer. CAUTION: A CAUTION indicates potential damage to hardware or loss of data if instructions are not followed. WARNING: A WARNING indicates a potential for property damage, personal injury, or death. Information in this document is subject to change without notice. © 2012 Dell Inc. All rights reserved. Reproduction of these materials in any manner whatsoever without the written permission of Dell Inc. -

Vga (Vesa Ddc)

VGA (VESA DDC) From HwB VGA=Video Graphics Adapter or Video Graphics Array VESA=Video Electronics Standards Association DDC=Display Data Channel Contents • 1 Pinout o 1.1 VESA DPMS power saving o 1.2 DDC 1.2.1 DDC1 1.2.2 DDC2B 1.2.3 DDC2B+ 1.2.4 DDC2AB/DDC2B+ 1.2.5 DDC/CI (formerly DDC2Bi) o 1.3 Extended Display Identification Data 1.3.1 EDID 1.0/1.1 1.3.2 E-EDID • 2 Links • 3 Contributions • 4 Source Pinout Videotype: Analogue. 15 PIN HIGHDENSITY D-SUB FEMALE at the videocard. 15 PIN HIGHDENSITY D-SUB MALE at the monitor cable. Pin Name Dir Description Impedance/Level 1 RED Red Video 75 Ω, 0.7 V p-p 2 GREEN Green Video 75 Ω, 0.7 V p-p 3 BLUE Blue Video 75 Ω, 0.7 V p-p 4 RES - Reserved 5 GND Ground 6 RGND Red Ground 7 GGND Green Ground 8 BGND Blue Ground 9 +5V +5 VDC 10 SGND Sync Ground 11 ID0 Monitor ID Bit 0 (optional) 12 SDA DDC Serial Data Line 13 HSYNC or CSYN C Horizontal Sync (or Composite Sync) 14 VSYNC Vertical Sync 15 SCL DDC Data Clock Line Note: Direction is Computer relative Monitor. VESA DPMS power saving DPMS = Device Power Management Signalling Power save mode Signal Normal Standby Supspended Off 13 HSYNC On Off On Off 14 VSYNC On On Off Off Power level 100% 80% <30W <8W DDC DDC = Display Data Channel Pins Name Protocol SDA SCL DDC1 14 Unidirection protocol (uses VS YNC (14) as clock) DDC2B I²C DDC2B+ 12 I²C (Bidirectional) 15 DDC2AB I²C (ACCESS.bus) DDC/CI I²C Note: DDC2 was never implemented DDC1 DDC1 is a quite simple protocol. -

Extended Display Identification (EDID) a Primer

Extended Display Identification (EDID) A Primer What is an EDID? Extended Display Identification Data (EDIDs) are data structures that reside in a display device—commonly referred to as “sinks” in HDMI and DisplayPort standards documents— such as an HDTV or a computer monitor. They are intended to be read by a “source” device (e.g. set top boxes, DVD players, PC graphic cards) in order to simplify user operation and to ensure that the user’s viewing experience is optimal, or as good as it can be based on the capabilities of the rendering sink device, i.e. audio system and/or video display (sink). EDIDs were created by Video Electronics Standards Association (VESA) to support “plug and play” on PCs when VGA monitors supported multiple video resolutions. They were then incorporated into consumer electronic devices by the Consumer Electronics Association (CEA). The VESA EDID standard has been updated to support digital PC monitors and HDTVs using DVI, HDMI, and more recently DisplayPort. Both VESA and CEA are involved in setting standards for EDIDs. The current version used in consumer electronic gear for the HDMI interface is Enhanced EDID (E-EDID) 1.3 which is based on CEA-861E and incorporated into the HDMI 1.4 specification. The EDID 1.3 specification was released in 2000. The current version used for PCs with the DisplayPort interface is EDID 1.4, released in March 2007. EDID – A Critical Piece of the Audio Visual Experience We take for granted the automation that EDIDs provide. One way to get a sense of the importance of EDIDs is to imagine what a user would have to do if EDIDs did not exist. -

DDC/CI ™ Standard

DDC/CI ™ Standard 39899 Balentine Drive, Suite 125 Phone: 510 651 5122 Newark, CA 94560 Fax: 510 651 5127 Display Data Channel Command Interface Standard Version 1.1 October 29, 2004 Purpose Define an I2C ™ based protocol which operates over the DDC channel to provide interactive control of a display and, optional associated devices. Summary In response to the Plug and Play needs of end-users, VESA has defined the E-DDC standard with different levels of communication. DDC/CI (formerly known as DDC2Bi) provides bi-directional communication between the host and the display. The communication interface is independent of display technology (CRT, LCD, PDP, etc), and is compatible with a number of different video interfaces (VGA, DVI, HDMI, etc). VESA DDC/CI Standard Page 1 of 42 ©Copyright 1997-2004 Video Electronics Standards Association Version 1.1 PREFACE Scope This revision of the DDC/CI Standard is intended to extend the E-DDC standard by providing flexibility and expandability for the DDC implementations in many video interfaces. DDC/CI providing a bi-directional communication channel that can be used, along with the VESA Monitor Command and Control Set (MCCS) standard, to provide interactive control of a display. Intellectual Property Copyright © 1998 - 2004, Video Electronics Standards Association. All rights reserved. While every precaution has been taken in the preparation of this standard, the Video Electronics Standards Association and its contributors assume no responsibility for errors or omissions, and make no warranties, expressed or implied, of functionality or suitability for any purpose. Trademarks All trademarks used within this document are the property of their respective owners.