ECE4623/5623 HW-6 Due: 11/21/12 Prof. M.P. Tull

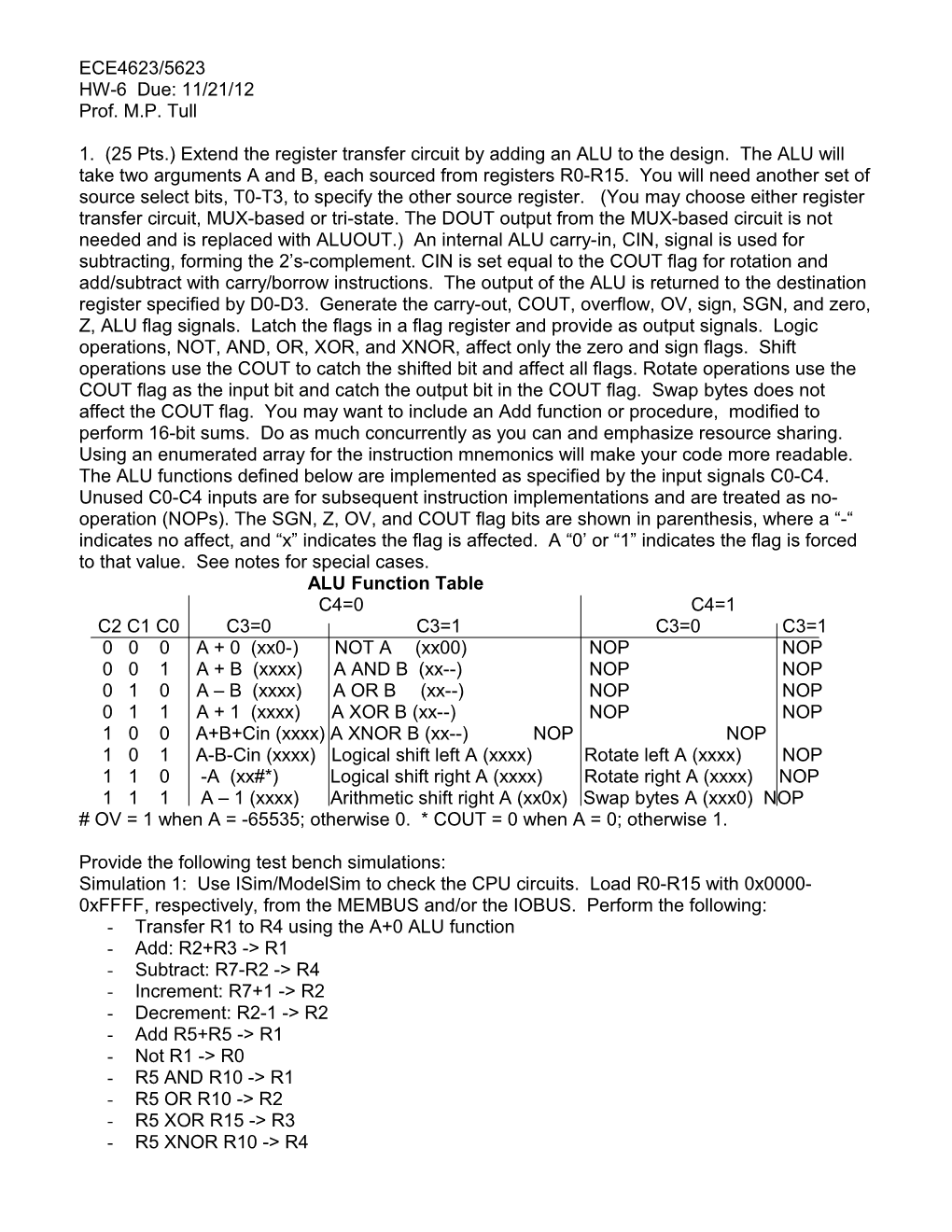

1. (25 Pts.) Extend the register transfer circuit by adding an ALU to the design. The ALU will take two arguments A and B, each sourced from registers R0-R15. You will need another set of source select bits, T0-T3, to specify the other source register. (You may choose either register transfer circuit, MUX-based or tri-state. The DOUT output from the MUX-based circuit is not needed and is replaced with ALUOUT.) An internal ALU carry-in, CIN, signal is used for subtracting, forming the 2’s-complement. CIN is set equal to the COUT flag for rotation and add/subtract with carry/borrow instructions. The output of the ALU is returned to the destination register specified by D0-D3. Generate the carry-out, COUT, overflow, OV, sign, SGN, and zero, Z, ALU flag signals. Latch the flags in a flag register and provide as output signals. Logic operations, NOT, AND, OR, XOR, and XNOR, affect only the zero and sign flags. Shift operations use the COUT to catch the shifted bit and affect all flags. Rotate operations use the COUT flag as the input bit and catch the output bit in the COUT flag. Swap bytes does not affect the COUT flag. You may want to include an Add function or procedure, modified to perform 16-bit sums. Do as much concurrently as you can and emphasize resource sharing. Using an enumerated array for the instruction mnemonics will make your code more readable. The ALU functions defined below are implemented as specified by the input signals C0-C4. Unused C0-C4 inputs are for subsequent instruction implementations and are treated as no- operation (NOPs). The SGN, Z, OV, and COUT flag bits are shown in parenthesis, where a “-“ indicates no affect, and “x” indicates the flag is affected. A “0’ or “1” indicates the flag is forced to that value. See notes for special cases. ALU Function Table C4=0 C4=1 C2 C1 C0 C3=0 C3=1 C3=0 C3=1 0 0 0 A + 0 (xx0-) NOT A (xx00) NOP NOP 0 0 1 A + B (xxxx) A AND B (xx--) NOP NOP 0 1 0 A – B (xxxx) A OR B (xx--) NOP NOP 0 1 1 A + 1 (xxxx) A XOR B (xx--) NOP NOP 1 0 0 A+B+Cin (xxxx) A XNOR B (xx--) NOP NOP 1 0 1 A-B-Cin (xxxx) Logical shift left A (xxxx) Rotate left A (xxxx) NOP 1 1 0 -A (xx#*) Logical shift right A (xxxx) Rotate right A (xxxx) NOP 1 1 1 A – 1 (xxxx) Arithmetic shift right A (xx0x) Swap bytes A (xxx0) NOP # OV = 1 when A = -65535; otherwise 0. * COUT = 0 when A = 0; otherwise 1.

Provide the following test bench simulations: Simulation 1: Use ISim/ModelSim to check the CPU circuits. Load R0-R15 with 0x0000- 0xFFFF, respectively, from the MEMBUS and/or the IOBUS. Perform the following: - Transfer R1 to R4 using the A+0 ALU function - Add: R2+R3 -> R1 - Subtract: R7-R2 -> R4 - Increment: R7+1 -> R2 - Decrement: R2-1 -> R2 - Add R5+R5 -> R1 - Not R1 -> R0 - R5 AND R10 -> R1 - R5 OR R10 -> R2 - R5 XOR R15 -> R3 - R5 XNOR R10 -> R4 ECE4623/5623 HW-6 Due: 11/21/12 Prof. M.P. Tull

Simulation 2: Use ISim/ModelSim to check the CPU circuits. Load R0-R15 with 0x0000- 0xFFFF, respectively, from the MEMBUS and/or the IOBUS. Perform the following:

- Add: R10+R10 -> R4 - Add: R15+R0 w/ CIN -> R3 - Subtract: R0-R1 -> R4 - Subtract: R10-R3 w/ CIN -> R3 - Logical Shift: R10 Left -> R10 - Rotate: R10 Right -> R10 - Arithmetic Shift: R10 Right -> R10 - Logical Shift: R5 Right -> R5 - Rotate: R5 Left -> R5 - Swap bytes: R10 -> R10

Use the Xilinx synthesis tools to synthesize your circuit. Modify your circuit as necessary to eliminate all Error conditions. Most Warnings can be ignored. Look at the synthesis reports and find and record the following:

1. How many adders did your circuit produce? ______

2. What is max clock speed for your circuit? ______

3. What is longest latency in your circuit? ______

4. How many logic blocks (CLBs) were required? ______

Turn in your VHDL, test benches, wave form windows, and snippets from the synthesis reports showing warnings, successful synthesis, and the data for the questions above.