Mr. SIBA KUMAR PANDA M.TECH, VSS UNIVERSITY OF TECHNOLOGY, BURLA, ODISHA

Ca r ee r O bje c t i v e :

To join in a work team of Research environment which will help in my personal development, with the use of the knowledge acquired during my professional experience, as well as during my academic studies and obtain greater experience through practice.

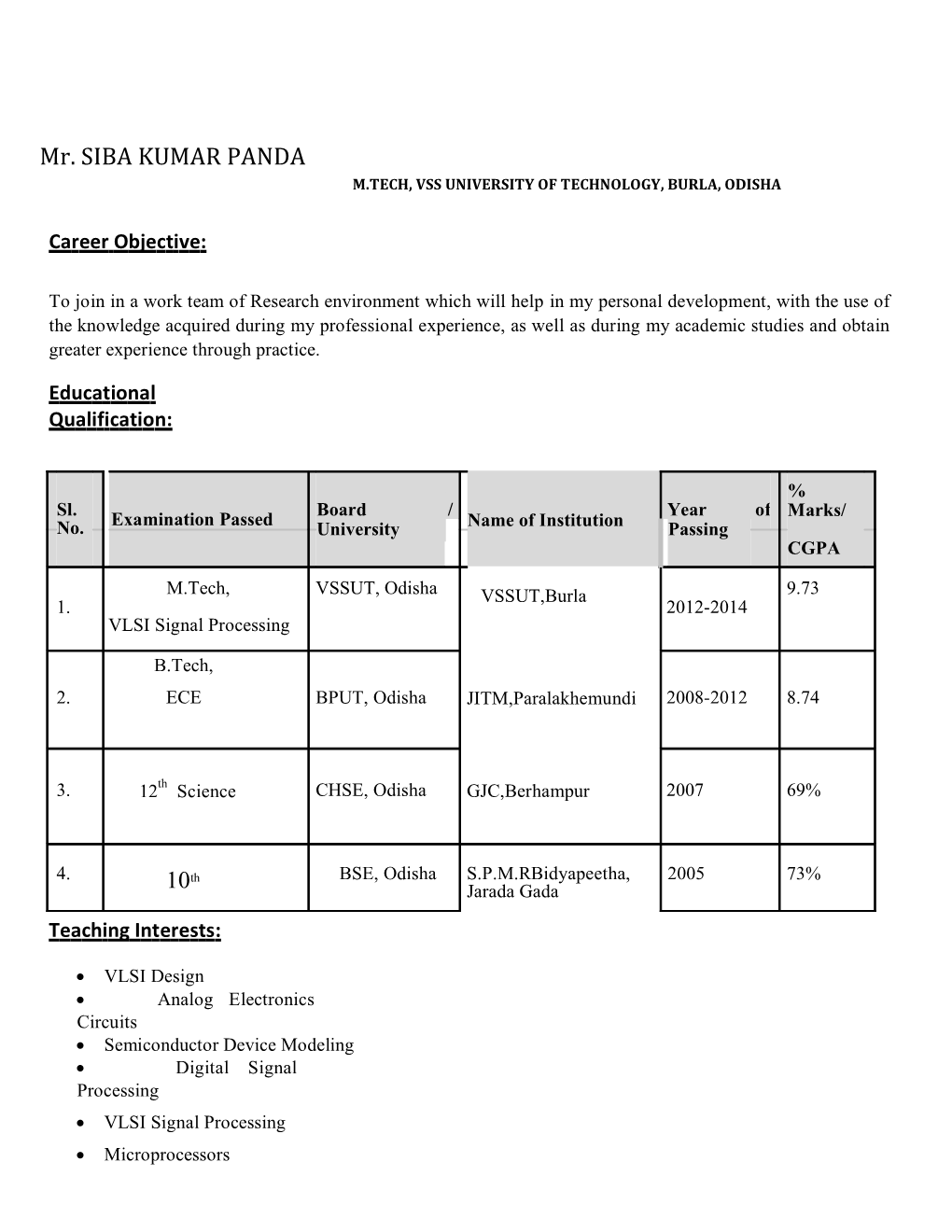

E d uc a t io n a l Qu a l i f i c a t i o n:

% Sl. Board / Year of Examination Passed Marks/ No. University Name of Institution Passing CGPA

M.Tech, VSSUT, Odisha VSSUT,Burla 9.73 1. 2012-2014 VLSI Signal Processing

B.Tech, 2. ECE BPUT, Odisha JITM,Paralakhemundi 2008-2012 8.74

3. 12th Science CHSE, Odisha GJC,Berhampur 2007 69%

4. th BSE, Odisha S.P.M.RBidyapeetha, 2005 73% 10 Jarada Gada T e a c h i ng I n t e r e s t s :

VLSI Design Analog Electronics Circuits Semiconductor Device Modeling Digital Signal Processing VLSI Signal Processing Microprocessors R e s e a r c h I n t e r e s t s: My research interest is in the area of VLSI Signal Processing, an emerging domain that combines the concepts and design of Signal processing and advanced VLSI design. Specifically, my research focuses on various Ultra-wideband (UWB) device design, Semiconductor devices, RF circuit design using CMOS Techniques, VLSI implementation of Vedic Mathematics and VLSI Signal Processing. M . T ec h T h e s i s W o r k: Title: Hybridized Low Noise Amplifier for Low Power Ultra-wideband Applications. Objective: To design and simulate a Novel LNA technique by ADS S/W for low power UWB VLSI Applications and in brief I had designed a hybridized LNA consisting of Resistive current -reuse dual inductive Degeneration at i/p with the CS inductive degeneration technique at o/p which improves the gain, NF,Power Consumption, return losses and Score of the circuit over the ultra-wide band frequency.

Project guide: Prof.(Dr.) Rutuparna Panda (Dept of ETC,VSSUT,BURLA) A c a d e m i c E x p e r ie n c e:

st Working as Assistant Professor in the Dept. of ECE, CENTURION UNIVERSITY, Odisha from 1 July 2014 to till date. Thesis Supervisor for Graduate & Post Graduate students for: CUTM,Jatni,Odisha R e s e a r c h G u i d a n c e: M.Tech Thesis: Completed-03 ,Ongoing- 1 P r o f e s s io n a l A c t i v i t ie s: Life Associate Member – The Institution Of Engineers,India

Pub l i c a t i o ns

Int er nat ional and Nat ional Conf er ence

1. N. Das, S. Jena and S.K. Panda, “FPGA implementation of angle generator for CORDIC based high pass FIR filter design,”Proc National Conference on Mechatronics,Computing and Signal processing(MCSP-2016),Bhubaneswar pp.1- 11, IOSR journal of Electronics and Communication Engineering, July 2016

2. A. Jena and S.K. Panda, “Revision of various Square root algorithm for efficient VLSI Signal Processing applications,”Proc National Conference on Mechatronics,Computing and Signal processing pp.38-41, IOSR journal of Electronics and Communication Engineering, July 2016 3. J.P Mohanty, R. Das and S.K. Panda, “Design and simulation of Convolution using Booth encoded Wallace Tree Multiplier,” Proc National Conference on Mechatronics,Computing and Signal processing pp.42-46, IOSR journal of Electronics and Communication Engineering, July 2016

Int er nat ional Jour nals

4. A. Jena and S.K. Panda,“FPGA-VHDL implementation of Pipelined Square root Circuit for VLSI Signal Processing Applications”, International Journal of Computer Applications 142,pp.20-24, May 2016

5. S.K Panda, A. Sahu “A Novel Vedic Divider Architecture with reduced delay for VLSI applications”, International Journal of Computer Applications (IJCA),Volume 120,No.17,June-2015 .

6. A. Sahu,S.K. Panda ,S. Jena “HDL Implementation and Performance Comparison of an Optimized High Speed Multiplier”, IOSR Journal of VLSI and Signal Processing (IOSR-JVSP),Volume 5, Issue 2, Ver. I ,pp. 10- 19, Mar - April. 2015

7. S.S Pattnaik, R. Das,S.K Panda “Design of Low Power Transversal FIR Filter For VLSI Signal Processing Applications ” International Journal of Emerging Trends in Science and Technology(IJETST) Vol-02,Issue-04,, pp. 2184-2189.,April- 2015

8. P.K Mahapatra,S.K Panda,S.Dalal,S.Pradhan “VHDL implementation of a Novel Low Power Squaring Circuit Using YTVY Algorithm of Vedic Mathematics” International Journal of Emerging Trends in Science and Technology(IJETST) Vol-02,Issue-03,pp .2139-2146, March-2015

9. S.K Panda, A. Padhy,J. Pani,S.R Rout and B.N.Panda “An Optimized procedure for investigation of problem in Marketing Strategy :A Review”, International Journal of Extensive Research(IJER),Vol. 3, pp.17-24,March-2015

10. S.K Panda,R.Das,S.k Raheman and T.R Sahoo, “VLSI implementation of Vedic Multiplier using Urdhva - Tiryakbhyam sutra in VHDL environment:A Novelty”, IOSR Journal of VLSI and Signal Processing (IOSR- JVSP),Volume 5, Issue 1, Ver. III pp 17-24, Jan-Feb.2015

11. S.K Panda, S.S. Pani and B.N Panda, “An Efficient Segmentation Technique for Machine Printed Devanagiri Script: Both line and Word Segmentation”, IOSR Journal of VLSI and Signal Processing (IOSR-JVSP), Volume 5, Issue 1, Ver. I PP 15-21, Jan - Feb. 2015

S e m i n a r , w o r ksh o p a nd F D P a t t e n d e d

12. Participated in National workshop on virtual instrumentation and its application in industry(VIAI-2016) in association with National instrument &Trident Tec lab on 29th April 2016,held at Centurion university of Technology and Management, Bhubaneswar.

13. Participated in Faculty development program on Instructional Design: Models and approaches to enhance Learning from 12th -14th februray, 2016,held at Centurion university of Technology and Management,Paralakhemundi.

14. Participated in IEEE workshop on High Performance Digital Signal processing System Design and implementation during 15th -17th December,2015 held at IIT,Bhubaneswar.

15. Participated in AICTE sponsored Faculty development program on Selected Topics in VLSI Design & Embedded System(STVDES’15) organized by CVRCE,Bhubaneswar from 1st -13th June,2015. 16. Participated in one week AICTE recognized short term course on Embedded System through ICT organized by NITTR,chandigarh from 16th -20th February,2015.

H o n o r s a nd Aw a r ds

Post Graduate Scholarship ( TEQIP ) at Veer Surendra Sai University Of Technology,Odisha (2012-2014). Recipient of Silver Medal for Best Electronics and Telecommunication Engineering Post graduate at VSS University of Technology, Burla, Odisha (2013-2014). T ec h n ic a l sk i l ls: Programming and Software Skills: ADS, XILINX, CADENCE, MICROWIND, 4NEC2, VHDL,

D ecl a r a t i o n:

I hereby declare that the above mentioned information is correct up to my knowledge.

Place: Date: Siba Kumar Panda Signature