Intelligent Medical Device Integration with Real Time Operating System

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Cisco Telepresence TC Software Licensing Information (TC4.1)

Cisco TelePresence TC Software License information guide TC Software FEBRUARY 2011 Legal information and third party copyright and licenses For Cisco TelePresence products using TC software D14767.02 License Information for products using TC Software, TC4 February 2011. 1 © 2010-2011 Cisco Systems, Inc. All rights reserved. www.cisco.com Cisco TelePresence TC Software License information guide ipcalc-1.3, ipcalc-license ...................................................................................... 16 TA - ToC - Hidden Table of Contents iproute-2.6.26, GPLv2 .......................................................................................16 What’stext anchor in iptables-1.4.28, GPLv2......................................................................................16 About this guide ..............................................................................................................4 iputils-s20071127, iputils-bsd-license .................................................... 16 The products covered by this guide: .....................................................4 jpeg lib, jpeg-license ................................................................................................ 17 this guide? User documentation .............................................................................................4 Kmod-*, GPLv2 ........................................................................................................19 Software download ................................................................................................4 -

Embedded Linux Systems with the Yocto Project™

OPEN SOURCE SOFTWARE DEVELOPMENT SERIES Embedded Linux Systems with the Yocto Project" FREE SAMPLE CHAPTER SHARE WITH OTHERS �f, � � � � Embedded Linux Systems with the Yocto ProjectTM This page intentionally left blank Embedded Linux Systems with the Yocto ProjectTM Rudolf J. Streif Boston • Columbus • Indianapolis • New York • San Francisco • Amsterdam • Cape Town Dubai • London • Madrid • Milan • Munich • Paris • Montreal • Toronto • Delhi • Mexico City São Paulo • Sidney • Hong Kong • Seoul • Singapore • Taipei • Tokyo Many of the designations used by manufacturers and sellers to distinguish their products are claimed as trademarks. Where those designations appear in this book, and the publisher was aware of a trademark claim, the designations have been printed with initial capital letters or in all capitals. The author and publisher have taken care in the preparation of this book, but make no expressed or implied warranty of any kind and assume no responsibility for errors or omissions. No liability is assumed for incidental or consequential damages in connection with or arising out of the use of the information or programs contained herein. For information about buying this title in bulk quantities, or for special sales opportunities (which may include electronic versions; custom cover designs; and content particular to your business, training goals, marketing focus, or branding interests), please contact our corporate sales depart- ment at [email protected] or (800) 382-3419. For government sales inquiries, please contact [email protected]. For questions about sales outside the U.S., please contact [email protected]. Visit us on the Web: informit.com Cataloging-in-Publication Data is on file with the Library of Congress. -

RT-ROS: a Real-Time ROS Architecture on Multi-Core Processors

Future Generation Computer Systems 56 (2016) 171–178 Contents lists available at ScienceDirect Future Generation Computer Systems journal homepage: www.elsevier.com/locate/fgcs RT-ROS: A real-time ROS architecture on multi-core processors Hongxing Wei a,1, Zhenzhou Shao b, Zhen Huang a, Renhai Chen d, Yong Guan b, Jindong Tan c,1, Zili Shao d,∗,1 a School of Mechanical Engineering and Automation, Beihang University, Beijing, 100191, PR China b College of Information Engineering, Capital Normal University, Beijing, 100048, PR China c Department of Mechanical, Aerospace, and Biomedical Engineering, The University of Tennessee, Knoxville, TN, 37996-2110, USA d Department of Computing, The Hong Kong Polytechnic University, Hong Kong, China article info a b s t r a c t Article history: ROS, an open-source robot operating system, is widely used and rapidly developed in the robotics Received 6 February 2015 community. However, running on Linux, ROS does not provide real-time guarantees, while real-time tasks Received in revised form are required in many robot applications such as robot motion control. This paper for the first time presents 20 April 2015 a real-time ROS architecture called RT-RTOS on multi-core processors. RT-ROS provides an integrated Accepted 12 May 2015 real-time/non-real-time task execution environment so real-time and non-real-time ROS nodes can be Available online 9 June 2015 separately run on a real-time OS and Linux, respectively, with different processor cores. In such a way, real-time tasks can be supported by real-time ROS nodes on a real-time OS, while non-real-time ROS nodes Keywords: Real-time operating systems on Linux can provide other functions of ROS. -

OS-9 for Intel IXDP425 Board Guide

OS-9® for IXDP425 Board Guide Version 4.7 www.radisys.com Revision A • July 2006 Copyright and publication information Reproduction notice This manual reflects version 4.7 of Microware OS-9. The software described in this document is intended to Reproduction of this document, in part or whole, by any means, be used on a single computer system. RadiSys electrical, mechanical, magnetic, optical, chemical, manual, or Corporation expressly prohibits any reproduction of the otherwise is prohibited, without written permission from RadiSys software on tape, disk, or any other medium except for Microware Communications Software Division, Inc. backup purposes. Distribution of this software, in part or whole, to any other party or on any other system Disclaimer may constitute copyright infringements and misappropriation of trade secrets and confidential The information contained herein is believed to be accurate as of processes which are the property of RadiSys the date of publication. However, RadiSys Corporation will not be Corporation and/or other parties. Unauthorized liable for any damages including indirect or consequential, from distribution of software may cause damages far in use of the OS-9 operating system, Microware-provided software, excess of the value of the copies involved. or reliance on the accuracy of this documentation. The information contained herein is subject to change without notice. July 2006 Copyright ©2006 by RadiSys Corporation All rights reserved. EPC and RadiSys are registered trademarks of RadiSys Corporation. ASM, Brahma, DAI, DAQ, MultiPro, SAIB, Spirit, and ValuePro are trademarks of RadiSys Corporation. DAVID, MAUI, OS-9, OS-9000, and SoftStax are registered trademarks of RadiSys Corporation. -

OPERATING SYSTEMS.Ai

Introduction Aeroflex Gaisler provides LEON and ERC32 users with a wide range of popular embedded operating systems. Ranging from very small footprint task handlers to full featured Real-Time Operating System (RTOS). A summary of available operating systems and their characteristics is outlined below. VxWorks The VxWorks SPARC port supports LEON3/4 and LEON2. Drivers for standard on-chip peripherals are included. The port supports both non-MMU and MMU systems allowing users to program fast and secure applications. Along with the graphical Eclipse based workbench comes the extensive VxWorks documentation. • MMU and non-MMU system support • SMP support (in 6.7 and later) • Networking support (Ethernet 10/100/1000) • UART, Timer, and interrupt controller support • PCI, SpaceWire, CAN, MIL-STD-1553B, I2C and USB host controller support • Eclipse based Workbench • Commercial license ThreadX The ThreadX SPARC port supports LEON3/4 and its standard on-chip peripherals. ThreadX is an easy to learn and understand advanced pico-kernel real-time operating system designed specifically for deeply embedded applications. ThreadX has a rich set of system services for memory allocation and threading. • Non-MMU system support • Bundled with newlib C library • Support for NetX, and USBX ® • Very small footprint • Commercial license Nucleus Nucleus is a real time operating system which offers a rich set of features in a scalable and configurable manner. • UART, Timer, Interrupt controller, Ethernet (10/100/1000) • TCP offloading and zero copy TCP/IP stack (using GRETH GBIT MAC) • USB 2.0 host controller and function controller driver • Small footprint • Commercial license LynxOS LynxOS is an advanced RTOS suitable for high reliability environments. -

FOSS Philosophy 6 the FOSS Development Method 7

1 Published by the United Nations Development Programme’s Asia-Pacific Development Information Programme (UNDP-APDIP) Kuala Lumpur, Malaysia www.apdip.net Email: [email protected] © UNDP-APDIP 2004 The material in this book may be reproduced, republished and incorporated into further works provided acknowledgement is given to UNDP-APDIP. For full details on the license governing this publication, please see the relevant Annex. ISBN: 983-3094-00-7 Design, layout and cover illustrations by: Rezonanze www.rezonanze.com PREFACE 6 INTRODUCTION 6 What is Free/Open Source Software? 6 The FOSS philosophy 6 The FOSS development method 7 What is the history of FOSS? 8 A Brief History of Free/Open Source Software Movement 8 WHY FOSS? 10 Is FOSS free? 10 How large are the savings from FOSS? 10 Direct Cost Savings - An Example 11 What are the benefits of using FOSS? 12 Security 13 Reliability/Stability 14 Open standards and vendor independence 14 Reduced reliance on imports 15 Developing local software capacity 15 Piracy, IPR, and the WTO 16 Localization 16 What are the shortcomings of FOSS? 17 Lack of business applications 17 Interoperability with proprietary systems 17 Documentation and “polish” 18 FOSS SUCCESS STORIES 19 What are governments doing with FOSS? 19 Europe 19 Americas 20 Brazil 21 Asia Pacific 22 Other Regions 24 What are some successful FOSS projects? 25 BIND (DNS Server) 25 Apache (Web Server) 25 Sendmail (Email Server) 25 OpenSSH (Secure Network Administration Tool) 26 Open Office (Office Productivity Suite) 26 LINUX 27 What is Linux? -

Building Embedded Linux Systems ,Roadmap.18084 Page Ii Wednesday, August 6, 2008 9:05 AM

Building Embedded Linux Systems ,roadmap.18084 Page ii Wednesday, August 6, 2008 9:05 AM Other Linux resources from O’Reilly Related titles Designing Embedded Programming Embedded Hardware Systems Linux Device Drivers Running Linux Linux in a Nutshell Understanding the Linux Linux Network Adminis- Kernel trator’s Guide Linux Books linux.oreilly.com is a complete catalog of O’Reilly’s books on Resource Center Linux and Unix and related technologies, including sample chapters and code examples. ONLamp.com is the premier site for the open source web plat- form: Linux, Apache, MySQL, and either Perl, Python, or PHP. Conferences O’Reilly brings diverse innovators together to nurture the ideas that spark revolutionary industries. We specialize in document- ing the latest tools and systems, translating the innovator’s knowledge into useful skills for those in the trenches. Visit con- ferences.oreilly.com for our upcoming events. Safari Bookshelf (safari.oreilly.com) is the premier online refer- ence library for programmers and IT professionals. Conduct searches across more than 1,000 books. Subscribers can zero in on answers to time-critical questions in a matter of seconds. Read the books on your Bookshelf from cover to cover or sim- ply flip to the page you need. Try it today for free. main.title Page iii Monday, May 19, 2008 11:21 AM SECOND EDITION Building Embedded Linux SystemsTomcat ™ The Definitive Guide Karim Yaghmour, JonJason Masters, Brittain Gilad and Ben-Yossef, Ian F. Darwin and Philippe Gerum Beijing • Cambridge • Farnham • Köln • Sebastopol • Taipei • Tokyo Building Embedded Linux Systems, Second Edition by Karim Yaghmour, Jon Masters, Gilad Ben-Yossef, and Philippe Gerum Copyright © 2008 Karim Yaghmour and Jon Masters. -

ENT-AN1144 Application Note SPI Flash Design for Vcore-III

ENT-AN1144 Application Note SPI Flash Design for VCore-III Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not Microsemi Corporate Headquarters rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to One Enterprise, Aliso Viejo, independently determine suitability of any products and to test and verify the same. The information provided by Microsemi CA 92656 USA hereunder is provided “as is, where is” and with all faults, and the entire risk associated with such information is entirely Within the USA: +1 (800) 713-4113 with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP Outside the USA: +1 (949) 380-6100 rights, whether with regard to such information itself or anything described by such information. Information provided in this Fax: +1 (949) 215-4996 document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this Email: [email protected] document or to any products and services at any time without notice. -

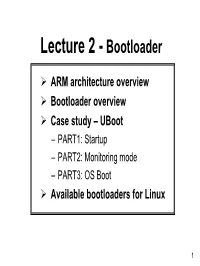

Lecture 2 - Bootloader

Lecture 2 - Bootloader ¾ ARM architecture overview ¾ Bootloader overview ¾ Case study – UBoot – PART1: Startup – PART2: Monitoring mode – PART3: OS Boot ¾ Available bootloaders for Linux 1 ARM Architecture Overview • ARM Operating Modes – User mode: a normal program execution state – FIQ – Fast Interrupt: for fast interrupt handling – IRQ – Normal Interrupt: for general purpose interrupt handling – Supervisor mode (SVC): a protected mode for operating system – Abort mode: when a data or instruction pre-fetch is aborted – Undefined mode: when an undefined instruction is executed – System mode: a privileged user mode for the operating system • ARM Processor States – Arm state: all instructions are 32bits long, word-aligned. – Thumb state: all instructions are 16 bits wide, half-word aligned. – Jazelle state: all instructions are 8 bits wide for Java Bytecode (for v5TEJ only) 2 ARM Architecture Overview • ARM-State Registers 3 ARM Architecture Overview • Thumb-State Registers 4 ARM Architecture Overview • Program Status Register (PSR) ¾ CPSR: Current Program Status Register ¾ SPSR: Saved Program Status Register 5 ARM Architecture Overview • ARM Exception Types – Reset • Hardware reset: when the processor reset pin is asserted • Software reset: by branching to the reset vector (0x0000) – Undefined instruction • the processor cannot recognize the currently execution instruction – Software Interrupt (SWI) • By s/w instruction, to allow a program running in User mode to request privileged operations that are in Supervisor mode – Prefetch Abort -

Timing Comparison of the Real-Time Operating Systems for Small Microcontrollers

S S symmetry Article Timing Comparison of the Real-Time Operating Systems for Small Microcontrollers Ioan Ungurean 1,2 1 Faculty of Electrical Engineering and Computer Science; Stefan cel Mare University of Suceava, 720229 Suceava, Romania; [email protected] 2 MANSiD Integrated Center, Stefan cel Mare University, 720229 Suceava, Romania Received: 9 March 2020; Accepted: 1 April 2020; Published: 8 April 2020 Abstract: In automatic systems used in the control and monitoring of industrial processes, fieldbuses with specific real-time requirements are used. Often, the sensors are connected to these fieldbuses through embedded systems, which also have real-time features specific to the industrial environment in which it operates. The embedded operating systems are very important in the design and development of embedded systems. A distinct class of these operating systems is real-time operating systems (RTOSs) that can be used to develop embedded systems, which have hard and/or soft real-time requirements on small microcontrollers (MCUs). RTOSs offer the basic support for developing embedded systems with applicability in a wide range of fields such as data acquisition, internet of things, data compression, pattern recognition, diversity, similarity, symmetry, and so on. The RTOSs provide basic services for multitasking applications with deterministic behavior on MCUs. The services provided by the RTOSs are task management and inter-task synchronization and communication. The selection of the RTOS is very important in the development of the embedded system with real-time requirements and it must be based on the latency in the handling of the critical operations triggered by internal or external events, predictability/determinism in the execution of the RTOS primitives, license costs, and memory footprint. -

GNU / Linux and Free Software

GNU / Linux and Free Software GNU / Linux and Free Software An introduction Michael Opdenacker Free Electrons http://free-electrons.com Created with OpenOffice.org 2.x GNU / Linux and Free Software © Copyright 2004-2007, Free Electrons Creative Commons Attribution-ShareAlike 2.5 license http://free-electrons.com Sep 15, 2009 1 Rights to copy Attribution ± ShareAlike 2.5 © Copyright 2004-2007 You are free Free Electrons to copy, distribute, display, and perform the work [email protected] to make derivative works to make commercial use of the work Document sources, updates and translations: Under the following conditions http://free-electrons.com/articles/freesw Attribution. You must give the original author credit. Corrections, suggestions, contributions and Share Alike. If you alter, transform, or build upon this work, you may distribute the resulting work only under a license translations are welcome! identical to this one. For any reuse or distribution, you must make clear to others the license terms of this work. Any of these conditions can be waived if you get permission from the copyright holder. Your fair use and other rights are in no way affected by the above. License text: http://creativecommons.org/licenses/by-sa/2.5/legalcode GNU / Linux and Free Software © Copyright 2004-2007, Free Electrons Creative Commons Attribution-ShareAlike 2.5 license http://free-electrons.com Sep 15, 2009 2 Contents Unix and its history Free Software licenses and legal issues Free operating systems Successful project highlights Free Software -

Redboot · User Manual

RedBoot · User Manual RedBoot · User Manual Important hints Thank you very much for purchasing a Garz & Fricke product. Our products are dedicated to professional use and therefore we suppose extended technical knowledge and practice in working with such products. The information in this manual is subject to technical changes, particularly as a result of continuous product upgrades. Thus this manual only reflects the technical status of the products at the time of printing. Before design-in the device into your or your customer’s product, please verify that this document and the therein described specification is the latest revision and matches to the PCB version. We highly recommend contacting our technical sales team prior to any activity of that kind. A good way getting the latest information is to check the release notes of each product and/or service. Please refer to the chapter [Online Support]. The attached documentation does not entail any guarantee on the part of Garz & Fricke GmbH with respect to technical processes described in the manual or any product characteristics set out in the manual. We do not accept any liability for any printing errors or other inaccuracies in the manual unless it can be proven that we are aware of such errors or inaccuracies or that we are unaware of these as a result of gross negligence and Garz & Fricke has failed to eliminate these errors or inaccuracies for this reason. Garz & Fricke GmbH expressly informs that this manual only contains a general description of technical processes and instructions which may not be applicable in every individual case.