I TEST CARD INTERFACE

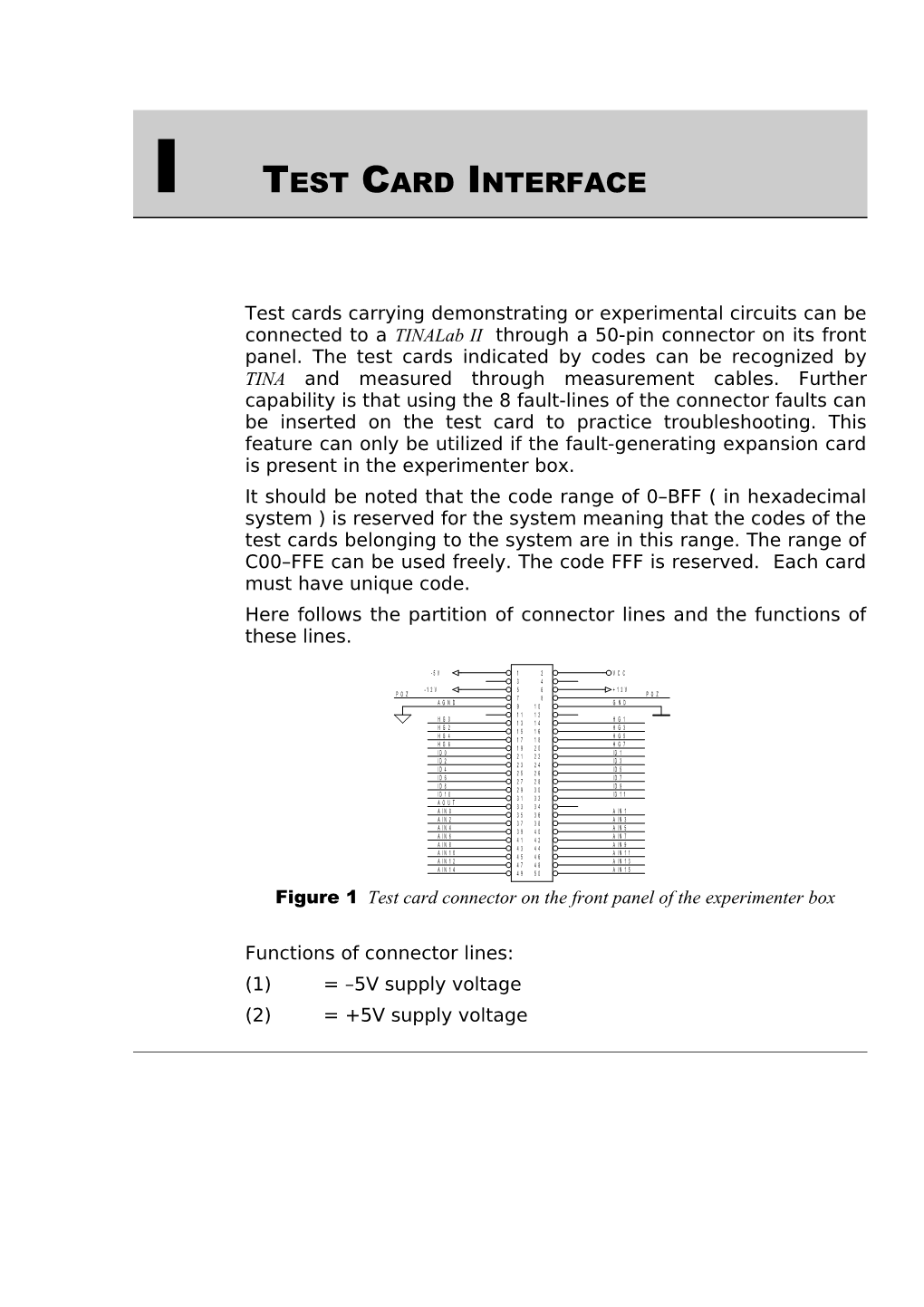

Test cards carrying demonstrating or experimental circuits can be connected to a TINALab II through a 50-pin connector on its front panel. The test cards indicated by codes can be recognized by TINA and measured through measurement cables. Further capability is that using the 8 fault-lines of the connector faults can be inserted on the test card to practice troubleshooting. This feature can only be utilized if the fault-generating expansion card is present in the experimenter box. It should be noted that the code range of 0–BFF ( in hexadecimal system ) is reserved for the system meaning that the codes of the test cards belonging to the system are in this range. The range of C00–FFE can be used freely. The code FFF is reserved. Each card must have unique code. Here follows the partition of connector lines and the functions of these lines.

- 5 V 1 2 V C C 3 4 - 1 2 V 5 6 + 1 2 V P O Z P O Z 7 8 A G N D G N D 9 1 0 1 1 1 2 H G 0 H G 1 1 3 1 4 H G 2 H G 3 1 5 1 6 H G 4 H G 5 1 7 1 8 H G 6 H G 7 1 9 2 0 I D 0 I D 1 2 1 2 2 I D 2 I D 3 2 3 2 4 I D 4 I D 5 2 5 2 6 I D 6 I D 7 2 7 2 8 I D 8 I D 9 2 9 3 0 I D 1 0 I D 1 1 3 1 3 2 A O U T 3 3 3 4 A I N 0 A I N 1 3 5 3 6 A I N 2 A I N 3 3 7 3 8 A I N 4 A I N 5 3 9 4 0 A I N 6 A I N 7 4 1 4 2 A I N 8 A I N 9 4 3 4 4 A I N 1 0 A I N 1 1 4 5 4 6 A I N 1 2 A I N 1 3 4 7 4 8 A I N 1 4 A I N 1 5 4 9 5 0 Figure 1 Test card connector on the front panel of the experimenter box

Functions of connector lines: (1) = –5V supply voltage (2) = +5V supply voltage (5) = –12V supply voltage (6) = 12V supply voltage (9) = analog ground (10) = digital ground (13–20) = HG0–HG7 fault-lines. The circuit diagram of the relay network connected to the fault-lines is shown in Figure 2. The operation of the relay network can be done through TINA with the “Map to Hardware” command in the View/Exam Manager window. (21–32) = ID0–ID11 identification lines serving to identify the test cards. These cards are identified by 12 bit codes. The lines ID0 and ID11 correspond to the LSB and MSB of the code, respectively. In default all the bits are 1 to produce 0 the corresponding line is to be connected to digital ground. The code is recognized by TINA in the following way: If the user wish to load the circuit [testcard], TINA reads in the code of the test card and tries to load the TC-XXXX.SCH file from subdirectory TINA\MEAS_SCH where XXXX means the hexadecimal code. Assuming that

ID0 = 0, ID11 = 0 (the first and last identification lines are grounded) and the other identification bits are 1 the file searched for by TINA is TC-07FE.SCH. (33) = AOUT: analog output of the data acquisition card serving to supply the excitation to the test card. (35–50) = analog input channels. Using the experimenter box the analog input of the card can be connected to any of the 16 channels. Thus the analog channels make possible the measurement of 16 nodes on the test card by TINA. Measurement can be done through one channel at a time. The channel is selected through TINA referring to the node numbers (1–16) defined in the program. H G 0

H G 1

K 1 K 2

H G 2 V C C V C C H K 0 H K 1

K 3 R 2

V C C H K 2 1 0 k

H G 3

H G 4

K 4 K 5

H G 5 V C C V C C H K 3 H K 4

K 6 R 1

V C C H K 5 1 k

H G 6

H G 7

K 7 K 8

V C C V C C H K 6 H K 7

Figure 2 Fault generating combination network

The general scheme of the test card is shown in Figure 3/a, while the circuit diagram of DC1 test card can be seen in Figure 3/b. The latter is a good example of how to make either an open or a short circuit.

C O N N E C T O R H I B A G E N E R A T O R

S D I O 0 S D I O 0 S D I O 0 S D I O 1 S D I O 1 S D I O 1 - D I O E N ? - D I O E N ? - D I O E N ? - D I O R H G [ 0 . . 7 ] - D I O R - D I O R H G [ 0 . . 7 ] - D I O W - D I O W - D I O W

D I O [ 0 . . 7 ] D I O [ 0 . . 7 ] D I O [ 0 . . 7 ]

E X T B O X C . S C H H I B A G E N . S C H

H G [ 0 . . 7 ] Figure 3/a General scheme of the test cards A I N [ 0 . . 1 5 ] A I N [ 0 . . 1 5 ] A I N 0 A O U T A I N 1 A I N 2 A I N 3 A I N 4

H G 0

R 1 R I D [ 0 . . 1 1 ] I D [ 0 . . 1 1 ] H G 1

J P 2 H G 2 1 2 I D 0 3 4 H G 6 5 6 H G 7 T C S W

H G 3 I D 1 I D 2 H G 4 I D 3 I D 5 I D 6 R 2 R 3 I D 7 R R I D 8 I D 9 I D 1 0 I D 1 1 H G [ 0 . . 7 ] H G [ 0 . . 7 ]

A G N D

G N D Figure 3/b Circuit diagram of DC1 test card

The following circuit schemes (Figures 4/a–d) show the actual circuit with the corresponding jumper and switch settings. The numbers at the jumper settings mean, that the corresponding pins are connected. The switches (SW #1–8) in TINA correspond to the K1–8 relays of Figure 2.

Figure 4/a (TC-0010.SCH) Good circuit Figure 4/b (TC-0010.SCH) Fault insertion

Figure 4/c (TC-0011.SCH) Good circuit Figure 4/d (TC-0011.SCH) Fault insertion