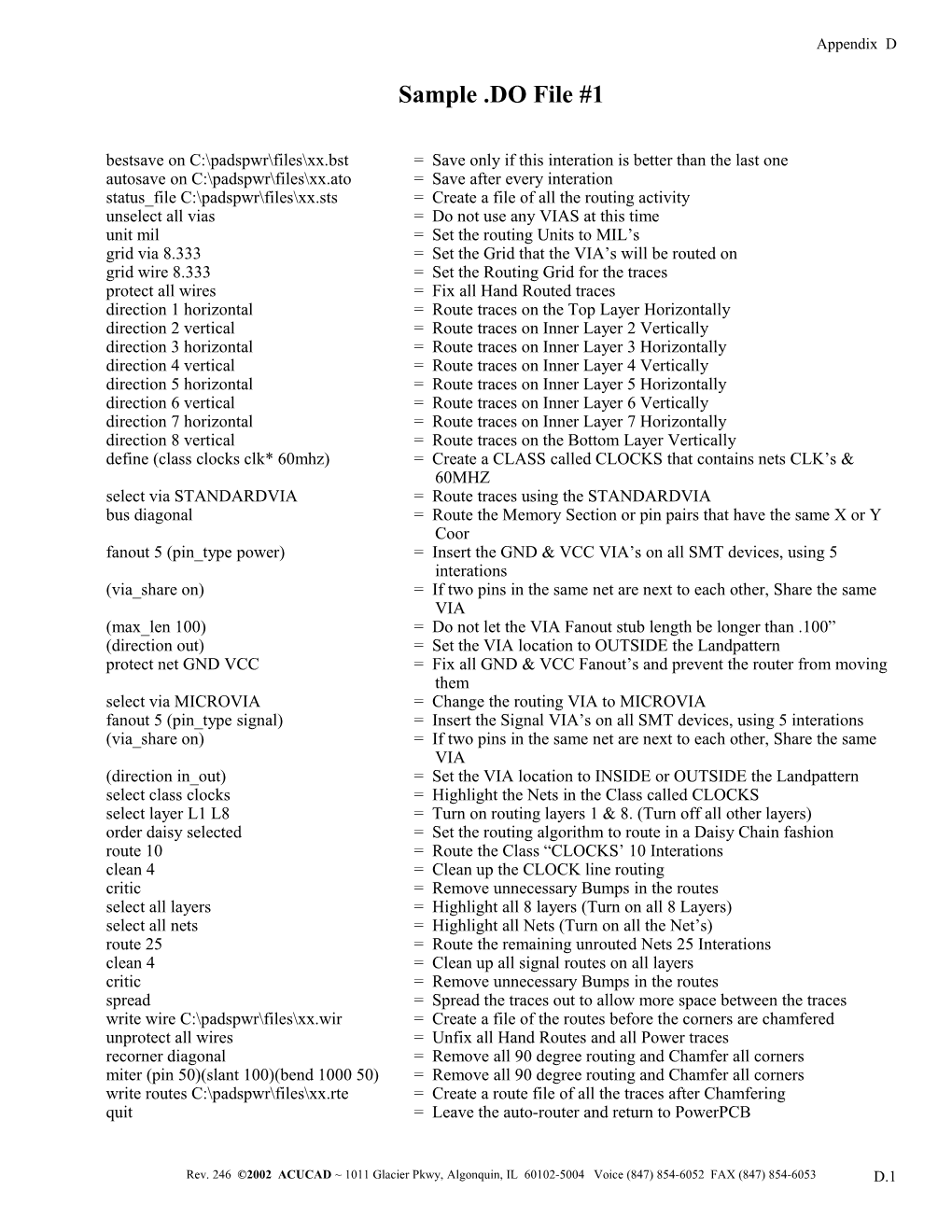

Appendix D

Sample .DO File #1 bestsave on C:\padspwr\files\xx.bst = Save only if this interation is better than the last one autosave on C:\padspwr\files\xx.ato = Save after every interation status_file C:\padspwr\files\xx.sts = Create a file of all the routing activity unselect all vias = Do not use any VIAS at this time unit mil = Set the routing Units to MIL’s grid via 8.333 = Set the Grid that the VIA’s will be routed on grid wire 8.333 = Set the Routing Grid for the traces protect all wires = Fix all Hand Routed traces direction 1 horizontal = Route traces on the Top Layer Horizontally direction 2 vertical = Route traces on Inner Layer 2 Vertically direction 3 horizontal = Route traces on Inner Layer 3 Horizontally direction 4 vertical = Route traces on Inner Layer 4 Vertically direction 5 horizontal = Route traces on Inner Layer 5 Horizontally direction 6 vertical = Route traces on Inner Layer 6 Vertically direction 7 horizontal = Route traces on Inner Layer 7 Horizontally direction 8 vertical = Route traces on the Bottom Layer Vertically define (class clocks clk* 60mhz) = Create a CLASS called CLOCKS that contains nets CLK’s & 60MHZ select via STANDARDVIA = Route traces using the STANDARDVIA bus diagonal = Route the Memory Section or pin pairs that have the same X or Y Coor fanout 5 (pin_type power) = Insert the GND & VCC VIA’s on all SMT devices, using 5 interations (via_share on) = If two pins in the same net are next to each other, Share the same VIA (max_len 100) = Do not let the VIA Fanout stub length be longer than .100” (direction out) = Set the VIA location to OUTSIDE the Landpattern protect net GND VCC = Fix all GND & VCC Fanout’s and prevent the router from moving them select via MICROVIA = Change the routing VIA to MICROVIA fanout 5 (pin_type signal) = Insert the Signal VIA’s on all SMT devices, using 5 interations (via_share on) = If two pins in the same net are next to each other, Share the same VIA (direction in_out) = Set the VIA location to INSIDE or OUTSIDE the Landpattern select class clocks = Highlight the Nets in the Class called CLOCKS select layer L1 L8 = Turn on routing layers 1 & 8. (Turn off all other layers) order daisy selected = Set the routing algorithm to route in a Daisy Chain fashion route 10 = Route the Class “CLOCKS’ 10 Interations clean 4 = Clean up the CLOCK line routing critic = Remove unnecessary Bumps in the routes select all layers = Highlight all 8 layers (Turn on all 8 Layers) select all nets = Highlight all Nets (Turn on all the Net’s) route 25 = Route the remaining unrouted Nets 25 Interations clean 4 = Clean up all signal routes on all layers critic = Remove unnecessary Bumps in the routes spread = Spread the traces out to allow more space between the traces write wire C:\padspwr\files\xx.wir = Create a file of the routes before the corners are chamfered unprotect all wires = Unfix all Hand Routes and all Power traces recorner diagonal = Remove all 90 degree routing and Chamfer all corners miter (pin 50)(slant 100)(bend 1000 50) = Remove all 90 degree routing and Chamfer all corners write routes C:\padspwr\files\xx.rte = Create a route file of all the traces after Chamfering quit = Leave the auto-router and return to PowerPCB

Rev. 246 ©2002 ACUCAD ~ 1011 Glacier Pkwy, Algonquin, IL 60102-5004 Voice (847) 854-6052 FAX (847) 854-6053 D.1 Appendix D

Sample .DO File #2 bestsave on \padspwr\files\xx.bst = Save only if this interation is better than the last one autosave on \padspwr\files\xx.ato = Save after every interation status_file C:\padspwr\files\xx.sts = Create a file of all the routing activity unselect all vias = Do not use any VIAS at this time unit mil = Set the routing Units to MIL’s grid via 8.333 = Set the Grid that the VIA’s will be routed on grid wire 8.333 = Set the Routing Grid for the traces protect all wires = Fix all Hand Routed traces direction 1 horizontal = Route traces on the Top Layer Horizontally direction 2 vertical = Route traces on Inner Layer 2 Vertically direction 3 horizontal = Route traces on Inner Layer 3 Horizontally direction 4 vertical = Route traces on Inner Layer 4 Vertically direction 5 horizontal = Route traces on Inner Layer 5 Horizontally direction 6 vertical = Route traces on Inner Layer 6 Vertically direction 7 horizontal = Route traces on Inner Layer 7 Horizontally direction 8 vertical = Route traces on the Bottom Layer Vertically select via MICROVIA = Route traces using the MICROVIA smart_route = Includes: Bus Diagonal, Fanout 5, Route 25, Clean 4 testpoint (use_via TESTVIA)(center_center 100) = Add Testpoints critic = Remove unnecessary Bumps in the routes spread = Spread the traces out to allow more space between the traces report testpoint C:\padspwr\files\xx.rpt = Test Point Report report unconnect C:\padspwr\files\xx.non = Unconnected route report write wire C:\padspwr\files\xx.wir = Create a file of the routes before the corners are chamfered unprotect all wires = Unfix all Hand Routes and all Power traces recorner diagonal = Remove all 90 degree routing and Chamfer all corners miter (pin 50)(slant 100)(bend 1000 50) = Remove all 90 degree routing and Chamfer all corners write routes C:\padspwr\files\xx.rte = Create a route file of all the traces after Chamfering quit = Leave the auto-router and return to PowerPCB

D.2 Rev. 246 ©2002 ACUCAD ~ 1011 Glacier Pkwy, Algonquin, IL 60102-5004 Voice (847) 854-6052 FAX (847) 854-6053