Libbfd the Binary File Descriptor Library

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

The GNU Linker

The GNU linker ld (GNU Binutils) Version 2.37 Steve Chamberlain Ian Lance Taylor Red Hat Inc [email protected], [email protected] The GNU linker Edited by Jeffrey Osier ([email protected]) Copyright c 1991-2021 Free Software Foundation, Inc. Permission is granted to copy, distribute and/or modify this document under the terms of the GNU Free Documentation License, Version 1.3 or any later version published by the Free Software Foundation; with no Invariant Sections, with no Front-Cover Texts, and with no Back-Cover Texts. A copy of the license is included in the section entitled \GNU Free Documentation License". i Table of Contents 1 Overview :::::::::::::::::::::::::::::::::::::::: 1 2 Invocation ::::::::::::::::::::::::::::::::::::::: 3 2.1 Command-line Options ::::::::::::::::::::::::::::::::::::::::: 3 2.1.1 Options Specific to i386 PE Targets :::::::::::::::::::::: 40 2.1.2 Options specific to C6X uClinux targets :::::::::::::::::: 47 2.1.3 Options specific to C-SKY targets :::::::::::::::::::::::: 48 2.1.4 Options specific to Motorola 68HC11 and 68HC12 targets :::::::::::::::::::::::::::::::::::::::::::::::::::::::::::: 48 2.1.5 Options specific to Motorola 68K target :::::::::::::::::: 48 2.1.6 Options specific to MIPS targets ::::::::::::::::::::::::: 49 2.1.7 Options specific to PDP11 targets :::::::::::::::::::::::: 49 2.2 Environment Variables :::::::::::::::::::::::::::::::::::::::: 50 3 Linker Scripts:::::::::::::::::::::::::::::::::: 51 3.1 Basic Linker Script Concepts :::::::::::::::::::::::::::::::::: 51 3.2 Linker Script -

Using the GNU Compiler Collection (GCC)

Using the GNU Compiler Collection (GCC) Using the GNU Compiler Collection by Richard M. Stallman and the GCC Developer Community Last updated 23 May 2004 for GCC 3.4.6 For GCC Version 3.4.6 Published by: GNU Press Website: www.gnupress.org a division of the General: [email protected] Free Software Foundation Orders: [email protected] 59 Temple Place Suite 330 Tel 617-542-5942 Boston, MA 02111-1307 USA Fax 617-542-2652 Last printed October 2003 for GCC 3.3.1. Printed copies are available for $45 each. Copyright c 1988, 1989, 1992, 1993, 1994, 1995, 1996, 1997, 1998, 1999, 2000, 2001, 2002, 2003, 2004 Free Software Foundation, Inc. Permission is granted to copy, distribute and/or modify this document under the terms of the GNU Free Documentation License, Version 1.2 or any later version published by the Free Software Foundation; with the Invariant Sections being \GNU General Public License" and \Funding Free Software", the Front-Cover texts being (a) (see below), and with the Back-Cover Texts being (b) (see below). A copy of the license is included in the section entitled \GNU Free Documentation License". (a) The FSF's Front-Cover Text is: A GNU Manual (b) The FSF's Back-Cover Text is: You have freedom to copy and modify this GNU Manual, like GNU software. Copies published by the Free Software Foundation raise funds for GNU development. i Short Contents Introduction ...................................... 1 1 Programming Languages Supported by GCC ............ 3 2 Language Standards Supported by GCC ............... 5 3 GCC Command Options ......................... -

The “Stabs” Debug Format

The \stabs" debug format Julia Menapace, Jim Kingdon, David MacKenzie Cygnus Support Cygnus Support Revision TEXinfo 2017-08-23.19 Copyright c 1992{2021 Free Software Foundation, Inc. Contributed by Cygnus Support. Written by Julia Menapace, Jim Kingdon, and David MacKenzie. Permission is granted to copy, distribute and/or modify this document under the terms of the GNU Free Documentation License, Version 1.3 or any later version published by the Free Software Foundation; with no Invariant Sections, with no Front-Cover Texts, and with no Back-Cover Texts. A copy of the license is included in the section entitled \GNU Free Documentation License". i Table of Contents 1 Overview of Stabs ::::::::::::::::::::::::::::::: 1 1.1 Overview of Debugging Information Flow ::::::::::::::::::::::: 1 1.2 Overview of Stab Format ::::::::::::::::::::::::::::::::::::::: 1 1.3 The String Field :::::::::::::::::::::::::::::::::::::::::::::::: 2 1.4 A Simple Example in C Source ::::::::::::::::::::::::::::::::: 3 1.5 The Simple Example at the Assembly Level ::::::::::::::::::::: 4 2 Encoding the Structure of the Program ::::::: 7 2.1 Main Program :::::::::::::::::::::::::::::::::::::::::::::::::: 7 2.2 Paths and Names of the Source Files :::::::::::::::::::::::::::: 7 2.3 Names of Include Files:::::::::::::::::::::::::::::::::::::::::: 8 2.4 Line Numbers :::::::::::::::::::::::::::::::::::::::::::::::::: 9 2.5 Procedures ::::::::::::::::::::::::::::::::::::::::::::::::::::: 9 2.6 Nested Procedures::::::::::::::::::::::::::::::::::::::::::::: 11 2.7 Block Structure -

Zilog’S Ez80acclaim!™ Product Family, Which Offers On-Chip Flash Versions of Zilog’S Ez80® • 3.0–3.6 V Supply Voltage with 5 V Tolerant Inputs Processor Core

eZ80Acclaim!™ Flash Microcontrollers eZ80F91 Product Brief PB013502-0104 Product Block Diagram • I2C with independent clock rate generator • SPI with independent clock rate generator eZ80F91 MCU • Four Counter/Timers with prescalers supporting event counting, input capture, output compare, and 256 KB Flash + 32-Bit GPIO PWM modes 512 B Flash • Watch-Dog Timer with internal RC clocking 10/100 Mbps option 8KB SRAM Ethernet MAC • Real-time clock with on-chip 32kHz oscillator, 8KB Frame Buffer selectable 50/60Hz input, and separate RTC_VDD pin for battery backup. Infrared 2 • Glueless external memory interface with 4 Chip- Encoder/ 2 UART I C SPI Selects/Wait-State Generators and external WAIT Decoder input pin. Supports Intel and Motorola buses. Real-Time • JTAG Interface supporting emulation features 4 PRT WDT Clock • Low-power PLL and on-chip oscillator • Programmable-priority vectored interrupts, non- 4 CS JTAG ZDI PLL maskable interrupts, and interrupt controller +WSG • New DMA-like eZ80® CPU instructions • Power management features supporting HALT/ Features SLEEP modes and selective peripheral power- down controls The eZ80F91 microcontroller is a member of • 144-pin BGA or 144-pin LQFP package ZiLOG’s eZ80Acclaim!™ product family, which offers on-chip Flash versions of ZiLOG’s eZ80® • 3.0–3.6 V supply voltage with 5 V tolerant inputs processor core. The eZ80F91 offers the following • Operating Temperature Ranges: features: – Standard: 0ºC to +70ºC • 50MHz High-Performance eZ80® CPU – Extended: –40ºC to +105ºC • 256 KB Flash Program Memory plus extra 512B device configuration Flash memory General Description • 32 bits of General-Purpose I/O The eZ80F91 device is an industry first, featuring a • 16K B total on-chip high-speed SRAM: high-performance 8-bit microcontroller with an integrated 10/100 BaseT Ethernet Media Access – 8KB for general-purpose use controller (EMAC). -

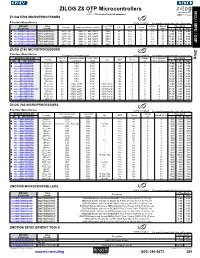

ZILOG Z8 OTP Microcontrollers MCU / MPU / DSP This Product Is Rohs Compliant

ZILOG Z8 OTP Microcontrollers DSP MPU / MCU / This product is RoHS compliant. ZILOG EZ80 MICROPROCESSORS ♦ Surface Mount Device For quantities greater than listed, call for quote. MOUSER Zilog Core CPU Voltage Speed Price Each Package Communications Controller I/O WDT Timers STOCK NO. Part No. Used (V) (MHz) 1 25 100 ♦ 692-EZ80L92AZ020EG EZ80L92AZ020EC LQFP-100 DMA, I2C, SPI, UART EZ80 24 Yes 6 3.3 20 9.29 9.10 8.63 ♦ 692-EZ80L92AZ020SG EZ80L92AZ020SC LQFP-100 DMA, I2C, SPI, UART EZ80 24 Yes 6 3.3 20 8.08 7.78 7.50 ♦ 692-EZ80L92AZ050EG EZ80L92AZ050EC LQFP-100 DMA, I2C, SPI, UART EZ80 24 Yes 6 3.3 50 10.21 9.75 9.49 ♦ 692-EZ80L92AZ050SG EZ80L92AZ050SC LQFP-100 DMA, I2C, SPI, UART EZ80 24 Yes 6 3.3 50 8.89 8.54 8.26 ♦ 692-EZ80190AZ050SG EZ80190AZ050SC LQFP-100 DMA, I2C, SPI, UART EZ80 32 Yes 6 3.3 50 12.03 11.59 11.17 ♦ 692-EZ80190AZ050EG EZ80190AZ050EC LQFP-100 DMA, I2C, SPI, UART EZ80 32 Yes 6 3.3 50 13.82 13.28 12.84 ZILOG Z180 MICROPROCESSORS Zilog ♦Surface Mount Device *See above for development tools. For quantities greater than listed, call for quote. MOUSER STOCK NO. Speed Communications Core CPU Voltage Development Price Each Package I/O WDT Timers Mfr. Mfr. Part No. (MHz) Controller Used (V) Tools Available 1 25 100 ♦ 692-Z8018006VSG PLCC-68 6 CPU Z180 - No 2 5 - 8.40 7.36 6.01 ♦ 692-Z8018006VEG PLCC-68 6 CPU Z180 - No 2 5 - 10.00 8.55 7.14 692-Z8018006PSG DIP-64 6 CPU Z180 - No 2 5 - 8.40 7.36 6.01 692-Z8018006PEG DIP-64 6 CPU Z180 - No 2 5 - 10.00 8.55 7.14 692-Z8018008PSG DIP-64 8 CPU Z180 - No 2 5 - 8.75 7.38 6.25 ♦ 692-Z8018008VSG -

Emerging Technologies Multi/Parallel Processing

Emerging Technologies Multi/Parallel Processing Mary C. Kulas New Computing Structures Strategic Relations Group December 1987 For Internal Use Only Copyright @ 1987 by Digital Equipment Corporation. Printed in U.S.A. The information contained herein is confidential and proprietary. It is the property of Digital Equipment Corporation and shall not be reproduced or' copied in whole or in part without written permission. This is an unpublished work protected under the Federal copyright laws. The following are trademarks of Digital Equipment Corporation, Maynard, MA 01754. DECpage LN03 This report was produced by Educational Services with DECpage and the LN03 laser printer. Contents Acknowledgments. 1 Abstract. .. 3 Executive Summary. .. 5 I. Analysis . .. 7 A. The Players . .. 9 1. Number and Status . .. 9 2. Funding. .. 10 3. Strategic Alliances. .. 11 4. Sales. .. 13 a. Revenue/Units Installed . .. 13 h. European Sales. .. 14 B. The Product. .. 15 1. CPUs. .. 15 2. Chip . .. 15 3. Bus. .. 15 4. Vector Processing . .. 16 5. Operating System . .. 16 6. Languages. .. 17 7. Third-Party Applications . .. 18 8. Pricing. .. 18 C. ~BM and Other Major Computer Companies. .. 19 D. Why Success? Why Failure? . .. 21 E. Future Directions. .. 25 II. Company/Product Profiles. .. 27 A. Multi/Parallel Processors . .. 29 1. Alliant . .. 31 2. Astronautics. .. 35 3. Concurrent . .. 37 4. Cydrome. .. 41 5. Eastman Kodak. .. 45 6. Elxsi . .. 47 Contents iii 7. Encore ............... 51 8. Flexible . ... 55 9. Floating Point Systems - M64line ................... 59 10. International Parallel ........................... 61 11. Loral .................................... 63 12. Masscomp ................................. 65 13. Meiko .................................... 67 14. Multiflow. ~ ................................ 69 15. Sequent................................... 71 B. Massively Parallel . 75 1. Ametek.................................... 77 2. Bolt Beranek & Newman Advanced Computers ........... -

The Birth, Evolution and Future of Microprocessor

The Birth, Evolution and Future of Microprocessor Swetha Kogatam Computer Science Department San Jose State University San Jose, CA 95192 408-924-1000 [email protected] ABSTRACT timed sequence through the bus system to output devices such as The world's first microprocessor, the 4004, was co-developed by CRT Screens, networks, or printers. In some cases, the terms Busicom, a Japanese manufacturer of calculators, and Intel, a U.S. 'CPU' and 'microprocessor' are used interchangeably to denote the manufacturer of semiconductors. The basic architecture of 4004 same device. was developed in August 1969; a concrete plan for the 4004 The different ways in which microprocessors are categorized are: system was finalized in December 1969; and the first microprocessor was successfully developed in March 1971. a) CISC (Complex Instruction Set Computers) Microprocessors, which became the "technology to open up a new b) RISC (Reduced Instruction Set Computers) era," brought two outstanding impacts, "power of intelligence" and "power of computing". First, microprocessors opened up a new a) VLIW(Very Long Instruction Word Computers) "era of programming" through replacing with software, the b) Super scalar processors hardwired logic based on IC's of the former "era of logic". At the same time, microprocessors allowed young engineers access to "power of computing" for the creative development of personal 2. BIRTH OF THE MICROPROCESSOR computers and computer games, which in turn led to growth in the In 1970, Intel introduced the first dynamic RAM, which increased software industry, and paved the way to the development of high- IC memory by a factor of four. -

Converting a Microcontroller Lab from the Freescale S12 to the Atmel Atmega32 Processor

ASEE-NMWSC2013-0025 Converting a Microcontroller Lab From The Freescale S12 to the Atmel ATmega32 Processor Christopher R. Carroll University of Minnesota Duluth [email protected] Abstract During the summer of 2013, the laboratory supporting the microcontroller course at the University of Minnesota Duluth was completely re-implemented. For the last several years, the processor that has been used was the Freescale S12, a popular 16-bit microcontroller with a long ancestral history 1. The recent popularity of the Atmel AVR series of microcontrollers, as used in the Arduino microcomputers, for example, has prompted a change in the lab to use Atmel’s ATmega32 microcontroller, an 8-bit member of the AVR family of microcontrollers 2,3 . The new processor has a fundamentally different architecture than that used in the past, but the input/output resources available are much the same. This paper addresses issues that will be faced in the conversion when the course is taught with the new lab hardware for the first time in the Fall. At the very fundamental level, the S12 and ATmega32 differ in architecture. The S12 is a Princeton architecture computer (single memory for both program and data), while the ATmega32 is a Harvard architecture computer (separate program and data memories). The S12 is clearly a CISC machine (Complex Instruction Set Computer) while the ATmega32 is clearly a RISC machine (Reduced Instruction Set Computer). These differences will affect how the microcontroller course is taught when it is offered in the Fall using this new lab. Fortunately, however, the collection of input/output devices in the AVR microcontrollers mimics closely what is found in the S12, so that many of the existing lab exercises will be used again with only minor tweaking. -

Escuela Politécnica Superior De Jaén

UNIVERSIDAD DE JAÉN ESCUELA POLITÉCNICA SUPERIOR DE JAÉN Trabajo Fin de Grado DATALOGGER CON ENLACE BLUETOOTH A SISTEMA ANDROID Alumno: Juan Miguel Bejarano Bueno Tutor: Prof. D. Luis Miguel Nieto Nieto Dpto: Ingeniería Electrónica y Automática Escuela Politécnica Superior Jaén de Area: Tecnología Electrónica Septiembre, 2015 Juan Miguel Bejarano Bueno Datalogger con enlace Bluetooth a aplicación Android. Universidad de Jaén Escuela Politécnica Superior de Jaén Departamento de Electrónica y Automática Don LUIS MIGUEL NIETO NIETO, tutor del Trabajo Fin de Grado titulado: DATALOGGER CON ENLACE BLUETOOTH A ANDROID, que presenta JUAN MIGUEL BEJARANO BUENO, autoriza su presentación para defensa y evaluación en la Escuela Politécnica Superior de Jaén. Jaén, SEPTIEMBRE de 2015 El alumno: El tutor: JUAN MIGUEL BEJARANO BUENO LUIS MIGUEL NIETO NIETO 1 Escuela Politécnica Superior de Jaén Juan Miguel Bejarano Bueno Datalogger con enlace Bluetooth a aplicación Android. RESUMEN Este Trabajo de Fin de Grado consiste en el desarrollo de dos sistemas. En primer lugar, se dispondrá de un sistema de registro de datos por eventos o datalogger. El sistema está basado en un microcontrolador Microchip y dispondrá de una interfaz de comunicaciones Bluetooth. Este dispositivo será capaz de realizar mediciones con una duración mínima configurable. En segundo lugar y de manera simultánea, se ha diseñado una aplicación Android capaz de gestionar la comunicación con el dispositivo de una manera gráfica. El sistema se ha diseñado siempre teniendo en cuenta el ahorro económico, dispondrá de una alimentación autónoma y el mantenimiento será prácticamente nulo. Se pretende así obtener un datalogger funcional, económico e intuitivo para el manejo del mismo por cualquier tipo de usuario. -

COSMIC C Cross Compiler for Motorola 68HC11 Family

COSMIC C Cross Compiler for Motorola 68HC11 Family COSMIC’s C cross compiler, cx6811 for the Motorola 68HC11 family of microcontrollers, incorporates over twenty years of innovative design and development effort. In the field since 1986 and previously sold under the Whitesmiths brand name, cx6811 is reliable, field-tested and incorporates many features to help ensure your embedded 68HC11 design meets and exceeds performance specifications. The C Compiler package for Windows includes: COSMIC integrated development environment (IDEA), optimizing C cross compiler, macro assembler, linker, librarian, object inspector, hex file generator, object format converters, debugging support utilities, run-time libraries and a compiler command driver. The PC compiler package runs under Windows 95/98/ME/NT4/2000 and XP. Complexity of a more generic compiler. You also get header Key Features file support for many of the popular 68HC11 peripherals, so Supports All 68HC11 Family Microcontrollers you can access their memory mapped objects by name either ANSI C Implementation at the C or assembly language levels. Extensions to ANSI for Embedded Systems ANSI / ISO Standard C Global and Processor-Specific Optimizations This implementation conforms with the ANSI and ISO Optimized Function Calling Standard C specifications which helps you protect your C support for Internal EEPROM software investment by aiding code portability and reliability. C support for Direct Page Data C Runtime Support C support for Code Bank Switching C runtime support consists of a subset of the standard ANSI C support for Interrupt Handlers library, and is provided in C source form with the binary Three In-Line Assembly Methods package so you are free to modify library routines to match User-defined Code/Data Program Sections your needs. -

M.Tech –Embedded System Design SEMESTER-I S.NO CODE

CURRICULUM DEPARTMENT OF ELECTRONICS AND COMMUNICATION BRANCH: M.Tech –Embedded System Design SEMESTER-I S.NO CODE SUBJECT NAME L T P C 1 PMA105 Applied Mathematics for Electronics Engineers 3 1 0 4 2 PED101 Microcontroller Based System Design 3 0 0 3 3 PED102 Embedded Systems 3 0 0 3 4 PAE102 Advanced Digital System Design 3 0 0 3 5 PED1E1 Elective-I 3 0 0 3 6 PED1L1 Embedded System Design Lab-I 0 0 4 2 TOTAL CONTACT HOURS- 20 18 SEMESTER-II 1 PED101 ASIC Design 3 0 0 3 2 PED202 Software Technology for Embedded System 3 0 0 3 3 PED203 Real Time Systems 3 0 0 3 4 PED2E2 Elective-II 3 0 0 3 5 PED2E3 Elective-III 3 0 0 3 6 PED2L2 Embedded System Design Lab -II 0 0 4 2 TOTAL CONTACT HOURS -19 17 SEMESTER-III 1. PED3E4 Elective-IV 3 0 0 3 2. PED3E5 Elective-V 3 0 0 3 3. PED3E6 Elective-VI 3 0 0 3 4. PED3P1 Project work phase-I 0 0 12 6 TOTAL CONTACT HOURS-21 15 SEMESTER-IV 1 PED4P2 Project work phase-II 0 0 24 12 TOTAL CONTACT HOURS-24 12 TOTAL CREDITS FOR THE PROGRAMME-62 LIST OF ELECTIVES 1 PED 001 Design of Embedded System 3 0 0 3 2 PED 002 Embedded Control System 3 0 0 3 3 PED 003 Computer Vision and Image Understanding 3 0 0 3 4 PED 004 Distributed Embedded Computing 3 0 0 3 5 PED 005 Design of Digital Control System 3 0 0 3 6 PED 006 Crypto Analytic Systems 3 0 0 3 7 PED 007 Intelligent Embedded Systems 3 0 0 3 8 PAE 006 Artificial Intelligence and Expert systems 3 0 0 3 9 PED102 Embedded systems 3 0 0 3 10 PED201 ASIC Design 3 0 0 3 11 PVL002 Low power VLSI Design 3 0 0 3 12 PVL003 Analog VLSI Design 3 0 0 3 13 PVL004 VLSI Signal processing -

8051 Programmer

T51prog2 MCS51 series and Atmel AVR microcontrollers ISP capable fast programmer Short description: 10692 supported devices from 149 manufacturers by 2.75 version of SW (21. Dec. 2010) small, very fast and powerful portable programmer of MCS51 series and Atmel AVR microcontrollers in-circuit serial programming (ISP) capability included program also serial EEPROMs DIL40 ZIF socket, all MCS51/AVR chips in DIL package up to 40 pins are supported without adapters connection to PC: USB port USB 2.0 full speed and USB 1.1 compatible upgradeable to SmartProg2 programmer. comfortable and easy to use control program, work with all versions of MS Windows from Windows 98 to Window 7 64-bit free SW update, download from Internet power supply, cable and software included approved by CE laboratory to meet CE requirements made in Slovakia Available accessories: Programming Adapters (Socket Converters) Diagnostic POD for ISP connector upgrade kit Xprog2 to SmartProg2 Features GENERAL T51prog2 is the next member of new generation MS Windows (from Windows 98 to Window 7 64-bit) based ELNEC specialized programmers . Programmer is capable to support all currently available microcontrollers of the MCS51 series (up to 40 pins) and the AVR microcontrollers (8-40 pins) using parallel and serial algorithms. T51prog2 has been developed in close cooperation with Atmel W&M. , therefore programmer's hardware is focused to support all current and future microcontrollers of Atmel W&M MCS51 family. T51prog2 is a small, very fast and powerful portable programmer for MCS51 series and Atmel AVR microcontrollers. T51prog also programs serial EEPROM with IIC (24Cxx), Microwire (93Cxx) and SPI (25Cxx) interface types.