Simulation Based Tuning of System Specification

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Reception of Low Frequency Time Signals

Reprinted from I-This reDort show: the Dossibilitks of clock svnchronization using time signals I 9 transmitted at low frequencies. The study was madr by obsirvins pulses Vol. 6, NO. 9, pp 13-21 emitted by HBC (75 kHr) in Switxerland and by WWVB (60 kHr) in tha United States. (September 1968), The results show that the low frequencies are preferable to the very low frequencies. Measurementi show that by carefully selecting a point on the decay curve of the pulse it is possible at distances from 100 to 1000 kilo- meters to obtain time measurements with an accuracy of +40 microseconds. A comparison of the theoretical and experimental reiulb permib the study of propagation conditions and, further, shows the drsirability of transmitting I seconds pulses with fixed envelope shape. RECEPTION OF LOW FREQUENCY TIME SIGNALS DAVID H. ANDREWS P. E., Electronics Consultant* C. CHASLAIN, J. DePRlNS University of Brussels, Brussels, Belgium 1. INTRODUCTION parisons of atomic clocks, it does not suffice for clock For several years the phases of VLF and LF carriers synchronization (epoch setting). Presently, the most of standard frequency transmitters have been monitored accurate technique requires carrying portable atomic to compare atomic clock~.~,*,3 clocks between the laboratories to be synchronized. No matter what the accuracies of the various clocks may be, The 24-hour phase stability is excellent and allows periodic synchronization must be provided. Actually frequency calibrations to be made with an accuracy ap- the observed frequency deviation of 3 x 1o-l2 between proaching 1 x 10-11. It is well known that over a 24- cesium controlled oscillators amounts to a timing error hour period diurnal effects occur due to propagation of about 100T microseconds, where T, given in years, variations. -

Time Signal Stations 1By Michael A

122 Time Signal Stations 1By Michael A. Lombardi I occasionally talk to people who can’t believe that some radio stations exist solely to transmit accurate time. While they wouldn’t poke fun at the Weather Channel or even a radio station that plays nothing but Garth Brooks records (imagine that), people often make jokes about time signal stations. They’ll ask “Doesn’t the programming get a little boring?” or “How does the announcer stay awake?” There have even been parodies of time signal stations. A recent Internet spoof of WWV contained zingers like “we’ll be back with the time on WWV in just a minute, but first, here’s another minute”. An episode of the animated Power Puff Girls joined in the fun with a skit featuring a TV announcer named Sonny Dial who does promos for upcoming time announcements -- “Welcome to the Time Channel where we give you up-to- the-minute time, twenty-four hours a day. Up next, the current time!” Of course, after the laughter dies down, we all realize the importance of keeping accurate time. We live in the era of Internet FAQs [frequently asked questions], but the most frequently asked question in the real world is still “What time is it?” You might be surprised to learn that time signal stations have been answering this question for more than 100 years, making the transmission of time one of radio’s first applications, and still one of the most important. Today, you can buy inexpensive radio controlled clocks that never need to be set, and some of us wear them on our wrists. -

Radio Navigational Aids

RADIO NAVIGATIONAL AIDS Publication No. 117 2014 Edition Prepared and published by the NATIONAL GEOSPATIAL-INTELLIGENCE AGENCY Springfield, VA © COPYRIGHT 2014 BY THE UNITED STATES GOVERNMENT NO COPYRIGHT CLAIMED UNDER TITLE 17 U.S.C. WARNING ON USE OF FLOATING AIDS TO NAVIGATION TO FIX A NAVIGATIONAL POSITION The aids to navigation depicted on charts comprise a system consisting of fixed and floating aids with varying degrees of reliability. Therefore, prudent mariners will not rely solely on any single aid to navigation, particularly a floating aid. The buoy symbol is used to indicate the approximate position of the buoy body and the sinker which secures the buoy to the seabed. The approximate position is used because of practical limitations in positioning and maintaining buoys and their sinkers in precise geographical locations. These limitations include, but are not limited to, inherent imprecisions in position fixing methods, prevailing atmospheric and sea conditions, the slope of and the material making up the seabed, the fact that buoys are moored to sinkers by varying lengths of chain, and the fact that buoy and/or sinker positions are not under continuous surveillance but are normally checked only during periodic maintenance visits which often occur more than a year apart. The position of the buoy body can be expected to shift inside and outside the charting symbol due to the forces of nature. The mariner is also cautioned that buoys are liable to be carried away, shifted, capsized, sunk, etc. Lighted buoys may be extinguished or sound signals may not function as the result of ice or other natural causes, collisions, or other accidents. -

STANDARD FREQUENCIES and TIME SIGNALS (Question ITU-R 106/7) (1992-1994-1995) Rec

Rec. ITU-R TF.768-2 1 SYSTEMS FOR DISSEMINATION AND COMPARISON RECOMMENDATION ITU-R TF.768-2 STANDARD FREQUENCIES AND TIME SIGNALS (Question ITU-R 106/7) (1992-1994-1995) Rec. ITU-R TF.768-2 The ITU Radiocommunication Assembly, considering a) the continuing need in all parts of the world for readily available standard frequency and time reference signals that are internationally coordinated; b) the advantages offered by radio broadcasts of standard time and frequency signals in terms of wide coverage, ease and reliability of reception, achievable level of accuracy as received, and the wide availability of relatively inexpensive receiving equipment; c) that Article 33 of the Radio Regulations (RR) is considering the coordination of the establishment and operation of services of standard-frequency and time-signal dissemination on a worldwide basis; d) that a number of stations are now regularly emitting standard frequencies and time signals in the bands allocated by this Conference and that additional stations provide similar services using other frequency bands; e) that these services operate in accordance with Recommendation ITU-R TF.460 which establishes the internationally coordinated UTC time system; f) that other broadcasts exist which, although designed primarily for other functions such as navigation or communications, emit highly stabilized carrier frequencies and/or precise time signals that can be very useful in time and frequency applications, recommends 1 that, for applications requiring stable and accurate time and frequency reference signals that are traceable to the internationally coordinated UTC system, serious consideration be given to the use of one or more of the broadcast services listed and described in Annex 1; 2 that administrations responsible for the various broadcast services included in Annex 2 make every effort to update the information given whenever changes occur. -

Time and Frequency Users' Manual

,>'.)*• r>rJfl HKra mitt* >\ « i If I * I IT I . Ip I * .aference nbs Publi- cations / % ^m \ NBS TECHNICAL NOTE 695 U.S. DEPARTMENT OF COMMERCE/National Bureau of Standards Time and Frequency Users' Manual 100 .U5753 No. 695 1977 NATIONAL BUREAU OF STANDARDS 1 The National Bureau of Standards was established by an act of Congress March 3, 1901. The Bureau's overall goal is to strengthen and advance the Nation's science and technology and facilitate their effective application for public benefit To this end, the Bureau conducts research and provides: (1) a basis for the Nation's physical measurement system, (2) scientific and technological services for industry and government, a technical (3) basis for equity in trade, and (4) technical services to pro- mote public safety. The Bureau consists of the Institute for Basic Standards, the Institute for Materials Research the Institute for Applied Technology, the Institute for Computer Sciences and Technology, the Office for Information Programs, and the Office of Experimental Technology Incentives Program. THE INSTITUTE FOR BASIC STANDARDS provides the central basis within the United States of a complete and consist- ent system of physical measurement; coordinates that system with measurement systems of other nations; and furnishes essen- tial services leading to accurate and uniform physical measurements throughout the Nation's scientific community, industry, and commerce. The Institute consists of the Office of Measurement Services, and the following center and divisions: Applied Mathematics -

Atomix Atomic Clock 00562 Instructions

Atomix Atomic Clock Model 00562 About the Atomic Clock The National Institute of Standard and Technology (NIST) in Fort Collins, Colorado broadcasts the time signal (WWVB at 60 kHz AM radio signal) with an accuracy of 1 second per every 3,000 years. The signal is able to cover a distance of up to 2,000 miles from the source. Like a typical AM radio, your atomic clock will not be able to receive the WWVB signal in places surrounded by heavy concrete or metal panels. The reception of the time signal is also greatly affected by electrical or electronic interference. To get the best performance from the atomic clock, install the clock nearer to a window facing west. Battery Installation and Set Up Remove the battery cover and insert 2 “AA” alkaline batteries according to the direction shown inside the battery compartment. Once the batteries are installed the display will show all segments of the LCD display for 3 seconds and will beep once. Then the display will show 12:00pm Jan 1, 2000 together with room temperature. The Time Zone is defaulted at PST – Pacific Standard Time. Select the correct Timer Zone 1. Press the ZONE / DST button to select PST, MST, CST or EST. 2. Once a time zone is selected, your Atomix clock will start searching for the time signal. 3. While your Atomix clock is seeking the signal, the signal strength icon will change gradually indicating the search is continuing. 4. If the signal is available, your Atomix clock will display the local time in about 3-5 minutes. -

Nbs Technical Note 674 National Bureau of Standards

NBS TECHNICAL NOTE 674 NATIONAL BUREAU OF STANDARDS The National Bureau of Standards' was established by an act of Congress March 3, ,1901. The Bureau's overall goal is to strengthen and advance the Nation's science and technology and facilitate their effective application for public benefit. To this end, the Bureau conducts research and provides: (1) a basis for the Nation's physical measurement system, (2) scientific and technological services for industry and government, (3) a technical basis for equity in trade, and (4) technical services to promote public safety. The Bureau consists of the Institute for Basic Standards, the Institute for Materials Research, the Institute for Applied Technology, the Institute for Computer Sciences and Technology, and the Office for Information Programs. THE INSTITUTE FOR BASIC STANDARDS provides the central basis within the United States of a complete and consistent system of physical measurement; coordinates that system with measurement systems of other nations; and furnishes essential services leading to accurate and uniform physical measurements throughout the Nation's scientific community, industry, and commerce. The Institute consists of the Office of Measurement Services, the Office of Radiation Measurement and the following Center and divisions: Applied Mathematics - Electricity - Mechanics - Heat - Optical Physics - Center for Radiation Research: Nuclear Sciences; Applied Radiation - Laboratory Astrophysics * - Cryogenics ' - Electromagnetics - Time and Frequency *. THE INSTITUTE FOR MATERIALS RESEARCH conducts materials research leading to improved methods of measurement, standards, and data on the properties of well-characterized materials needed by industry, commerce, educational institutions, and Government; provides advisory and research services to other Government agencies; and develops, produces, and distributes standard reference materials. -

Japan Standard Time Service Group

Space-Time Standards Laboratory Japan Standard Time 6HUYLFHGroup National Institute of Information and Communications Technology -DSDQ6WDQGDUG7LPH6HUYLFH*URXSʊ*HQHUDWLRQ&RPSDULVRQDQG 'LVVHPLQDWLRQRI-DSDQ6WDQGDUG7LPHDQG)UHTXHQF\6WDQGDUGV National Institute of Information and Communications Technology 7KH1DWLRQDO,QVWLWXWHRI,QIRUPDWLRQDQG&RPPXQLFDWLRQV7HFKQRORJ\ 1,&7 LVUHVSRQVLEOHIRUWKHLPSRUWDQW WDVNV RI *HQHUDWLRQ &RPSDULVRQ DQG 'LVVHPLQDWLRQ RI -DSDQ 6WDQGDUG 7LPH DQG )UHTXHQF\ 6WDQGDUGV ZKLFKKDYHDGLUHFWLPSDFWRQSHRSOH¶VOLYHV,QWKLVEURFKXUHZHILUVWH[SODLQKRZ,QWHUQDWLRQDO$WRPLF7LPH DQG &RRUGLQDWHG 8QLYHUVDO 7LPH DUH FDOFXODWHG :H WKHQ ORRN DW KRZ WKH VWDQGDUG WLPH DOO RYHU WKH ZRUOG LQFOXGLQJ -DSDQ 6WDQGDUG 7LPH LV JHQHUDWHG EDVHG RQ WKHP )LQDOO\ ZH LQWURGXFH WKUHH PDMRU IXQFWLRQV RI WKH-DSDQ6WDQGDUG7LPH6HUYLFH*URXS*HQHUDWLRQ&RPSDULVRQDQG'LVVHPLQDWLRQRI-DSDQ6WDQGDUG7LPH 6OJWFSTBM 5JNF 65 BU PO +BOVBSZ BOE UIF UXP IBWF TJODF ESJGUFE BQBSU 5"* JT EFDJEFE CZ DBMDVMBUJOH B XFJHIUFEBWFSBHFUJNFPGBUPNJDDMPDLTBSPVOEUIFXPSME PPSEJOBUFE6OJWFSTBM5JNFBOE-FBQ4FDPOE$ڦ "EKVTUNFOU 8IBUJTUIF5JNF 0VSEBJMZMJWFTBSFHPWFSOFECZUIFBQQBSFOUNPUJPOPGUIF4VO 4JODF UIF UJNF TDBMF VTFE JO NFBTVSJOH UJNF JT BUPNJD UJNF UIFSFJTBOFFEGPSBOBUPNJDUJNFUIBUJTDMPTFUP6OJWFSTBM5JNF 65 5IJTBUPNJDUJNFJTDBMMFE$PPSEJOBUFE6OJWFSTBM5JNF 65$ "T UIF BOHVMBS WFMPDJUZ PG UIF &BSUI JT BGGFDUFE CZ OBUVSBM QIFOPNFOBTVDIBTUJEBMGSJDUJPO UIFNBOUMF BOEUIFBUNPT B UJNF EJGGFSFODF CFUXFFO 65 BOE 65$ JT GMVDUVBUFE FGJOJUJPOPGB4FDPOE QIFSF% ڦ 5IFSFGPSF UP LFFQ UIF UJNF EJGGFSFODF CFUXFFO 65$ -

Reception of Radio Controlled Signal Signal

Suitable mode: C8458B-PD15164M(DCF/MSF/WWVB/JJY) Size: A4 2015.4.20 10 9 1 9 1 8 8 2 7 2 7 RADIO CONTROLLED CLOCK 3 6 3 6 WITH TEMPERATURE AND HUMIDITY Model: C8458B 4545 USER MANUAL WWVB version JJY version Suitable mode: C8458B-PD15164M(DCF/MSF/WWVB/JJY) Size: A4 2015.4.20 2 Alarm time mode 1 1. Alarm time 3 2. Alarm icon/Alarm on 3. Alarm mode indicator 10 9 1 9 1 8 8 2 7 2 7 RADIO CONTROLLED CLOCK 3 6 3 6 WITH TEMPERATURE AND HUMIDITY GETTING STARTED Model: C8458B 45Ɣ Remove the battery door. 45 Ɣ ,nsert 4 new AA size batteries according to the “+/-” polarity mark on the USER MANUAL battery compartment. WWVB version JJY version Thank you for purchasing this delicate radio clock with temperature and Ɣ Replace the battery door. humidity. Utmost care has gone into the design and manufacture of the clock. Ɣ 2nce the batteries are inserted, full segment of the LCD will be shown before This manual is used for DCF/MSF/WWVB/JJY versions, but the LCD display 2 entering the radio controlled time reception1 mode. and temperature use DCF/MSF version for reference. Please read the ƔAlarm The timeRC clock mode will automatically start scanning for the radio controlled time 3 instructions carefully according to the version you purchased and keep the 1. signalAlarm intime 8 seconds. manual well for future reference. 2. Alarm icon/Alarm on 3. Alarm mode indicator NOTE: PRODUCT OVERVIEW ,f no display appears on the LCD after inserting the batteries, press the [ RESET ] button by using a metal wire. -

Radio Controlled Analog Clock Quick Set up Instructions Nothing Is More

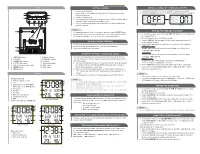

La Crosse Technology Radio Controlled Analog Clock OWNER’S MANUAL Quick set up instructions Welcome to the world of radio controlled timekeeping technology. We hope you will enjoy the convenience of never having to set your clock again and the confidence of knowing exactly what time it is. • Insert 1 fresh AA, LR6 1.5 volt ALKALINE battery • Press button to select a time zone. THAT’S IT! During the night your clock will automatically set itself. For a better understanding of how and why your clock works please continue reading. Nothing is more precisely measured than time! And nothing keeps track of time more precisely and trouble free than La Crosse Technology radio controlled clocks. Since the beginning of time, man has been fascinated with the measurement of time and has devised more accurate machines to trap and measure time. Today, time is precisely measured in the United States by the most accurate clock in North America, the Atomic Clock of the US National Institute of Standards and Technology, Time and Frequency Division in Boulder, Colorado. A team of atomic physicists continually measures every second of every day to an accuracy of ten billionths of a second per day. These physicists have created an international standard, measuring a second as 9,192,631,770 vibrations of a Cesium 133 atom in a vacuum. This atomic clock regulates the WWVB radio transmitter located in Fort Collins, Colorado, where the exact time signal is continuously broadcast throughout the United States at 60 kHz to take advantage of stable longwave radio paths found in that frequency range. -

Geodetic Connexion Between France and North Africa by Simultaneous Sighting on the Echo I Artificial Satellite

GEODETIC CONNEXION BETWEEN FRANCE AND NORTH AFRICA BY SIMULTANEOUS SIGHTING ON THE ECHO I ARTIFICIAL SATELLITE by The F rench N ational Geographical Institute Report submitted by the French Government to the Second United Nations Regional Cartographic Conference for Africa,Tunis (Tunisia) Í2-14- September 1966 h — GENERAL PRINCIPLES OF SATELLITE TRIANGULATION The basic principle is very simple : a luminous object is seen against a different star background according to the observer's position on the earth’s surface. It can be seen that a photograph of this luminous object and the surrounding stars will give information which permits fixing the position of points on the earth’s surface, on the assumption that the positions of other observation points are known. Let us clarify this idea : the solid earth, assumed to be indéformable and to which we shall attach a trihedral TXYZ, has a known directional movement relative to the stars in function of time, this movement being given by the astronomy of star positions. Fixing the time means immobil izing the position of the trihedral in the stellar field; each star then constitutes an absolute direction in relation to the trihedral TXYZ, such direction being given in the star almanac. In the same way we must “ immobilize ’’ the luminous object, which in practice requires simultaneous or nearly simultaneous observations from the different points on the earth’s surface which are to be connected. If the luminous object emits flashes then simultaneity is automatic ally ensured. If it is continuously luminous, then “ artificial flashes ’’ have to be arranged by using, at the various observation points, rotating shutters which can be synchronized. -

Time and Frequency Transmission Facilities

Time and Frequency Transmission Facilities ▲Ohtakadoya-yama LF Standard Time and Frequency Transmission Station Disseminating accurate Japan Standard Time (JST)! ● Time synchronization of radio clocks ●Time standard for broadcasting and telephone time signal services Providing highly precise frequency standards! ● Frequency standard for measuring instruments ● Frequency synchronization of radio instruments ▲Hagane-yama LF Standard Time and Frequency Transmission Station National Institute of Information and Communications Technology,Applied Electromagnetic Research Institute. Space-Time Standards Laboratory Japan Standard Time Group 長波帯電波施設(英文).indd 1 1 17/07/25 16:58 of received signals may be reduced by factors such as Low-Frequency conditions in the ionosphere. Such effects are particularly enhanced in the HF region, causing the frequency precision of the received wave to deteriorate to nearly 1 × Standard Time and 10–8 (i.e., the frequency differs from the standard frequency by 1/100,000,000). Therefore, low frequencies, which are Frequency not susceptible to ionospheric conditions, are used for standard transmissions, allowing received signals to be Transmission used as more precise frequency standards. The precision obtained in LF transmissions, calculated as a 24-hour average of frequency comparison, is 1 × 10–11 (i.e., the The National Institute of Information and Communications frequency differs from the standard frequency by Technology (NICT) determines and maintains the time and 1/100,000,000,000). The Ohtakadoya-yama and Hagane- frequency standard and Japan Standard Time (JST) in yama LF Standard Time and Frequency Transmission Japan as the sole organization responsible for the national Stations are described on the final page. Note that frequency standard.