Taking a Proactive Approach to Effective Supply Chain Management

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Outline ECE473 Computer Architecture and Organization • Technology Trends • Introduction to Computer Technology Trends Architecture

Outline ECE473 Computer Architecture and Organization • Technology Trends • Introduction to Computer Technology Trends Architecture Lecturer: Prof. Yifeng Zhu Fall, 2009 Portions of these slides are derived from: ECE473 Lec 1.1 ECE473 Lec 1.2 Dave Patterson © UCB Birth of the Revolution -- What If Your Salary? The Intel 4004 • Parameters – $16 base First Microprocessor in 1971 – 59% growth/year – 40 years • Intel 4004 • 2300 transistors • Initially $16 Æ buy book • Barely a processor • 3rd year’s $64 Æ buy computer game • Could access 300 bytes • 16th year’s $27 ,000 Æ buy cacar of memory • 22nd year’s $430,000 Æ buy house th @intel • 40 year’s > billion dollars Æ buy a lot Introduced November 15, 1971 You have to find fundamental new ways to spend money! 108 KHz, 50 KIPs, 2300 10μ transistors ECE473 Lec 1.3 ECE473 Lec 1.4 2002 - Intel Itanium 2 Processor for Servers 2002 – Pentium® 4 Processor • 64-bit processors Branch Unit Floating Point Unit • .18μm bulk, 6 layer Al process IA32 Pipeline Control November 14, 2002 L1I • 8 stage, fully stalled in- cache ALAT Integer Multi- Int order pipeline L1D Medi Datapath RF @3.06 GHz, 533 MT/s bus cache a • Symmetric six integer- CLK unit issue design HPW DTLB 1099 SPECint_base2000* • IA32 execution engine 1077 SPECfp_base2000* integrated 21.6 mm L2D Array and Control L3 Tag • 3 levels of cache on-die totaling 3.3MB 55 Million 130 nm process • 221 Million transistors Bus Logic • 130W @1GHz, 1.5V • 421 mm2 die @intel • 142 mm2 CPU core L3 Cache ECE473 Lec 1.5 ECE473 19.5mm Lec 1.6 Source: http://www.specbench.org/cpu2000/results/ @intel 2006 - Intel Core Duo Processors for Desktop 2008 - Intel Core i7 64-bit x86-64 PERFORMANCE • Successor to the Intel Core 2 family 40% • Max CPU clock: 2.66 GHz to 3.33 GHz • Cores :4(: 4 (physical)8(), 8 (logical) • 45 nm CMOS process • Adding GPU into the processor POWER 40% …relative to Intel® Pentium® D 960 When compared to the Intel® Pentium® D processor 960. -

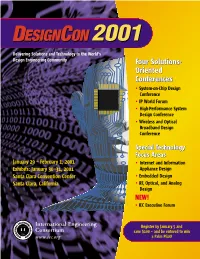

Oriented Conferences Four Solutions

Delivering Solutions and Technology to the World’s Design Engineering Community Four Solutions- Oriented Conferences • System-on-Chip Design Conference • IP World Forum • High-Performance System Design Conference • Wireless and Optical Broadband Design Conference Special Technology Focus Areas January 29 – February 1, 2001 • Internet and Information Exhibits: January 30–31, 2001 Appliance Design Santa Clara Convention Center • Embedded Design Santa Clara, California • RF, Optical, and Analog Design NEW! • IEC Executive Forum International Engineering Register by January 5 and Consortium save $100 – and be entered to win www.iec.org a Palm Pilot! Practical Design Solutions Practical design-engineering solutions presented by practicing engineers—The DesignCon reputation of excellence has been built largely by the practical nature of its sessions. Design engineers hand selected by our team of professionals provide you with the best electronic design and silicon-solutions information available in the industry. DesignCon provides attendees with DesignCon has an established reputation for the high design solutions from peers and professionals. quality of its papers and its expert-level speakers from Silicon Valley and around the world. Each year more than 100 industry pioneers bring to light the design-engineering solutions that are on the leading edge of technology. This elite group of design engineers presents unique case studies, technology innovations, practical techniques, design tips, and application overviews. Who Should Attend Any professionals who need to stay on top of current information regarding design-engineering theories, The most complete educational experience techniques, and application strategies should attend this in the industry conference. DesignCon attracts engineers and allied The four conference options of DesignCon 2001 provide a professionals from all levels and disciplines. -

The Advantages of FRAM-Based Smart Ics for Next Generation Government Electronic Ids

The Advantages of FRAM-Based Smart ICs for Next Generation Government Electronic IDs By Joseph Pearson and Dr. Ted Moise Texas Instruments, Inc. September 27, 2007 Executive Summary Electronic versions of passports and other government-issued identification documents use an Integrated Circuit (IC) or chip to establish a digital link between the holder and personal biometric information, such as a digitized photo, fingerprint or iris image. Designed to enhance border, physical and IT security, electronic chips ensure that the person holding a passport or government document is the one to whom it was legitimately issued. The next generation ICs will employ an advanced embedded memory technology, called FRAM (Ferroelectric Random Access Memory), which considerably improves the speed and reliability of future smart, secure e-passports and government ID documents. More than 50 countries have electronic passport (e-passport) programs, and many countries are also putting in place more secure forms of electronic citizen, visitor and government employee identification. As the volume of document issuance increases and new security threats occur, there is an increased need for industry-standard, next-generation contactless smart IC solutions that securely store, process and communicate data. These new smart ICs will have increased writing speeds to produce and process documents faster and more efficiently, as well as enhanced memory for future security requirements. When FRAM is manufactured at the 130 nanometer semiconductor process node, and embedded in a smart IC, it surpasses the limitations of current Electrically Erasable Programmable Read-Only Memory (EEPROM) and other memory technologies used in government ID applications. The imminent introduction of this innovative memory technology for smart ICs signals a shift in performance in smart card applications deployed in government electronic ID documents. -

Nano-Cmos Scaling Problems and Implications

CHAPTER 1 NANO-CMOS SCALING PROBLEMS AND IMPLICATIONS 1.1 DESIGN METHODOLOGY IN THE NANO-CMOS ERA As process technology scales beyond 100-nm feature sizes, for functional and high-yielding silicon the traditional design approach needs to be modified to cope with the increased process variation, interconnect processing difficulties, and other newly exacerbated physical effects. The scaling of gate oxide (Figure 1.1) in the nano-CMOS regime results in a significant increase in gate direct tunnel- ing current. Subthreshold leakage and gate direct tunneling current (Figure 1.2) are no longer second-order effects [1,15]. The effect of gate-induced drain leak- age (GIDL) will be felt in designs, such as DRAM (Chapter 7) and low-power SRAM (Chapter 9), where the gate voltage is driven negative with respect to the source [15]. If these effects are not taken care of, the result will be a nonfunctional SRAM, DRAM, or any other circuit that uses this technique to reduce subthresh- old leakage. In some cases even wide muxes and flip-flops may be affected. Subthreshold leakage and gate current are not the only issues that we have to deal with at a functional level, but also the power management of chips for high-performance circuits such as microprocessors, digital signal processors, and graphics processing units. Power management is also a challenge in mobile applications. Furthermore, optical lithography will be stretched to the limit even when en- hanced resolution extension technologies (RETs) are employed. These techniques Nano-CMOS Circuit and Physical Design, by Ban P. Wong, Anurag Mittal, Yu Cao, and Greg Starr ISBN 0-471-46610-7 Copyright © 2005 John Wiley & Sons, Inc. -

3D Massively Parallel Processor with Stacked Memory)

112 IEEE TRANSACTIONS ON COMPUTERS, VOL. 64, NO. 1, JANUARY 2015 Design and Analysis of 3D-MAPS (3D Massively Parallel Processor with Stacked Memory) Dae Hyun Kim, Krit Athikulwongse, Michael B. Healy, Mohammad M. Hossain, Moongon Jung, Ilya Khorosh, Gokul Kumar, Young-Joon Lee, Dean L. Lewis, Tzu-Wei Lin, Chang Liu, Shreepad Panth, Mohit Pathak, Minzhen Ren, Guanhao Shen, Taigon Song, Dong Hyuk Woo, Xin Zhao, Joungho Kim, Ho Choi, Gabriel H. Loh, Hsien-Hsin S. Lee, and Sung Kyu Lim Abstract—This paper describes the architecture, design, analysis, and simulation and measurement results of the 3D-MAPS (3D massively parallel processor with stacked memory) chip built with a 1.5 V, 130 nm process technology and a two-tier 3D stacking technology using 1.2 μ -diameter, 6 μ -height through-silicon vias (TSVs) and μ -diameter face-to-face bond pads. 3D-MAPS consists of a core tier containing 64 cores and a memory tier containing 64 memory blocks. Each core communicates with its dedicated 4KB SRAM block using face-to-face bond pads, which provide negligible data transfer delay between the core and the memory tiers. The maximum operating frequency is 277 MHz and the maximum memory bandwidth is 70.9 GB/s at 277 MHz. The peak measured memory bandwidth usage is 63.8 GB/s and the peak measured power is approximately 4 W based on eight parallel benchmarks. Index Terms—3D Multiprocessor-memory stacked systems, 3D integrated circuits, Computer-aided design, RTL implementation and simulation 1INTRODUCTION HREE-DIMENSIONAL integrated circuits (3D ICs) are ex- circuit components built with different technologies can be Tpected to provide numerous benefits. -

Samsung Electronics Co., Ltd. and Its Subsidiaries NOTES to INTERIM

Samsung Electronics Co., Ltd. and its Subsidiaries NOTES TO INTERIM CONSOLIDATED FINANCIAL STATEMENTS 1. General Information 1.1 Company Overview Samsung Electronics Co., Ltd. (“SEC”) was incorporated under the laws of the Republic of Korea in 1969 and listed its shares on the Korea Stock Exchange in 1975. SEC and its subsidiaries (collectively referred to as the “Company”) operate four business divisions: Consumer Electronics (“CE”), Information technology & Mobile communications (“IM”), Device Solutions (“DS”) and Harman. The CE division includes digital TVs, monitors, air conditioners and refrigerators and the IM division includes mobile phones, communication systems, and computers. The DS division includes products such as Memory, Foundry and System LSI in the semiconductor business (“Semiconductor”), and LCD and OLED panels in the display business (“DP”). The Harman division includes connected car systems, audio and visual products, enterprise automation solutions and connected services. The Company is domiciled in the Republic of Korea and the address of its registered office is Suwon, the Republic of Korea. These interim consolidated financial statements have been prepared in accordance with Korean International Financial Reporting Standards (“Korean IFRS”) 1110, Consolidated Financial Statements. SEC, as the controlling company, consolidates its 256 subsidiaries including Samsung Display and Samsung Electronics America. The Company also applies the equity method of accounting for its 41 associates, including Samsung Electro-Mechanics. -

Organising Committees

DATE 2005 Executive Committee GENERAL CHAIR PROGRAMME CHAIR Nobert Wehn Luca Benini Kaiserslautern U, DE DEIS – Bologna U, IT VICE CHAIR & PAST PROG. CHAIR VICE PROGRAMME CHAIR Georges Gielen Donatella Sciuto KU Leuven, BE Politecnico di Milano, IT FINANCE CHAIR PAST GENERAL CHAIR Rudy Lauwereins Joan Figueras IMEC, Leuven, BE UP Catalunya, Barcelona, ES DESIGNERS’ FORUM DESIGNERS’ FORUM Menno Lindwer Christoph Heer Philips, Eindhoven, NL Infineon, Munich, DE SPECIAL SESSIONS & DATE REP AT DAC FRIDAY WORKSHOPS Ahmed Jerraya Bashir Al-Hashimi TIMA, Grenoble, FR Southampton U, UK INTERACTIVE PRESENTATIONS ELECTRONIC REVIEW Eugenio Villar Wolfgang Mueller Cantabria U, ES Paderborn U, DE WEB MASTER AUDIO VISUAL Udo Kebschull Jaume Segura Heidelberg U, DE Illes Baleares U, ES TUTORIALS & MASTER COURSES FRINGE MEETINGS Enrico Macii Michel Renovell Politecnico di Torino, IT LIRMM, Montpellier, FR AUTOMOTIVE DAY BIOCHIPS DAY Juergen Bortolazzi Christian Paulus DaimlerChrysler, DE Infineon, Munich, DE PROCEEDINGS EXHIBITION PROGRAMME Christophe Bobda Juergen Haase Erlangen U, DE edacentrum, Hannover, DE UNIVERSITY BOOTH UNIVERSITY BOOTH & ICCAD Volker Schoeber REPRESENTATIVE edacentrum, Hannover, DE Wolfgang Rosenstiel Tuebingen U/FZI, DE AWARDS & DATE REP. AT ASPDAC PCB SYMPOSIUM Peter Marwedel Rainer Asfalg Dortmund U, DE Mentor Graphics, DE TRAVEL GRANTS COMMUNICATIONS Marta Rencz Bernard Courtois TU Budapest, HU TIMA, Grenoble, FR LOCAL ARRANGEMENTS PRESS LIASON Volker Dueppe Fred Santamaria Siemens, DE Infotest, Paris, FR ESF CHAIR & EDAA -

Short Form Catalogue 2011

Short form catalogue 2011 TM Always On WiFi Short description Nanoradio AB has developed the smallest and most power NRG831 - 802.11b/g/n single chip System in Package efficient Wi-Fi solutions in the world, for battery operated mobile (SiP) for Mobile Devices devices like: The NRG831 is 802.11b/g/n compliant Wireless LAN System-in- Mobile phones, VoIP phones, tablets (MID), multimedia devices Package (SiP) solution. This ultra-low power circuit is optimized for (Mobile gaming terminals, portable multimedia players, digital use in mobile phones and supports full coexistence with Bluetooth cameras, positioning devices and E-book readers) and headsets. chips. Wi-Fi Certifications including 802.11b/g/n, WPA. WPA2, Nanoradio AB is now broadening its offerings by developing WMM. UMA support. solutions including further connectivity features, e.g. Bluetooth. NRG800 - Combo WLAN 802.11b/g/Bluetooth single chip The Nanoradio solutions are offered as Wi-Fi chipset or as System-in-Package (SiP) for mobile devices. complete modules from our global module partners. The NRG800 is a complete Wireless LAN/ Bluetooth© Combo System- in-Package (SiP) Solution for Mobile devices. The NRG800 delivers a PRODUCTS complete and fully tested implementation of 802.11b/g and Bluetooth NRX600 - 802.11 b/g true one chip (COB) functionality. Best WiFi/BT coexistence on the market. High performance 802.11 b/g true one chip for direct PCB NRG850 - Combo WLAN 802.11b/g/n/Bluetooth single mounting, designed to handle the 802.11 b/g standards. This ultra chip System-in-Package (SiP) for mobile devices. low power chip is optimized for use in battery operated The NRG850 is a complete Wireless LAN/Bluetooth© Combo mobile devices, due to one chip power System-in-Package (SiP) Solution for Mobile devices. -

Interim Consolidated Financial Statements of Samsung Electronics Co., Ltd

INTERIM CONSOLIDATED FINANCIAL STATEMENTS OF SAMSUNG ELECTRONICS CO., LTD. AND ITS SUBSIDIARIES INDEX TO FINANCIAL STATEMENTS Page Independent Auditors’ Review Report 1-2 Inteim Consolidated Statements of Financial Position 3-5 Inteim Consolidated Statements of Profit or Loss 6 Inteim Consolidated Statements of Comprehensive Income 7 Inteim Consolidated Statements of Changes in Equity 8-11 Inteim Consolidated Statements of Cash Flows 12-13 Notes to the Inteim Consolidated Financial Statements 14 Deloitte Anjin LLC 9F., One IFC, 10, Gukjegeumyung-ro, Youngdeungpo-gu, Seoul 07326, Korea Tel: +82 (2) 6676 1000 Fax: +82 (2) 6674 2114 www.deloitteanjin.co.kr Independent Auditors’ Review Report [English Translation of Independent Auditors’ Report Originally Issued in Korean on November 13th, 2020] To the Shareholders and the Board of Directors of Samsung Electronics Co., Ltd.: Reviewed Financial Statements We have reviewed the accompanying interim consolidated financial statements of Samsung Electronics Co., Ltd. and its subsidiaries. The interim consolidated financial statements consist of the consolidated statement of financial position as of September 30, 2020, and the related consolidated statements of profit or loss and comprehensive income for the three-month and the nine-month period ended September 30, 2020, changes in equity and cash flows for the nine-month period ended September 30, 2020, all expressed in Korean won, and a summary of significant accounting policies and other explanatory information. Management’s Responsibility for the Consolidated Financial Statements Management is responsible for the preparation and fair presentation of these interim consolidated financial statements in accordance with Korean International Financial Reporting Standards (“K-IFRS”) No. 1034 Interim Financial Reporting, and for such internal control as management determines is necessary to enable the preparation of interim consolidated financial statements that are free from material misstatement, whether due to fraud or error. -

Exhibition Report

Exhibition Report Japan Electronics and Information Technology Industries Association (JEITA) Contents Exhibition Outline 1 Exhibition Configuration 2 1. Scope of Exhibits 2 2. Conference 2 3. Number of Exhibitors and Booths 2 4. Suite Exhibits 2 5. Exhibitors 3 Conference Activities 4 1. Exhibitor Seminars 4 2. Keynote Speech 4 3. Special Event Stage 4 4. The 13th FPGA/PLD Design Conference 4 5. FPGA/PLD Design Conference User’s Presentations 4 6. IP(Intellectual Property) Flea Market in EDSFair 4 7. System Design Forum 2006 Conference 4 Other Events and Special Projects 5 1. Opening Ceremony 5 2. University Plaza 5 3. Venture Conpany Pavilion 5 4. EDAC Reception 5 5. Press 5 Number of Visitors 6 Results of Visitor Questionnaire 6-7 Exhibition Outline Name . Electronic Design and Solution Fair 2006 (EDSFair2006) Duration . Thursday, January 26 and Friday, January 27, 2006 (2 days) 10:00 a.m. to 6:00 p.m. Location . Pacifico Yokohama (Halls C-D hall and Annex Hall) 1-1-1 Minato Mirai, Nishi-ku, Yokohama 220-0012, Japan Admission. Exhibition: Free (registration required at show entrance) Conference: Fees charged for some sessions Sponsorship . Japan Electronics and Information Technology Industries Association (JEITA) Cooperation . Electronic Design Automation Consortium (EDAC) Support . Ministry of the Economy, Trade and Industry, Japan (METI) Embassy of the United States of America in Japan Distributors Association of Foreign Semiconductors (DAFS) City of Yokohama Assistance . Institute of Electronics, Information and Communication Engineers (IEICE) Information Processing Society of Japan (IPSJ) Japan Printed Circuit Association (JPCA) Spacial Assistance. Hewlett-Packard Japan, Ltd. Sun Microsystems K.K Management . -

Nanoradio at a Glance

Nanoradio at a glance 1 © Nanoradio 2010 Confidential Nanoradio - Geographic Reach Headquarters: Kista, Sweden Sales Office in Lund NA: Agent Korea: Seoul China: Shanghai Japan: Tokyo Patras, Greece Taiwan: Taipei Development office Sales & Customer support office 2 © Nanoradio 2010 Confidential Nanoradio - Major Progress During the Last 12 Months 15 major mobile phone manufactures have selected Nanoradio, and growing 5 Global TOP10 mobile players, including Samsung, selected the Nanoradio Solution #1 Japanese vendor Sharp leading ODM’s and OEM’s in China and Taiwan Nanoradio also selected for MIDs VoIP phones Wi-Fi headsets DSC Photo frames Volumes increasing fast 350% 2008->2009 350% 2009->2010 Leading wafer and back-end partners Ported on major operating systems and platforms, increasing the addressable market to 70% 3 © Nanoradio 2010 Confidential Nanoradio - Wi-Fi Design Wins Samsung Haier P250 (2008) Q1 (2010) P270 (2008) N8 (2010) GT-M5650 (2010) K-Touch GT-M5650u (2010) W606 (2010) GT-B7722 (2010) Coolpad GT-B7722u (2010) W711(2010) GT-B7732 (2010) Huawei GT-B7722i (2011) T8301(2011) W6370 (VoIP phone) (2010) Acer Sharp beTouch E120 (2010) 940SH (2009) beTouch E130 (2010) 941SH (2009) 943SH (2010) 944SH (2010) 945SH (2010) 945SH-G (2010) 002SH (2010) 004SH (2011) 4 © Nanoradio 2010 Confidential Nanoradio - Other Applications Selected by World’s largest Camera ODM for Wi-Fi products Major SIM card Top headset player selected brand, launching NRX600 for SIM + World’s first Wi-Fi Wi-Fi cards headset China’s largest Close cooperation SD-card player with a leading selected NRX600 video chip for Flash + Wi-Fi provider cards WiFi partner by China’s largest application processor suppliers. -

28Th IEEE VLSI Test Symposium (VTS 2010) Santa Cruz, CA, April 19-21, 2010

28th IEEE VLSI Test Symposium (VTS 2010) Santa Cruz, CA, April 19-21, 2010 Preliminary Program (as of 3/25/10) Monday, 4/19/10 Plenary Session (9:00 – 11:00) Break (11:00 – 11:15) Sessions 1 (11:15 – 12:15) Session 1A: Delay & Performance Test 1 Moderator: M. Batek - Broadcom Fast Path Selection for Testing of Small Delay Defects Considering Path Correlations Z. He, T. Lv - Institute of Computing Technology, H. Li, X. Li - Chinese Academy of Sciences Identification of Critical Primitive Path Delay Faults without any Path Enumeration K. Christou, M. Michael, S. Neophytou - University of Cyprus Path Clustering for Adaptive Test T. Uezono, T. Takahashi - Tokyo Institute of Technology, M. Shintani , K. Hatayama - Semiconductor Technology Academic Research Center, K. Masu - Tokyo Institute of Technology, H. Ochi, T. Sato - Kyoto University Session 1B: Memory Test & Repair Moderator: P. Prinetto - Politecnico di Torino Automatic Generation of Memory Built-In Self-Repair Circuits in SOCs for Minimizing Test Time and Area Cost T. Tseng, C. Hou, J. Li - National Central University Bit Line Coupling Memory Tests for Single Cell Fails in SRAMs S. Irobi, Z. Al-ars, S. Hamdioui - Delft University of Technology Reducing Test Time and Area Overhead of an Embedded Memory Array Built-In Repair Analyzer with Optimal Repair Rate J. Chung, J. Park - The University of Texas at Austin, E. Byun, C. Woo - Samsung Electronics, J. Abraham - The University of Texas at Austin IP Session 1C: Innovative Practices in RF Test Organizer: R. Parekhji - Texas Instruments Moderator: TBA Test Time Reduction Using Parallel RF Test Techniques R.