D-Band Frequency Tripler Module Using Anti-Parallel Diode Pair and Waveguide Transitions

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Electronic Spectroscopy of Free Base Porphyrins and Metalloporphyrins

Absorption and Fluorescence Spectroscopy of Tetraphenylporphyrin§ and Metallo-Tetraphenylporphyrin Introduction The word porphyrin is derived from the Greek porphura meaning purple, and all porphyrins are intensely coloured1. Porphyrins comprise an important class of molecules that serve nature in a variety of ways. The Metalloporphyrin ring is found in a variety of important biological system where it is the active component of the system or in some ways intimately connected with the activity of the system. Many of these porphyrins synthesized are the basic structure of biological porphyrins which are the active sites of numerous proteins, whose functions range from oxygen transfer and storage (hemoglobin and myoglobin) to electron transfer (cytochrome c, cytochrome oxidase) to energy conversion (chlorophyll). They also have been proven to be efficient sensitizers and catalyst in a number of chemical and photochemical processes especially photodynamic therapy (PDT). The diversity of their functions is due in part to the variety of metals that bind in the “pocket” of the porphyrin ring system (Fig. 1). Figure 1. Metallated Tetraphenylporphyrin Upon metalation the porphyrin ring system deprotonates, forming a dianionic ligand (Fig. 2). The metal ions behave as Lewis acids, accepting lone pairs of electrons ________________________________ § We all need to thank Jay Stephens for synthesizing the H2TPP 2 from the dianionic porphyrin ligand. Unlike most transition metal complexes, their color is due to absorption(s) within the porphyrin ligand involving the excitation of electrons from π to π* porphyrin ring orbitals. Figure 2. Synthesis of Zn(TPP) The electronic absorption spectrum of a typical porphyrin consists of a strong transition to the second excited state (S0 S2) at about 400 nm (the Soret or B band) and a weak transition to the first excited state (S0 S1) at about 550 nm (the Q band). -

Spectrum and the Technological Transformation of the Satellite Industry Prepared by Strand Consulting on Behalf of the Satellite Industry Association1

Spectrum & the Technological Transformation of the Satellite Industry Spectrum and the Technological Transformation of the Satellite Industry Prepared by Strand Consulting on behalf of the Satellite Industry Association1 1 AT&T, a member of SIA, does not necessarily endorse all conclusions of this study. Page 1 of 75 Spectrum & the Technological Transformation of the Satellite Industry 1. Table of Contents 1. Table of Contents ................................................................................................ 1 2. Executive Summary ............................................................................................. 4 2.1. What the satellite industry does for the U.S. today ............................................... 4 2.2. What the satellite industry offers going forward ................................................... 4 2.3. Innovation in the satellite industry ........................................................................ 5 3. Introduction ......................................................................................................... 7 3.1. Overview .................................................................................................................. 7 3.2. Spectrum Basics ...................................................................................................... 8 3.3. Satellite Industry Segments .................................................................................... 9 3.3.1. Satellite Communications .............................................................................. -

Infrared Astronomy Break: Sara and Rebeka

Astro 121, Spring 2014 Week 13 (April 24) Topic: Infrared astronomy Break: Sara and Rebeka Reading for this week: As we switch to looking at observing at wavelengths other than visible light, we’re moving beyond what Chromey covers. For this week, I’ve suggested reading from two sources. Glass gives a good introduction to the infrared and covers much of the practical material about filter systems, etc. McLean then fills in more details of practicalities of instrumentation for the infrared and how it is different from the optical. • Chromey briefly discusses the main broadband IR filter system in Section 10.4.3. • Glass, Handbook of Infrared Astronomy. In the same series as the book by Howell, this is a relatively new book with excellent coverage of infrared astronomy. Reading: Chapter 2 (The Infrared Sky); Chapter 3 (Photometry) through 3.2; and Chapter 6 (Instrumentation). You may also want to skim the rest of Chapter 3 and all of Chapter 4; they concentrate on applications of infrared photometry and spectroscopy, respectively. • McLean, Electronic Imaging in Astronomy (second edition). Ian McLean was one of the people most closely involved in the development and use of the early infrared arrays, and this is an area where this book stands out. Read Chapter 11, skipping pp. 400–404 (and in general reading the chapter for understanding of concepts rather than lots of details). One bit of physics that is worth reviewing for this week is the concept from thermodynamics that good absorbers are also good emitters, and correspondingly that the reflectivity R of some object is related to its emissivity ε by ε = 1 – R. -

Assessment of Spatial and Temporal Properties of Ka/Q Band Earth-Space Radio Channel Across Europe Using Alphasat Aldo Paraboni

Received: 28 February 2018 Revised: 19 April 2019 Accepted: 27 April 2019 DOI: 10.1002/sat.1313 SPECIAL ISSUE PAPER Assessment of spatial and temporal properties of Ka/Q band earth‐space radio channel across Europe using Alphasat Aldo Paraboni payload Spiros Ventouras1 | Antonio Martellucci11 | Richard Reeves1 | Emal Rumi1 | Fernando P. Fontan2 | Fernando Machado2 | Vicente Pastoriza2 | Armando Rocha3 | Susana Mota3 | Flavio Jorge3 | Athanasios D. Panagopoulos4 | Apostolos Z. Papafragkakis4 | Charilaos I. Kourogiorgas4 | Ondrej Fiser5 | Viktor Pek5 | Petr Pesice5 | Martin Grabner6 | Andrej Vilhar7 | Arsim Kelmendi7 | Andrej Hrovat7 | Danielle Vanhoenacker‐Janvier8 | Laurent Quibus8 | George Goussetis9 | Alexios Costouri9 | James Nessel10 1 STFC Rutherford Appleton Laboratory, RAL Space, Oxford, UK Summary 2 Escola de Enxeñaría de Telecomunicación, The upcoming migration of satellite services to higher bands, namely, the Ka‐ and University of Vigo, Vigo, Spain Q/V‐bands, offers many advantages in terms of bandwidth and system capacity. 3 Dep. Elect. Telec. e Informática, Instituto de However, it poses challenges as propagation effects introduced by the various atmo- Telecomunicações, Aveiro, Portugal 4 School of Electrical and Computer spheric phenomena are particularly pronounced in these bands and can become a Engineering, National Technical University of serious constraint in terms of system reliability and performance. This paper presents Athens, Athens, Greece the goals, organisation, and preliminary results of an ongoing large‐scale European 5 Meteorological Department, Institute of Atmospheric Physics ASCR, Prague, Czech coordinated propagation campaign using the Alphasat Aldo Paraboni Ka/Q band sig- Republic nal payload on satellite, performed by a wide scientific consortium in the framework 6 TESTCOM, Czech Metrology Institute, Prague, Czech Republic of a European Space Agency (ESA) project. -

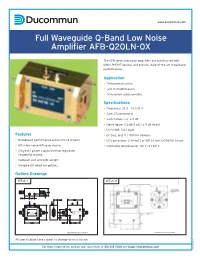

Full Waveguide Q-Band Low Noise Amplifier AFB-Q20LN-0X

www.ducommun.com Full Waveguide Q-Band Low Noise Amplifier AFB-Q20LN-0X The AFB series low noise amplifiers are constructed with MMICWT-A-7 PHEMT devices and provide state-of-the-art broadbandWT -A-8 performances. 0.096 DIA x THRU WR-28 W/UG599/U FLANGE 4PLS OR WR-42 W/UG595/U FLANGE 1 PLS Application • Telecommunication D M S D/ M S / /C / N N: / / N: C: N: : : X X X X X X X X X X X XX X / X XX • Test instrumentation X / X X X X X X X X X X • Transceiver subassemblies Specifications SIZE L W LM 0.096 DIA x THRU WR-28 W/UG599/U FLANGE SMALL 1.73 1.20 1.63 OUTPUT CONNECTOR CAN BE VARIED ON CUSTOMER'S REQUEST • Frequency: 33.0 -4 PL45.0S GHz OR WR-42 W/UG595/U FLANGE LARGE 2.53 1.30 2.43 K BAND ONLY APPLY TO SMALL SIZE SIZE L WLM • Gain:SMAL L 201.73 dB nominal1.20 1.63 LARGE 2.53 1.30 2.43 Dimensions are in inches Dimensions are in inches • Gain flatness: +/- 2.0 dB WT-A-9 WT-A-10 • Noise figure: 3.5 dB (typ) / 5.0 dB (max) WR-28 W/UG599/U FLANGE • I/O VSWR: 2.0:1 (typ) 2 PLS Features • DC bias: 8-12 V / 100 mA nominal • Broadband performance across entire Q-band • I/O connectors: 2.4mm(F) or WR-22 with UG383/U flange • Ultra-low noise with gain choice • Operating temperature: -40˚C to +50˚C M/N: XXXXX S/N: XXXXX • Single DC power supply/internal regulated D/C: XX/XX sequential biasing • Compact size and light weight WR-15 W/UG385/U FLANGE 4-40 x 0.20 DP OR WR-10 W/UG387/U MOD FLANGE 2 PLS 2 PLS • Variable I/O interface options 0.096 DIA x THRU 8 PLS Outline Drawings Dimensions are in inches Dimensions are in inches WT-A-1 WT-A-2 WT-A-11 WT-A-12 0.089 DIA X THRU 4 PLS M/N: XXXXX 4-40 x 0.20 DP S/N: XXXXX WR-10 W/UG 387/U-MOD FLANGE M/N: XXXXX D/C: XX/XX S/N: XXXXX 4 PLS OR WR-15 W/UG 385/U FLANGE D/C: XX/XX 4-40 x 0.20 DP 2 PLS 4 PLS M/N: XXXXX S/N: XXXXX D/C: XX/XX BAND L HW V,E, & W 1.50 1.00 0.75 M/N: XXXXX Q & U 1.80 1.13 1.13 S/N: XXXXX D/C: XX/XX Dimensions are in inches Dimensions areDimensions in inches are in inches Dimensions are in inches AllWT specifications-A-3 are subject to change without notice. -

Happy Holidays to All Time to Renew It Was a Happy Day for Those of Us Who Gathered for Our Annual Holiday Luncheon at the Sea Cliff Inn on December 13, 2014

DECEMBER 2014 Happy Holidays to All Time to Renew It was a happy day for those of us who gathered for our annual holiday luncheon at the Sea Cliff Inn on December 13, 2014. The food was excellent and the fellowship amongst our club SCCARC Membership Renewals members was superb. As usual, our drawing was especially fun as we all carefully watched our Due January 1; tickets in anticipation of hearing one of our ticket numbers called. We were only sorry that If you have already renewed your some of our members were unable to join us because we missed those were unable to partici- membership for 2015, thank you! If pate in the festivities you haven’t, please do it now. Annual dues are $25 for full members, $6 each for each additional member at the same mailing address, and $10 for full-time students age 18 or under. Dues may be paid in cash or check (payable to SCCARC) in person, at regular Club meetings, or checks may be mailed to SCCARC, P.O. Box 238, Santa Cruz, CA 95061-0238. If you have any questions you can email the Secretary Michael Usher <[email protected]> I don’t know about all of the tables, but at the one where I was seated, the “tech talk” was Secretary or Treasurer. We appreciate all of lively. Between Kerry Veenstra, K3RRY, Ron Skelton, W6WO, Steve Petersen, AC6P, and Jeff the work that this team contributed for our Lieberman, AE6KS, various aspects of propagation were the topic of interest. welfare over the past ten years. -

Photophysics of Chlorin E6: from One- and Two-Photon Absorption To

RSC Advances PAPER View Article Online View Journal | View Issue Photophysics of chlorin e6: from one- and two- photon absorption to fluorescence and Cite this: RSC Adv.,2017,7, 10992 phosphorescence† Hugo Gattuso,ab Antonio Monariab and Marco Marazzi*ab We present the study of optical and photophysical properties of chlorin e6, a known photosensitizer producing singlet oxygen. The linear and non-linear optical properties have been studied taking into account the dynamical and vibrational effects both by using Wigner distribution or coupling with molecular dynamics. A force field correctly describing the out-of-plane vibrations has been properly Received 23rd December 2016 parameterized. The photophysical study revealed a possible efficient population of the triplet manifold, Accepted 5th February 2017 from the S1 minimum region. Hence, fluorescence and singlet oxygen production are shown to coexist. DOI: 10.1039/c6ra28616j Two-photon absorption high cross-section and far infrared absorption also suggest the possible use of rsc.li/rsc-advances chlorin e6 as an efficient sensitizer in two-photon absorption based phototherapy. Creative Commons Attribution 3.0 Unported Licence. 1 Introduction aspects of a potential phototherapeutic drug is its ability to populate the triplet manifold. In that respect, relatively high Photodynamic therapy,1–6 based on photosensitization of bio- spin–orbit coupling and low energy gaps between triplet and logical targets, is an emerging therapeutic strategy used to treat singlet states are generally required. a number of pathologies including infections,7 skin diseases,8 Furthermore, in order to assure the efficient use of the drug and certain types of cancers.9 It involves the administration of the absorbed wavelengths should be displaced as much as an inert drug to the patient that is subsequently activated by possible toward the red. -

3.0 KLM Sensor Package

3.0 DESCRIPTION OF THE NOAA KLM SENSOR PACKAGE This section describes the characteristics of the NOAA KLM series instruments. The normal suite of instruments onboard the NOAA KLM series includes the following instruments: AVHRR/3, HIRS/3, AMSU-A and -B, SEM-2, DCS/2, SARSAT and sometimes SBUV/2. A detailed description of each instrument is provided in the respective subsections shown below. The instrument descriptions contain information such as spectral channel characteristics, system performance characteristics and additional information on the modules or subsystems that comprise the instrument. Table 1.2.1.3-1 provides a list of sensors flown onboard on each NOAA KLM spacecraft. 3.1 ADVANCED VERY HIGH RESOLUTION RADIOMETER/3 (AVHRR/3) 3.1.1 INSTRUMENT OPERATION This section describes the six channel Advanced Very High Resolution Radiometer (AVHRR/3) developed by ITT-A/CD. The AVHRR/3 is used as the meteorological imaging system of the NOAA KLM spacecraft. The AVHRR/3 is an imaging system in which a small field of view (1.3 milliradians by 1.3 milliradians) is scanned across the earth from one horizon to the other by continuous 360 degree rotation of a flat scanning mirror. The orientation of the scan lines is perpendicular to the spacecraft orbit track and the speed of rotation of the scan mirror is selected so that adjacent scan lines are contiguous at the subsatellite (nadir) position. Complete strip maps of the earth from pole to pole are thus obtained as the spacecraft travels in orbit at an altitude of approximately 833 km (450 n. -

IRMMW-Thz 2018)

2018 43rd International Conference on Infrared, Millimeter, and Terahertz Waves (IRMMW-THz 2018) Nagoya, Japan 9-14 September 2018 Pages 578-1320 IEEE Catalog Number: CFP18IMM-POD ISBN: 978-1-5386-3810-1 2/2 Copyright © 2018 by the Institute of Electrical and Electronics Engineers, Inc. All Rights Reserved Copyright and Reprint Permissions: Abstracting is permitted with credit to the source. Libraries are permitted to photocopy beyond the limit of U.S. copyright law for private use of patrons those articles in this volume that carry a code at the bottom of the first page, provided the per-copy fee indicated in the code is paid through Copyright Clearance Center, 222 Rosewood Drive, Danvers, MA 01923. For other copying, reprint or republication permission, write to IEEE Copyrights Manager, IEEE Service Center, 445 Hoes Lane, Piscataway, NJ 08854. All rights reserved. *** This is a print representation of what appears in the IEEE Digital Library. Some format issues inherent in the e-media version may also appear in this print version. IEEE Catalog Number: CFP18IMM-POD ISBN (Print-On-Demand): 978-1-5386-3810-1 ISBN (Online): 978-1-5386-3809-5 ISSN: 2162-2027 Additional Copies of This Publication Are Available From: Curran Associates, Inc 57 Morehouse Lane Red Hook, NY 12571 USA Phone: (845) 758-0400 Fax: (845) 758-2633 E-mail: [email protected] Web: www.proceedings.com TABLE OF CONTENTS TAILORED NANO-ELECTRONICS AND PHOTONICS WITH 2D MATERIALS ....................................................1 Miriam Serena Vitiello A NOVEL 300–520 GHZ TRIPIER WITH 50 % BANDWIDTH FOR MULTI-PIXEL HETERODYNE SIS ARRAY LOCAL OSCILLATOR SIGNAL GENERATION ........................................................2 J. -

Dual-Band Feed

The Development, Variations, and Applications ofan EHF Dual-Band Feed J.e. Lee • A compact, high-performance, EHF dual-band feed has been designed and developed. Subsequent improvements and modifications for a wide range ofantenna applications have been made. This article begins with three working examples ofexisting dual-band-antenna approaches, and discusses the dual-band feed that was developed for the antenna to be used on the scorrADM, a satellite communications terminal for mobile command posts. Excellent performance for the feed and antenna in both bands has been achieved. Other applications ofthe feed with appropriate modifications for dielectric-lens antennas, ADE (displaced-axis elliptical) antennas, and compact eleetronic-Iobing antennas are also d4cussed. These variations offeeds have been used in the FEP spot-beam antenna backup and a military-communications-satellite spot-beam antenna, in satellite-communications terminals on submarines, and in portable terminals (e.g., SCAMP and Advanced SCAMP). N THE MODERN WORLD, we have all encountered bands-hence the term dual band. The following sec many communications and radar terminals (1, 2] tions describe how we conceived and developed a dual I and have therefore glimpsed profiles of big and band feed, and how we subsequently improved and small antenna dishes. But we rarely have the chance to modified the feed for various antenna applications. see any details ofthe feeds ofthe antennas. In theory, we Background can design an antenna feed simply by applying the well known Maxwell equations with the appropriate bound Dual-Band Ratio ary conditions. In practice, however, only the simplest The dual-frequency-band ratio r is defined as the quo antenna reeds operating in a single frequency band can tientobtained bydividing the high-band center frequency be analyzed this way. -

Ka and Q Band Propagation Experiments in Toulouse Using ASTRA 3B and ALPHASAT Satellites Xavier Boulanger, Laurent Castanet

Ka and Q band propagation experiments in Toulouse using ASTRA 3B and ALPHASAT satellites Xavier Boulanger, Laurent Castanet To cite this version: Xavier Boulanger, Laurent Castanet. Ka and Q band propagation experiments in Toulouse using ASTRA 3B and ALPHASAT satellites. International Journal of Satellite Communications and Net- working, Wiley, 2018, 10.1002/sat.1261. hal-01840014 HAL Id: hal-01840014 https://hal.archives-ouvertes.fr/hal-01840014 Submitted on 16 Jul 2018 HAL is a multi-disciplinary open access L’archive ouverte pluridisciplinaire HAL, est archive for the deposit and dissemination of sci- destinée au dépôt et à la diffusion de documents entific research documents, whether they are pub- scientifiques de niveau recherche, publiés ou non, lished or not. The documents may come from émanant des établissements d’enseignement et de teaching and research institutions in France or recherche français ou étrangers, des laboratoires abroad, or from public or private research centers. publics ou privés. Ka and Q band Propagation Experiments in Toulouse using ASTRA 3B and ALPHASAT Satellites Xavier Boulanger 1 and Laurent Castanet 1 1ONERA – Université Fédérale de Toulouse (UFTMiP) – ElectroMagnetics & Radar Department, Propagation, Environment and Radio-communications research unit – BP 74025, 2 Avenue Edouard Belin, 31055 Toulouse Cedex 4, France SUMMARY From January 2008 to March 2011, ONERA operated in Toulouse, France, a beacon receiver able to collect the 19.7 GHz beacon signal of the HotBird 6 satellite. In March 2011, the RF chain was modified to be able to receive the 20.2 GHz ASTRA 3B beacon to benefit from a higher EIRP of the satellite. -

Binary Energy Source of the HH 250 Outflow

A&A 612, A73 (2018) https://doi.org/10.1051/0004-6361/201730917 Astronomy & © ESO 2018 Astrophysics Binary energy source of the HH 250 outflow and its circumstellar environment? Fernando Comerón1, Bo Reipurth2, Hsi-Wei Yen3, and Michael S. Connelley2,?? 1 European Southern Observatory, Alonso de Córdova 3107, Vitacura, Santiago, Chile e-mail: [email protected] 2 Institute for Astronomy, University of Hawaii at Manoa, 640 N. Aohoku Place, Hilo HI 96720, USA 3 European Southern Observatory, Karl-Schwarzschild-Strasse 2, 85748 Garching bei München, Germany Received 3 April 2017 / Accepted 28 December 2017 ABSTRACT Aims. Herbig-Haro flows are signposts of recent major accretion and outflow episodes. We aim to determine the nature and properties of the little-known outflow source HH 250-IRS, which is embedded in the Aquila clouds. Methods. We have obtained adaptive optics-assisted L-band images with the NACO instrument on the Very Large Telescope (VLT), together with N- and Q-band imaging with VISIR also on the VLT. Using the SINFONI instrument on the VLT we carried out H- and K-band integral field spectroscopy of HH 250-IRS, complemented with spectra obtained with the SpeX instrument at the InfraRed Telescope Facility (IRTF) in the JHKL bands. Finally, the SubMillimeter Array (SMA) interferometer was used to study the circum- stellar environment of HH 250-IRS at 225 and 351 GHz with CO (2–1) and CO (3–2) maps and 0.9 mm and 1.3 mm continuum images. Results. The HH 250-IRS source is resolved into a binary with 000: 53 separation, corresponding to 120 AU at the adopted distance of 225 pc.