PC Hardware and Booting

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Foundations for Music-Based Games

Die approbierte Originalversion dieser Diplom-/Masterarbeit ist an der Hauptbibliothek der Technischen Universität Wien aufgestellt (http://www.ub.tuwien.ac.at). The approved original version of this diploma or master thesis is available at the main library of the Vienna University of Technology (http://www.ub.tuwien.ac.at/englweb/). MASTERARBEIT Foundations for Music-Based Games Ausgeführt am Institut für Gestaltungs- und Wirkungsforschung der Technischen Universität Wien unter der Anleitung von Ao.Univ.Prof. Dipl.-Ing. Dr.techn. Peter Purgathofer und Univ.Ass. Dipl.-Ing. Dr.techn. Martin Pichlmair durch Marc-Oliver Marschner Arndtstrasse 60/5a, A-1120 WIEN 01.02.2008 Abstract The goal of this document is to establish a foundation for the creation of music-based computer and video games. The first part is intended to give an overview of sound in video and computer games. It starts with a summary of the history of game sound, beginning with the arguably first documented game, Tennis for Two, and leading up to current developments in the field. Next I present a short introduction to audio, including descriptions of the basic properties of sound waves, as well as of the special characteristics of digital audio. I continue with a presentation of the possibilities of storing digital audio and a summary of the methods used to play back sound with an emphasis on the recreation of realistic environments and the positioning of sound sources in three dimensional space. The chapter is concluded with an overview of possible categorizations of game audio including a method to differentiate between music-based games. -

Vintage Game Consoles: an INSIDE LOOK at APPLE, ATARI

Vintage Game Consoles Bound to Create You are a creator. Whatever your form of expression — photography, filmmaking, animation, games, audio, media communication, web design, or theatre — you simply want to create without limitation. Bound by nothing except your own creativity and determination. Focal Press can help. For over 75 years Focal has published books that support your creative goals. Our founder, Andor Kraszna-Krausz, established Focal in 1938 so you could have access to leading-edge expert knowledge, techniques, and tools that allow you to create without constraint. We strive to create exceptional, engaging, and practical content that helps you master your passion. Focal Press and you. Bound to create. We’d love to hear how we’ve helped you create. Share your experience: www.focalpress.com/boundtocreate Vintage Game Consoles AN INSIDE LOOK AT APPLE, ATARI, COMMODORE, NINTENDO, AND THE GREATEST GAMING PLATFORMS OF ALL TIME Bill Loguidice and Matt Barton First published 2014 by Focal Press 70 Blanchard Road, Suite 402, Burlington, MA 01803 and by Focal Press 2 Park Square, Milton Park, Abingdon, Oxon OX14 4RN Focal Press is an imprint of the Taylor & Francis Group, an informa business © 2014 Taylor & Francis The right of Bill Loguidice and Matt Barton to be identified as the authors of this work has been asserted by them in accordance with sections 77 and 78 of the Copyright, Designs and Patents Act 1988. All rights reserved. No part of this book may be reprinted or reproduced or utilised in any form or by any electronic, mechanical, or other means, now known or hereafter invented, including photocopying and recording, or in any information storage or retrieval system, without permission in writing from the publishers. -

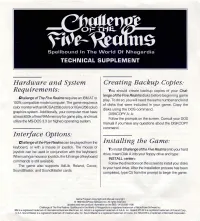

C5realms-Refcard

Hardware and System Creating Backup Copies: Requirements: You should create backup copies of your Chal lenge of the Five Realms disks before beginning game Challenge of The Five Realms requires an IBM AT or play. To do so, you will need the same number and kind 100% compatible model computer. The game requires a of dis~s that were included in your game. Copy the color monitor with an MCGA (256 color) or VGA (256 color) disks using the DOS command. graphics system. Additionally, your computer must have DISKCOPY A: A: at least 600k of free RAM memory for game play, and must Follow the prompts on the screen. Consult your DOS utilize the MS-DOS 3.3 (or higher) operating system. manual if you have any questions about the DISKCOPY command. Interface Options: Challenge of the Five Realms can be played from the Installing the Game: keyboard, or with a mouse or joystick. The mouse or To install Challenge of the Five Realms onto your hard joystick can be used in conjunction with the keyboard. drive, insert Disk A into your floppy drive and type: When using a mouse or joystick, the full range of keyboard INSTALL <enter> commands is still available. Follow the directions on the screen to install your disks The game also supports AdLib, Roland, Covox, to your hard drive. After the installation process has been Sound Blaster, and Sound Master cards. completed , type C5 from the prompt to begin the game. Game Program Copyright and Manual Copyright © 1992 MicroProse Software Inc. All rights reserved. Updates and new product information on the BBS - (412) 838-11 86 Challenge of The Five Realms: Spellbound in the World of Nhagardia is a registered trademark of MicroProse Software Inc. -

Intel® NUC Board DE3815TYBE Technical Product Specification

Intel® NUC Board DE3815TYBE Technical Product Specification July 2014 Order Number: H26598-004 The Intel NUC Board DE3815TYBE may contain design defects or errors known as errata that may cause the product to deviate from published specifications. Current characterized errata are documented in the Intel NUC Board DE3815TYBE Specification Update. Revision History Revision Revision History Date 001 First release of the Intel® NUC Board DE3815TYBE Technical Product April 2014 Specification 002 Specification Clarification April 2014 003 Specification Clarification June 2014 004 Specification Clarification July 2014 Disclaimer This product specification applies to only the standard Intel® NUC Board with BIOS identifier TYBYT10H.86A. INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL’S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. UNLESS OTHERWISE AGREED IN WRITING BY INTEL, THE INTEL PRODUCTS ARE NOT DESIGNED NOR INTENDED FOR ANY APPLICATION IN WHICH THE FAILURE OF THE INTEL PRODUCT COULD CREATE A SITUATION WHERE PERSONAL INJURY OR DEATH MAY OCCUR. All Intel® NUC Boards are evaluated as Information Technology Equipment (I.T.E.) for use in personal computers (PC) for installation in homes, offices, schools, computer rooms, and similar locations. The suitability of this product for other PC or embedded non-PC applications or other environments, such as medical, industrial, alarm systems, test equipment, etc. -

Contents: Sound Blaster Live! Value Sound Card User's Guide

Contents: Sound Blaster Live! Value Sound Card User's Guide Sound Blaster Live! Value Sound Card User's Guide Safety Instructions Introduction Setup Using the Sound Card Software Troubleshooting Specifications Internal Connectors Regulatory Information in this document is subject to change without notice. © 1998-2000 Creative Technology Ltd. All rights reserved. Trademarks used in this text: Sound Blaster and Blaster are registered trademarks, and the Sound Blaster Live! logo, the Sound Blaster PCI logo, EMU10K1, E-mu Environmental Modeling, Environmental Audio, Creative Multi Speaker Surround, and DynaRAM are trademarks of Creative Technology Ltd. in the United States and/or other countries. E-Mu and SoundFont are registered trademarks of E-mu Systems, Inc. Microsoft, Windows, and Windows NT are registered trademarks of Microsoft Corporation. Other trademarks and trade names may be used in this document to refer to either the entities claiming the marks and names or their products. Creative Technology Ltd. disclaims any proprietary interest in trademarks and trade names other than its own. This product is covered by one or more of the following U.S. patents: 4,506,579; 4,699,038; 4,987,600; 5,013,105; 5,072,645; 5,111,727; 5,144,676; 5,170,369; 5,248,845; 5,298,671; 5,303,309; 5,317,104; 5,342,990; 5,430,244; 5,524,074; 5,698,803; 5,698,807; 5,748,747; 5,763,800; 5,790,837. Version 1.00 July 2000 file:///C|/Terrys/index.htm [1/2/2001 1:47:24 PM] Using the Sound Card: Sound Blaster Live! Value Sound Card User's Guide Back to Contents Page -

Montegotm DDL Eight-Channel Surround Sound Card Featuring Dolby® Digital Live

MontegoTM DDL Eight-Channel Surround Sound Card Featuring Dolby® Digital Live www.TurtleBeach.com Notices Montego DDL Users Guide Version 6 Software and documentation copyright © 2005 - 2009 Voyetra Turtle Beach, Inc. All rights reserved. No part of this publication may be reproduced or transmitted by any means or in any form without prior written consent from Voyetra Turtle Beach, Inc. (“VTB”). In no event will VTB be liable for direct, indirect, special, exemplary, incidental, or consequential damages resulting from any defect or omission in this manual, even if advised of the possibility of such damages. In the interest of continued product development, VTB reserves the right to make improvements to this manual and the products it describes at any time, without notices or obligation. Turtle Beach, the Turtle Beach Logo, Montego DDL, and Ear Force are trademarks of VTB. Voyetra is a registered trademark of VTB. Dolby and the Double D symbol are registered trademarks of Dolby Labs. Windows and Windows XP Media Center are registered trademarks of Microsoft Corporation. Pentium is a registered trademark of Intel Corporation. All other trademarks are the properties of their respective companies and are hereby acknowledged. Use of this software is subject to the terms and conditions of the End-User Software License Agreement. Montego DDL is a product of: Voyetra Turtle Beach, Inc. 150 Clearbrook Road, Ste. 162, Elmsford, NY 10523 USA www.TurtleBeach.com Technical Support Knowledge Base: Go to the Turtle Beach web site www.turtlebeach.com and click on Support > Sound Cards > PCI Sound Cards > Montego DDL. This will bring up the list of articles Driver Downloads: From the same support page, next to the 'Knowledge Base' button click on Downloads > Sound Cards > PCI Sound Cards > Montego DDL. -

Ultimate Edge 5.1 High Definition Plus PSA2 HD

User’s Guide Ultimate Edge™ 5.1 High Definition 24-bit Sound Card ™ plus PSA2 HD Philips Sound Solutions PHILIPS Philips Sound Solutions SOFTWARE END USER LICENSE AGREEMENT THIS SOFTWARE END USER LICENSE AGREEMENT (THIS “AGREEMENT”) IS A LEGAL AND BINDING AGREEMENT BETWEEN YOU (EITHER AN INDIVIDUAL OR ENTITY) AND PHILIPS ELECTRONICS NORTH AMERICA CORPORATION, with OFFICES AT 1251 Avenue of the Americas, New York, New York 10020, USA ("PHILIPS"), REGARDING THE USE OF THE PHILIPS SOFTWARE (THE “SOFTWARE”) PROVIDED WITH THE PHILIPS ULTIMATE EDGE SOUND CARD (THE “PRODUCT”), WHICH INCLUDES USER DOCUMENTATION PROVIDED IN ELECTRONIC FORM. BY INSTALLING OR USING THE SOFTWARE, YOU AGREE TO ALL OF THE TERMS AND CONDITIONS OF THIS AGREEMENT. IF YOU DO NOT AGREE TO THESE TERMS AND CONDITIONS, DO NOT INSTALL OR USE THE SOFTWARE, AND RETURN THE PRODUCT, THE SOFTWARE, ALL MANUALS, DOCUMENTATION, AND PROOF OF PAYMENT TO PHILIPS WITHIN THIRTY (30) DAYS OF PURCHASE FOR A FULL REFUND. Grant of License. This Agreement grants you a non-exclusive, nontransferable, non-sublicensable license to install and use one (1) copy of the specified version of the Software in object code format, in operating environment(s) authorized by Philips for internal purposes only, on only one computer. This license does not permit you to use more than one instance of any copy of the Software. The Software is "in use" on a computer when it is loaded into the temporary memory (i.e. RAM) or installed into the permanent memory (e.g., hard disk, CD-ROM, or other storage device) of that computer. -

Chiptune Synthesis

- UFEE63-30-3 - A modern implementation of chiptune synthesis by Philip Phelps (#03974520) Summary A chiptune can be broadly categorised as a piece of music produced by sound chips in home computer/ games systems popular in the 1980s into the 1990s. The synthesis techniques often employed in chiptunes involve the careful control of the hardware features available in the sound chips. Such chips generally featured a limited number of simple oscillators with simple waveforms such as square, triangle, pseudorandom noise, and so on. In order to create more interesting sounds, chiptune composers rely on software synthesis structures that are used to configure the sound chip to alternate between waveforms, and to alter the pitch of the oscillators. MaxMSP is a graphical programming environment developed by Cycling’74. This report documents the reasons behind the decision to choose MaxMSP for the design and implementation of a software synthesiser for the creation of chiptunes. The report presents the detailed research into the sound hardware, and software used for composing chiptunes, exposing the differences in user interface design between modern composition software tools such as MIDI sequencers and historic composition tools such as trackers. Several pieces of historic software are examined; with elements of each user interface being assessed for inclusion in a modern software synthesiser user interface. The report also explains in detail the internal hardware structure of several popular sound chips (such as the General Instruments AY-3-8910) and examines several examples of software structures used to control the hardware synthesis structures inside the chips. The report documents the design of numerous software modules (programmed in the MaxMSP environment) and explains how each module can be combined to form the software synthesiser. -

How to Use This Manual Creative Sound Blaster Audigy Creative Audio Software

How to use this manual Creative Sound Blaster Audigy Creative Audio Software Information in this document is subject to change without notice and does not represent a commitment on the part of Creative Technology Ltd. No part of this manual may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, for any purpose without the written permission of Creative Technology Ltd. The software described in this document is furnished under a license agreement and may be used or copied only in accordance with the terms of the license agreement. It is against the law to copy the software on any other medium except as specifically allowed in the license agreement. The licensee may make one copy of the software for backup purposes only. The Software License Agreement is found in a separate folder on this installation CD. The copyright and disclaimer, including trademark issues are also found in the same folder. Important: This PDF file has been designed to provide you with complete product knowledge. The following are instructions on how to make use of this PDF file effectively by launching applications and help files, as well as accessing relevant web sites, where applicable, via specially prepared links. • To launch applications, Help files or to access relevant web sites, click the blue text, or whenever the symbol or appears on the object or text. • For best viewing, this PDF is by default set to "Fit Width" so that all the contents on every page is visible. If you are unable to read the text clearly, press Ctrl + <+> to zoom in or Ctrl + <-> to zoom out. -

ES1788 Audiodrive® Product Brief

ES1788 AudioDrive® Product Brief DESCRIPTION FEATURE HIGHLIGHTS The ES1788 AudioDrive is a mixed-signal single-chip solution that Single, high-performance, mixed-signal, 16-bit stereo VLSI chip adds 16-bit stereo sound and FM music synthesis to personal for digital audio computers. It includes an embedded microprocessor, a 20-voice High-quality, 20-voice ESFM™ music synthesizer; patents ESFM™ music synthesizer, 16-bit stereo wave ADC and DAC, 16- pending bit stereo music DAC, MPU-401 UART mode serial port, dual game ports, hardware master volume control, two serial port Patented ESPCM compression interfaces to external DSP and external wavetable music Record and Playback Features synthesizer, DMA control logic with FIFO, and ISA bus inferface Record, compress, and play back voice, sound, and music logic. There are three stereo inputs (typically line, CD Audio, and auxiliary line) and a mono microphone input to an internal preamp. Programmable sample rate from 4 kHz to 44.1 kHz for record All of this on a single chip that can be designed into a and playback motherboard, add-on card, or integrated into other peripheral 3-button hardware volume control for up, down, and mute cards such as Fax/Modem, VGA, LAN, I/O, etc. Mixer controlled record and playback with programmable The ES1788 AudioDrive can record, compress, and play back logarithmic volume controls voice, sound, and music with built-in 6-channel mixer controls. Inputs and Outputs Using two high-performance DMA channels, the ES1788 supports full-duplex analog operation for simultaneous record and playback. MIDI serial port compatible with MPU-401 UART mode The ESFM™ synthesizer has extended capabilities within native ESS high-performance integrated dual game port mode operation providing superior sound and power-down Address decode for joysticks capabilities. -

Spellcastllfg 301 Sprin6l.,\\.L\ What Is a LEGEND Adventure Game?

STEVE MERETZKY'S SPELLCASTllfG 301 SPRIN6l.,\\.l\ What Is A LEGEND Adventure Game? In an adventure game from Legend, you become the main character in an evolv ing story that takes place in a world populated with interesting people, places, and things. You see this world through your main character's eyes, and you play the game by directing his actions. Like a book or a movie, the story unfolds as you travel from location to location, encountering situations which require action on your part. You can think of each of these situations as a puzzle. The key to solving these puzzles will often be creative thinking and clever use of objects you have picked up in your travels. You will get points as you solve puzzles, and your score will help you monitor your progress. Throughout the game the richly textured graphics, prose, sound effects and music will draw you into a spellbinding adventure that could only be brought to you by the master storytellers of Legend Entertainment Company. Legend Entertainment Company 14200 Park Meadow Drive Chantilly, Virginia 22021 703-222-8500 U.S. Customer Support: 1-800-658-8891, 9:00 a.m. - 5:00 p.m. EDT/EST European Customer Support: 081-877-0880 FAX: 703-968-5151 CompuServe E-~ail 76226,2356 24-Hour Hint Line: 1-900-PRO-KLUE (1-900-776-5583) $.75 For the first minute, $.50 for each minute thereafter Hint books are available - call 1-800-658-8891 to order Table Of Contents Introduction ....................................................................................................... 4 Quick Start: Installation ................................................................................. 6 Quick Start: Playing the Game .................................................................... -

Sound Blaster Series Hardware Programming Guide

Sound Blaster Series Hardware Programming Guide Hardware Overview Digital Sound Processor Mixer MIDI Port License Agreement/Limitation And Disclaimer Of Warranties PLEASE NOTE : BY DOWNLOADING AND/OR USING THE SOFTWARE AND/OR MANUAL ACCOMPANYING THIS LICENSE AGREEMENT, YOU ARE HEREBY AGREEING TO THE FOLLOWING TERMS AND CONDITIONS: The software and related written materials, including any instructions for use, are provided on an "AS IS" basis, without warranty of any kind, express or implied. This disclaimer of warranty expressly includes, but is not limited to, any implied warranties of merchantability and/or of fitness for a particular purpose. No oral or written information given by Creative Technology Ltd., its suppliers, distributors, dealers, employees, or agents, shall create or otherwise enlarge the scope of any warranty hereunder. Licensee assumes the entire risk as to the quality and the performance of such software and licensee application. Should the software, and/or Licensee application prove defective, you, as licensee (and not Creative Technology Ltd., its suppliers, distributors, dealers or agents), assume the entire cost of all necessary correction, servicing, or repair. RESTRICTIONS ON USE Creative Technology Ltd. retains title and ownership of the manual and software as well as ownership of the copyright in any subsequent copies of the manual and software, irrespective of the form of media on or in which the manual and software are recorded or fixed. By downloading and/or using this manual and software, Licensee