Reliability of Gallium Arsenide Devices

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

DFB Lasers Between 760 Nm and 16 Μm for Sensing Applications

Sensors 2010, 10, 2492-2510; doi:10.3390/s100402492 OPEN ACCESS sensors ISSN 1424-8220 www.mdpi.com/journal/sensors Review DFB Lasers Between 760 nm and 16 µm for Sensing Applications Wolfgang Zeller *, Lars Naehle, Peter Fuchs, Florian Gerschuetz, Lars Hildebrandt and Johannes Koeth nanoplus Nanosystems and Technologies GmbH, Oberer Kirschberg 4, 97218 Gerbrunn, Germany; E-Mails: [email protected] (L.N.); [email protected] (P.F.); [email protected] (F.G.); [email protected] (L.H.); [email protected] (J.K.) * Author to whom correspondence should be addressed; E-Mail: [email protected]; Tel.: +49-931-90827-10; Fax: +49-931-90827-19. Received: 20 January 2010; in revised form: 22 February 2010 / Accepted: 6 March 2010 / Published: 24 March 2010 Abstract: Recent years have shown the importance of tunable semiconductor lasers in optical sensing. We describe the status quo concerning DFB laser diodes between 760 nm and 3,000 nm as well as new developments aiming for up to 80 nm tuning range in this spectral region. Furthermore we report on QCL between 3 µm and 16 µm and present new developments. An overview of the most interesting applications using such devices is given at the end of this paper. Keywords: DFB; laser; QCL; sensing Classification: PACS 42.55.Px; 42.62.Fi; 42.62.-b 1. Introduction In recent years the importance of lasers in optical sensing has been continuously increasing [1]. Many apparatus use long-known techniques like fluorescence measurements after excitation by photons, e.g., to detect petroleum contamination in soils [2]. -

![Arxiv:1010.1610V1 [Physics.Ins-Det] 8 Oct 2010 Ai Mouneyrac, David Emndtetm Osat O H Rpigadde- and Illumination](https://docslib.b-cdn.net/cover/4871/arxiv-1010-1610v1-physics-ins-det-8-oct-2010-ai-mouneyrac-david-emndtetm-osat-o-h-rpigadde-and-illumination-1094871.webp)

Arxiv:1010.1610V1 [Physics.Ins-Det] 8 Oct 2010 Ai Mouneyrac, David Emndtetm Osat O H Rpigadde- and Illumination

Detrapping and retrapping of free carriers in nominally pure single crystal GaP, GaAs and 4H-SiC semiconductors under light illumination at cryogenic temperatures David Mouneyrac,1,2 John G. Hartnett,1 Jean-Michel Le Floch,1 Michael E. Tobar,1 Dominique Cros,2 Jerzy Krupka3∗ 1School of Physics, University of Western Australia 35 Stirling Hwy, Crawley 6009 WA Australia 2Xlim, UMR CNRS 6172, 123 av. Albert Thomas, 87060 Limoges Cedex - France 3Institute of Microelectronics and Optoelectronics Department of Electronics, Warsaw University of Technology, Warsaw, Poland (Dated: October 27, 2018) We report on extremely sensitive measurements of changes in the microwave properties of high purity non-intentionally-doped single-crystal semiconductor samples of gallium phosphide, gallium arsenide and 4H-silicon carbide when illuminated with light of different wavelengths at cryogenic temperatures. Whispering gallery modes were excited in the semiconductors whilst they were cooled on the coldfinger of a single-stage cryocooler and their frequencies and Q-factors measured under light and dark conditions. With these materials, the whispering gallery mode technique is able to resolve changes of a few parts per million in the permittivity and the microwave losses as compared with those measured in darkness. A phenomenological model is proposed to explain the observed changes, which result not from direct valence to conduction band transitions but from detrapping and retrapping of carriers from impurity/defect sites with ionization energies that lay in the semicon- ductor band gap. Detrapping and retrapping relaxation times have been evaluated from comparison with measured data. PACS numbers: 72.20.Jv 71.20.Nr 77.22.-d I. -

Basic Light Emitting Diodes

The following is for information purposes only and comes with no warranty. See http://www.bristolwatch.com/ Light Emitting Diodes Light Emitting Diodes are made from compound type semiconductor materials such as Gallium Arsenide (GaAs), Gallium Phosphide (GaP), Gallium Arsenide Phosphide (GaAsP), Silicon Carbide (SiC) or Gallium Indium Nitride (GaInN). The exact choice of the semiconductor material used will determine the overall wavelength of the photon light emissions and therefore the resulting color of the light emitted, as in the case of the visible light colored LEDs, (RED, AMBER, GREEN etc). Before a light emitting diode can "emit" any form of light it needs a current to flow through it, as it is a current dependent device. As the LED is to be connected in a forward bias condition across a power supply it should be Current Limited using a series resistor to protect it from excessive current flow. From the table above we can see that each LED has its own forward voltage drop across the PN junction and this parameter which is determined by the semiconductor material used is the forward voltage drop for a given amount of forward conduction current, typically for a forward current of 20mA. In most cases LEDs are operated from a low voltage DC supply, with a series resistor to limit the forward current to a suitable value from say 5mA for a simple LED indicator to 30mA or more where a high brightness light output is needed. Typical LED Characteristics Semiconductor Material Wavelength Color voltage at 20mA GaAs 850-940nm Infra-Red 1.2v GaAsP 630-660nm Red 1.8v GaAsP 605-620nm Amber 2.0v GaAsP:N 585-595nm Yellow 2.2v GaP 550-570nm Green 3.5v SiC 430-505nm Blue 3.6v GaInN 450nm White 4.0v 1 Multi-LEDs LEDs are available in a wide range of shapes, colors and various sizes with different light output intensities available, with the most common (and cheapest to produce) being the standard 5mm Red LED. -

The Low-Temperature Catalyzed Etching of Gallium Arsenide with Hydrogen Chloride Jeffrey L

The low-temperature catalyzed etching of gallium arsenide with hydrogen chloride Jeffrey L. Dupuie and Erdogan Gulari Department of Chemical Engineering, The University of Michiggn, Ann Arbor, Michigan 48109 (Received 18 September 1991; accepted for publication 10 January 1992) A heated tungsten filament has been used to catalyze the gas phase etching of gallium arsenide with hydrogen chloride at a substrate temperature of 563 K. Rapid etch rates, between 1 and 3 microns per minute, were obtained in a pure hydrogen chloride ambient in the pressure range of 3.3 to 20.0 Pascal. Low flow rates of hydrogen quenched the etching reaction, and resulted in degradation of the quality of the etched gallium arsenide surface. Dilution of the hydrogen chloride to 10.5% in helium reduced the etch rate to 63 nanometers per minute. The removal of 83 nm of gallium arsenide with the helium-diluted gas mixture resulted in a specular surface. X-ray photoelectron spectroscopy indicated that the gallium arsenide surface became enriched in gallium after the etch in helium-diluted hydrogen chloride. No tungsten or other metal contamination on the etched gallium arsenide surface was detected by x-ray photoelectron spectroscopy. BACKGROUND We reported previously that high purity aluminum ni- tride and silicon nitride films could be deposited by low- Development of a dielectric deposition scheme for the pressure chemical vapor deposition (LPCVD) at low sub- fabrication of viable gallium arsenide metal-insulator- strate temperatures through the catalytic action of a heated semiconductor devices will probably include an in situ sur- filament.5’6 In this process, a heated tungsten filament is face pretreatment prior to dielectric deposition due to a used to decompose ammonia. -

A Comparison of E/D-MESFET Gallium Arsenide and CMOS Silicon for VLSI Processor Design Mark K

Purdue University Purdue e-Pubs Department of Electrical and Computer Department of Electrical and Computer Engineering Technical Reports Engineering 12-1-1985 A Comparison of E/D-MESFET Gallium Arsenide and CMOS Silicon for VLSI Processor Design Mark K. Bettinger Purdue University Follow this and additional works at: https://docs.lib.purdue.edu/ecetr Bettinger, Mark K., "A Comparison of E/D-MESFET Gallium Arsenide and CMOS Silicon for VLSI Processor Design" (1985). Department of Electrical and Computer Engineering Technical Reports. Paper 551. https://docs.lib.purdue.edu/ecetr/551 This document has been made available through Purdue e-Pubs, a service of the Purdue University Libraries. Please contact [email protected] for additional information. A Comparison of E/D-MESFET Gallium Arsenide and CMOS Silicon for VLSI Processor Design Mark K. Bettinger TR-EE 85-18 December 1985 School of Electrical Engineering Purdue University West Lafayette, Indiana 47907 A COMPARISON OF E/D-MESFET GALLIUM ARSENIDE AND CMOS SILICON FOR VLSI PROCESSOR DESIGN Mark K. Bettinger TR-EE 85-18 December 1985 ACKNOWLEDGMENTS I acknowledge the guidance and assistance of my major professor, Veljko Milutinovic. He has provided opportunities to learn that I appreciate. I am also indebted to RCA-ATL for their support and guidance as well as their funding. I would also like to thank those at RCA-ATL who have provided assistance: Tom Geigel, Bill Heagerty, Walt Helbig, Wayne Moyers, Jeff Prid- more, and Rich Zeigert. Little of this work would have been completed without the support of my officemates. I also thank my good friend Lee Bissonette for all of her cheerful assistance. -

LOW LOSS ORIENTATION-PATTERNED GALLIUM ARSENIDE (Opgaas)

LOW LOSS ORIENTATION-PATTERNED GALLIUM ARSENIDE (OPGaAs) WAVEGUIDES FOR NONLINEAR INFRARED FREQUENCY CONVERSION Dissertation Submitted to The School of Engineering of the UNIVERSITY OF DAYTON In Partial Fulfillment of the Requirements for The Degree of Doctor of Philosophy in Electrical and Computer Engineering By Izaak Vincent Kemp Dayton, Ohio December 2012 LOW LOSS ORIENTATION-PATTERNED GALLIUM ARSENIDE (OPGaAs) WAVEGUIDES FOR NONLINEAR INFRARED FREQUENCY CONVERSION Name: Kemp, Izaak Vincent APPROVED BY: Dr. Andrew Sarangan Dr. Peter Powers Advisory Committee Chairman Committee Member Professor Professor Electrical and Computer Engineering Department of Physics Dr. Partha Banerjee Dr. Guru Subramanyam Committee Member Committee Member Professor Department Chair Electrical and Computer Engineering Electrical and Computer Engineering Dr. Rita Peterson Dr. Kenneth Schepler Committee Member Committee Member Adjunct Professor Adjunct Professor Electro-Optics Electro-Optics John G. Weber, Ph.D. Tony E. Saliba, Ph.D. Associate Dean Dean, School of Engineering School of Engineering &Wilke Distinguished Professor ii © Copyright by Izaak Vincent Kemp All rights reserved 2012 iii Distribution Statement A: Approved for public release, distribution is unlimited. This dissertation contains information regarding currently ongoing U.S. Department of Defense (DoD) research that has been approved for public release. Distribution of this dissertation is unlimited pursuant to DoD Directive 5230.24 subsection A4. Requests for further information may be referred to the author, Izaak V. Kemp AFRL/RYMWA. iv ABSTRACT LOW LOSS ORIENTATION-PATTERNED GALLIUM ARSENIDE (OPGaAs) WAVEGUIDES FOR NONLINEAR INFRARED FREQUENCY CONVERSION Name: Kemp, Izaak Vincent University of Dayton Advisor: Dr. Andrew Sarangan The mid-IR frequency band (λ = 2-5 μm) contains several atmospheric transmission windows making it a region of interest for a variety of medical, scientific, commercial, and military applications. -

Gallium Arsenide and Related Compounds for Device Applications

l 79 (1991 ACTA YSICA OOICA Α 1 oc I Ieaioa Scoo o Semicoucig Comous asowiec 199 GALLIUM ARSENIDE AND RELATED COMPOUNDS FOR DEVICE APPLICATIONS WOO Uiesiy o Yok e o Eecoics esigo Yok YO 5 UK A MOGA Uiesiy o Waes Coege o Cai Cai UK (eceie Augus 199θ e eice aicaios o gaium aseie a eae I— comou a aoy semicoucos ae eiewe A age o eecoic eices is escie a e cue sae o e a eomace is iicae o eac ye o eice e eices wic wi e escie ae asee eeco eices - as osciaos u o G GaAs MESEs — e wokose micowae soi sae eice some mooiic micowae iegae cicui /MMIC/ a eeoucio eices e use o moecua eam eiay ME o gow I- semicoucos wi gea coo oe e oig moe acio o e cosiues a e ickess o e eiaye as emie e cosucio o eices wi aomicay au ieaces ewee egios o iee o- ig a aoy e eecoic eices wic make use o suc au ee o -ucios icue ig eeco moiiy asisos eeoucio ioa asiso a ase ioes A ume o oe eices ase o muie aie a quaum we sucues is aso escie icuig esoa ueig eices ACS umes 7Ey 73Κρ 7s Intrdtn Gaium aseie a eae III- comous wee is iesigae as semicoucig maeias oe iy yeas ago e maeia oeies o ese comous ossess some oa simiaiies wi ose o a aceya semi- couco siico ey ae a simia cysaie sucue a e ieaomic oig is agey coae [1] u e III— comous wee aso ecogise o (97 9 Woo Mogα ei oica a eecoic oeies suc as a iec a ga a ig eeco moiiy a wee o ou i siico o gemaium ese oeies e e omise o ew a uique eices suc as ig eiciecy ig emies a ig sesos a ig see swicig eices ies wee siico cou o eaiy comee e easos ei ese eecoic a oica oeies a e cose- que iees i gaium aseie GaAs a simia III- comous ie i e eaie aue o ei eeco eegy a sucues akig GaAs as yica o III— semicoucos i wic we ae ieese Gallium arsenide has a direct energy band gap. -

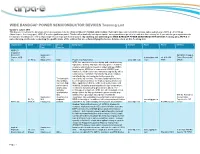

WIDE BANDGAP POWER SEMICONDUCTOR DEVICES Teaming List

WIDE BANDGAP POWER SEMICONDUCTOR DEVICES Teaming List Updated: July 8, 2013 This document contains the list of potential teaming partners for the WIDE BANDGAP POWER SEMICONDUCTOR DEVICES, solicited in RFI-0000004 and is published on ARPA-E eXCHANGE (https://arpa-e-foa.energy.gov), ARPA-E’s online application portal. This list will periodically undergo an update as organizations request to be added to this teaming list. If you wish for your organization to be added to this list please refer to https://arpa-e-foa.energy.gov/ for instructions. By enabling and publishing the WIDE BANDGAP POWER SEMICONDUCTOR DEVICES Teaming List, ARPA-E is not endorsing or otherwise evaluating the qualifications of the entities that are self-identifying themselves for placement on this Teaming List. Organization Name Organization Area of Background Website Email Phone Address Type Expertise ABB US Corporate Research Business > 940 Main Campus Center, ABB 1000 [email protected] +1 919 856 Drive, Raleigh NC Inc. Le Tang Employees Grid Power and Automation www.abb.com .com 3878 27606 APEI, Inc. specializes in developing and manufacturing high power density and high efficiency power electronic solutions and products based on wide bandgap (WBG) technologies. APEI, Inc.’s commercial ISO9001 and AS9100 certified Class 1000 manufacturing facility offers custom power substrate manufacturing, power module manufacturing, and microelectronics assembly Technologies manufacturing services. The manufacturing lines have that facilitate been designed to deliver the highest quality product for low-cost, high- those applications that need the best performance and performance, reliability, including a specialization in high temperature and/or plug- electronics manufacturing processes to 400 C. -

NOVEL MODELLING METHODS for MICROWAVE Gaas MESFET DEVICE ZHONG ZHENG a THESIS SUBMITTED for the DEGREE of DOCTOR of PHILOSOPHY

CORE Metadata, citation and similar papers at core.ac.uk Provided by ScholarBank@NUS NOVEL MODELLING METHODS FOR MICROWAVE GaAs MESFET DEVICE ZHONG ZHENG (M.Eng, University of Science and Technology of China, P.R.C) A THESIS SUBMITTED FOR THE DEGREE OF DOCTOR OF PHILOSOPHY DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING NATIONAL UNIVERSITY OF SINGAPORE 2010 i Acknowledgements First of all, I would like to deeply thank my supervisors, Professor Leong Mook Seng and A/Prof. Ooi Ban Leong, who have led me into this interesting world of device modelling, and given me full support for my study. I am here to express my sincere gratitude to them for their patient guidance, invaluable advices and discussions. I believe what I have learnt from them will always lead me ahead. I also want to thank other faculty staffs in NUS Microwave & RF group: Prof Yeo Swee Ping, Prof Li Le-Wei, Dr. Chen Xu Dong, Dr. Guo Yong Xin, Dr. Koen Mouthaan, and Dr. Hui Hon Tat, etc. for their significant guidance and support. I am also very grateful to these supporting staffs in NUS Microwave & RF group: Madam Guo Lin, Mr. Sing Cheng-Hiong and Madam Lee Siew-Choo for their kind assistances in PCB/MMIC fabrication and measurement. My gratitude also goes to all the friends in microwave division, for their kind help and for the wonderful time we shared together. Last but not least, I would like to thank my family, for their endless support and encouragement, which always be the greatest treasure of my life. ii Table of Contents Acknowledgements ……..………………………..……………..…...…………………i Table of Contents ...…………………………...……………………………………….ii Summary ……………………………………...…….…………………………………vi List of Figures……………………………………….……………………………..…viii List of Tables ….……………………………………..………….……………………xiii List of Symbols ……………………………………….……………….….……….….xv Chapter 1 Introduction ........................................................................................ -

Characterization and Applications of Low-Temperature-Grown MBE Gallium

AN ABSTRACT OF THE THESIS OF Pin Zhao for the degree of Master of Science in Materials Science through the Department of Electrical & Computer Engineering presented on January 14, 1994. Title:Characterization and Applications of Low-Temperature-Grown MBE Gallium Arsenide. Redacted for privacy Abstract approved: Thomas K. Plant Low-temperature (LT) MBE-grown GaAs material has recently been used for fast response, low dark current photodetectors.The material contains a high concentration of As precipitates which appear to act as spherical Schottky barriers with overlapping depletion regions making the GaAs semi-insulating. In this work, the electrical and optical characteristics of LT-GaAs are studied in p-i-n diodes, MSM photoconductors, and a new modulation-doped photoconductor using LT-GaAs grown at 225 °C, 300 °C, and 350 °C. The goal of this work was to measure the transport properties of LT-GaAs to resolve an ambiguity in the literature. Direct Hall mobility measurements proved unreliable due to high resistivity even in photoexcited samples. From the I-V behavior ofp-i-n diodes, an estimate of carrier lifetime ranging from 4 ps to 130 ps for growth temperatures from 225 °C to 350 °C was made. MSM photoconductors fabricated on the LT-GaAs showed sub-nanosecond response and no evidence of the long tail always found in MSM photodetectors on semi-insulating GaAs. The new modulation-doped LT-GaAs photoconductor shows a gain of 300, a mobility of 500 cm2 / Vs, and a response to wavelengths longer than 1500 nm. There appears to be both a transient, trap-related transport mechanism and a steady-state, recombination-related transport mechanism with significantly different properties. -

Algaas-On-Insulator Nonlinear Photonics

AlGaAs-On-Insulator Nonlinear Photonics Minhao Pu*, Luisa Ottaviano, Elizaveta Semenova, and Kresten Yvind** DTU Fotonik, Department of Photonics Engineering, Technical University of Denmark, Building 343, DK-2800 Lyngby, Denmark *[email protected]; **[email protected] The combination of nonlinear and integrated photonics has recently seen a surge with Kerr frequency comb generation in micro-resonators1 as the most significant achievement. Efficient nonlinear photonic chips have myriad applications including high speed optical signal processing2,3, on-chip multi-wavelength lasers4,5, metrology6, molecular spectroscopy7, and quantum information science8. Aluminium gallium arsenide (AlGaAs) exhibits very high material nonlinearity and low nonlinear loss9,10 when operated below half its bandgap energy. However, difficulties in device processing and low device effective nonlinearity made Kerr frequency comb generation elusive. Here, we demonstrate AlGaAs-on-insulator as a nonlinear platform at telecom wavelengths. Using newly developed fabrication processes, we show high-quality-factor (Q>105) micro-resonators with integrated bus waveguides in a planar circuit where optical parametric oscillation is achieved with a record low threshold power of 3 mW and a frequency comb spanning 350 nm is obtained. Our demonstration shows the huge potential of the AlGaAs-on-insulator platform in integrated nonlinear photonics. Desirable material properties for all-optical χ(3) nonlinear chips are a high Kerr nonlinearity and low linear and nonlinear losses to enable high four-wave mixing (FWM) efficiency and parametric gain. Many material platforms have been investigated showing the different trade-offs between nonlinearity and losses2-5,11-16. In addition to good intrinsic material properties, the ability to perform accurate and high yield processing is desirable in order to integrate additional functionalities on the same chip and also to decrease linear losses. -

Transition of Sic MESFET Technology from Discrete Transistors to High Performance MMIC Technology

Transition of SiC MESFET Technology from Discrete Transistors to High Performance MMIC Technology J.W. Milligan, J. Henning, S.T. Allen, A.Ward, P. Parikh, R.P. Smith, A. Saxler, Y. Wu, and J. Palmour Cree, Inc., 4600 Silicon Drive, Durham, NC 27703, (919) 313-5564, [email protected] Keywords: SiC, MESFET, MMIC, HPSI, HTOL, GaN Abstract Significant progress has been made in the development of SiC MESFET DEVICE PERFORMANCE SiC MESFETs and MMIC power amplifiers manufactured on 3-inch high purity semi-insulating (HPSI) 4H-SiC substrates. SiC MESFETs continue to mature in performance and MESFETs with a MTTF of over 200 hours when operated at a manufacturing process stability. These devices now TJ =295 °C are presented. High power SiC MMIC amplifiers achieve a power density of approximately 4.0 W/mm and are shown with excellent yield and repeatability using a power added efficiencies greater than 50% on a regular released foundry process. GaN HEMT operating life of over basis. As an example, Figure 2 shows a 1.0 mm gate 500 hours at a TJ =160 °C is shown. Finally, GaN HEMTs with 30 W/mm RF output power density are reported. periphery MESFET operating at 50V producing 4.0 watts of output power at 66% drain efficiency (54% PAE) at 3.5 GHz. INTRODUCTION SiC MESFETs offer significant advantages for next CW Load Pull Data at 3.5 GHz generation commercial and military systems. Increased 40 60 CW Power power density and higher operating voltage enable higher 36 PAE 50 performance, lighter weight, and wider bandwidth systems.