Switching Circuits for a Ferrite Core Storage

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

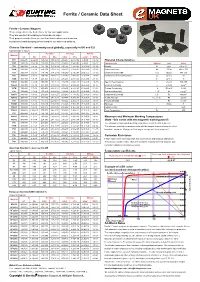

Ferrite / Ceramic Data Sheet

Ferrite / Ceramic Data Sheet Ferrite / Ceramic Magnets These magnets are the best choice for low cost applications. They are excellent at resisting corrosion due to water. Their properties make them an excellent choice when used in motors, loudspeakers and clamping devices and for use with reed switches. Chinese Standard - commonly used globally, especially in UK and EU Typical Range of Values Br Hc (Hcb) Hci (Hcj) BHmax Material mT kG kA/m kOe kA/m kOe kJ/m3 MGOe Y8T 200-235 2.0-2.35 125-160 1.57-2.01 210-280 2.64-3.52 6.5-9.5 0.8-1.2 Physical Characteristics Y10T 200-235 2.0-2.35 128-160 1.61-2.01 210-280 2.64-3.52 6.4-9.6 0.8-1.2 Characteristic Symbol Unit Value Y20 320-380 3.2-3.8 135-190 1.70-2.39 140-195 1.76-2.45 18.0-22.0 2.3-2.8 Density D g/cc 4.9 to 5.1 Y22H 310-360 3.1-3.6 220-250 2.76-3.14 280-320 3.52-4.02 20.0-24.0 2.5-3.0 Vickers Hardness Hv D.P.N 400 to 700 Y23 320-370 3.2-3.7 170-190 2.14-2.39 190-230 2.39-2.89 20.0-25.5 2.5-3.2 Compression Strength C.S N/mm2 680-720 Y25 360-400 3.6-4.0 135-170 1.70-2.14 140-200 1.76-2.51 22.5-28.0 2.8-3.5 Coefficient of Thermal Expansion C// 10-6/C 15 Y26H 360-390 3.6-3.9 220-250 2.76-3.14 225-255 2.83-3.20 23.0-28.0 2.9-3.5 C^ 10-6/C 10 Y26H-1 360-390 3.6-3.9 200-250 2.51-3.14 225-255 2.83-3.20 23.0-28.0 2.9-3.5 Specific Heat Capacity c J/kg°C 795-855 Y26H-2 360-380 3.6-3.8 263-288 3.30-3.62 318-350 4.00-4.40 24.0-28.0 3.0-3.5 Electrical Resistivity r m Ω.cm 1x1010 Y27H 370-400 3.7-4.0 205-250 2.58-3.14 210-255 2.64-3.20 25.0-29.0 3.1-3.6 Thermal Conductivity k W/cm°C 0.029 Y28 370-400 3.7-4.0 175-210 2.20-2.64 180-220 2.26-2.76 26.0-30.0 3.3-3.8 Modulus of Elasticity l / E Pa 1.8x1011 Y28H-1 380-400 3.8-4.0 240-260 3.02-3.27 250-280 3.14-3.52 27.0-30.0 3.4-3.8 Compression Strength C.S. -

A TWO DIMENSIONAL FERRITE-CORE MEMORY Bv M

A TWO DIMENSIONAL FERRITE-CORE MEMORY Bv M. M. FAROOQUI, S. P. SKiVASTAVA AND R. N. NEOGI (Tata Institute of Fundamental Research, Bomba),) Received January t0, 1957 (Communicated by Prof. Bernard P ABS'IXACT This paper describes a two dimensional matrix memory using ferrite- cores. A urtit consisting of 100 words of I 1 binary digits each has been cortstructed for parallel operation. The word drive is from a biasr switch-core matrix, while the digit drive makes use of pulse--trans- formers. Logic and circuit techniques enable high discrimination bet- ween wanted and unwanted signals. A semi-automatic method for testing the memory cores is also described. INTRODUCTION THE potentiality of magnetie fer¡ with a rectangular hysteresis loop as binary storage elements for digital computer was realised earlier by Forrester. x Later, Papian% s and almost simultaneously Rajchman4, ~ showed the practicability of such a system by successfully operating memories of fairly large capacity. This paper describes a modest attempt in this direction. A memory of I00 words, 11 bits each, has beca constructed to operate with a smaU digital computer at the Tata institute of Fundamental Research, Bombay. THE PRINClPLE OF OPERATION OF THE MEMORY The two stable states required for sto¡ binary information in magnetic cores ate the states of positive and negative magnetisation. These are the states corresponding to the position A0 and Ax on the hysteresis loop and can be termed as the 0- and the 1-states respectively (Fig. 2). Con- sider a number of sucia cores with ah ideaUy rectangular hysteresis character- istic, arranged in rows and columns in the form of a matrix. -

Magnetics in Switched-Mode Power Supplies Agenda

Magnetics in Switched-Mode Power Supplies Agenda • Block Diagram of a Typical AC-DC Power Supply • Key Magnetic Elements in a Power Supply • Review of Magnetic Concepts • Magnetic Materials • Inductors and Transformers 2 Block Diagram of an AC-DC Power Supply Input AC Rectifier PFC Input Filter Power Trans- Output DC Outputs Stage former Circuits (to loads) 3 Functional Block Diagram Input Filter Rectifier PFC L + Bus G PFC Control + Bus N Return Power StageXfmr Output Circuits + 12 V, 3 A - + Bus + 5 V, 10 A - PWM Control + 3.3 V, 5 A + Bus Return - Mag Amp Reset 4 Transformer Xfmr CR2 L3a + C5 12 V, 3 A CR3 - CR4 L3b + Bus + C6 5 V, 10 A CR5 Q2 - + Bus Return • In forward converters, as in most topologies, the transformer simply transmits energy from primary to secondary, with no intent of energy storage. • Core area must support the flux, and window area must accommodate the current. => Area product. 4 3 ⎛ PO ⎞ 4 AP = Aw Ae = ⎜ ⎟ cm ⎝ K ⋅ΔB ⋅ f ⎠ 5 Output Circuits • Popular configuration for these CR2 L3a voltages---two secondaries, with + From 12 V 12 V, 3 A a lower voltage output derived secondary CR3 C5 - from the 5 V output using a mag CR4 L3b + amp postregulator. From 5 V 5 V, 10 A secondary CR5 C6 - CR6 L4 SR1 + 3.3 V, 5 A CR8 CR7 C7 - Mag Amp Reset • Feedback to primary PWM is usually from the 5 V output, leaving the +12 V output quasi-regulated. 6 Transformer (cont’d) • Note the polarity dots. Xfmr CR2 L3a – Outputs conduct while Q2 is on. -

Ferrite and Metal Composite Inductors

Ferrite and Metal Composite Inductors Design and Characteristics © 2019 KEMET Corporation What is an Inductor? Coil Magnetic Magnetic flux φ (Wire) Field dφ Core e = - dt Material i The coil converts electric energy into magnetic energy and stores it. e Core Material Current through the coil of wire creates a magnetic field Air Ferrite Metal and stores it. (None) (Iron) Composite Different core materials change magnetic field strength. © 2019 KEMET Corporation Ferrite Inductor or Metal Composite Inductor? Ferrite InductorFerrite Metal InductorMetal Composite MaterialMaterial Type type Ni-ZnNi-Zn Mn-Zn Mn-Zn Fe based Fe Based Very Good!! No Good.. InductanceInductace GoodGood! Very Good No Good Very Good!! Magnetic Saturation Good! No Good.. Good! No Good.. Very Good!! MagneticThermal Saturation Property Good No Good Very Good Good! Very Good!! Good! Efficiency Very Good!! No Good.. Good! ThermalResistance Property of core Good No Good Very Good Efficiency SBC/SBCPGood TPI Very GoodMPC, MPCV Good Products MPLC, MPLCV Resistance of Core Very Good No Good Good © 2019 KEMET Corporation Ferrite and Metal Composite Comparison Advantage of Ferrite 1. Higher inductance with high permeability 2. Stable inductance in the right range High L and Low DCR capability Advantage of Metal Composite 1. Very slow saturation 2. Very stable saturation for the thermal Core Loss Comparison Good for Auto app especially Advantage of Ferrite Very low core loss in dynamic frequency range Mn-Zn Ferrite Metal Core Low power consumption capability © 2019 KEMET Corporation -

Switch Mode Power Supplies and Their Magnetics Tutorial

Datatronic Switch Mode Power Supplies and their Magnetics Many factors must be considered by designers when choosing the magnetic components required in today’s electronic power supplies DATATRONIC DISTRIBUTION, INC. Datatronic In today’s day and age the most often used topology for electronic power supplies is that of the Switch Mode Power Supply (SMPS), which is a major user of magnetics. In some applications the “older type” linear supplies are still used, but in the early 70’s SMPS came into being spurred by the development of faster switching transistors. This facilitated the use of much smaller magnetic components and greater efficiencies. DATATRONIC DISTRIBUTION, INC. Datatronic SMPS and their General Magnetic Usage In general, there are four different types of magnetic components that are needed for the typical SMPS. They include the Output Transformer, usually the most noticeable because of its size compared to the others, the Output Inductors, the Input Inductors and the Current Sense Transformer, each with its own important function. DATATRONIC DISTRIBUTION, INC. Datatronic SMPS and their General Magnetic Usage 1.The Output Transformer or “Main” Transformer takes the input voltage that is supplied to its primary winding and then transforms the input voltage to one or more voltages that are the output of the secondary winding or windings. 2. The Output Inductors are used to filter the output voltage so that the load “sees” a filtered DC voltage. DATATRONIC DISTRIBUTION, INC. Datatronic SMPS and their General Magnetic Usage 3. The Input Inductors filter out the noise generated by the switching transistors so that this noise isn’t emitted back to the source. -

INTRODUCTION:- Ferrites Are Ferromagnetic Material Containing Predominantly Oxides Iron Along with Other Oxides of Barium, Stron

INTRODUCTION:- Ferrites are ferromagnetic material containing predominantly oxides iron along with other oxides of barium, strontium, manganese, nickel, zinc, lithium and cadmium .Ferrites are ideally suited for making device like inductor core, circulators, memory devices and also for various microwave application. Although the saturation magnetisation of ferrites less than that of ferromagnetic alloys, they have advantages such as applicability at higher frequency, lower price and greater electrical resistance. Since 1950, soft ferrites have been widely studied and have become a field of interest of many researches because of their application potential in the modern electronics industry. The electrical and magnetic properties of these materials are structure sensitive and can be altered by doping or substitution. The substitution of aluminium in the inverse ferrites like Nickel, copper and cobalt ferrites have proved to be useful by increasing their saturation, magnetization, resistivity, however, at the cost of decrease of Curie temperature. Cadmium ferrite is a normal spinel ; its magnetic moment per unit cell is zero. Low magnetic high resistive ferrite are so applicable in the high frequency transformer cores. The addition of aluminium which has strong preference for the octahedral sites should exhibit the decrease of the magnetisation because aluminium is nonmagnetic. As aluminium content increases, the magnetic moment of unit cell decreases that means show triangular spin moment, their occurs a reduction in the sub lattice interaction. The removal of iron ions from magnetic sublattice and substitution of the nonmagnetic aluminium ion in its place weakens the magnetism. Due to this substitution improves catalytic, dielectric and magnetic properties, as they possess high resistivity and negligible eddy current losses. -

Ferrite EMI Cable Cores Electro-Magnetic Interference Solutions

global solutions : local support ™ Ferrite EMI Cable Cores Electro-Magnetic Interference Solutions www.lairdtech.com Laird Technologies is the world leader in the design and supply of customized performance critical products for wireless and other advanced electronic applications. Laird Technologies partners with it's customers to help find solutions for applications in various industries such as: Aerospace Automotive Electronics Computers Consumer Electronics Data Communications Medical Equipment Military Network Equipment Telecommunications Laird Technologies offers its customers unique product solutions, dedication to research and development and a seamless network of manufacturing and customer support facilities located all across the globe. global solutions : local support ™ www.lairdtech.com Contents Ferrite Material Impedance Comparison ................................. 4 Design & Selection “Rules of Thumb” ..................................... 4 High Frequency (HFB-) Cylindrical Cores .................................. 5 High Frequency (HFA-) Split, Snap-On Cores ........................... 6 Broadband (28B-) Cylindrical Cores ........................................ 7 Broadband (28A-) Split, Snap-On Cores ................................ 10 Sorted Quick Reference Charts Broadband (28B- and 28A-) Cable Cores .......................... 12 Low Frequency (LFB-) Cylinderical Cores ............................... 14 Broadband (28R-) Ribbon & Flex Cable Cores ....................... 15 Broadband (28S-) Split Ribbion & Flex Cable Cores -

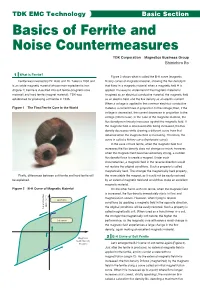

Basics of Ferrite and Noise Countermeasures TDK Corporation Magnetics Business Group Shinichiro Ito

TDK EMC Technology Basic Section Basics of Ferrite and Noise Countermeasures TDK Corporation Magnetics Business Group Shinichiro Ito What is Ferrite? 1 Figure 2 shows what is called the B-H curve (magnetic Ferrite was invented by Dr. Kato and Dr. Takei in 1930 and history curve) of magnetic material, showing the flux density B is an oxide magnetic material whose main ingredient is iron that flows in a magnetic material when a magnetic field H is (Figure 1) Ferrite is classified into soft ferrite (magnetic core applied. It is easy to understand if the magnetic material is material) and hard ferrite (magnet material). TDK was imagined as an electrical conductive material, the magnetic field established for producing soft ferrite in 1935. as an electric field, and the flux density as an electric current. When a voltage is applied to the common electrical conductive Figure 1 The First Ferrite Core in the World material, a current flows in proportion to the voltage; then, if the voltage is decreased, the current decreases in proportion to the voltage (Ohm’s Law). In the case of the magnetic material, the flux density non-linearly increases against the magnetic field. If the magnetic field is decreased after being increased, the flux density decreases while drawing a different curve from that obtained when the magnetic field is increasing. Therefore, the curve is called a history curve (hysteresis curve). In the case of hard ferrite, when the magnetic field first increases the flux density does not change so much, however, when the magnetic field becomes extremely strong, a sudden flux density flows to create a magnet. -

Ferrite Cores

Ferrite Cores Vol. 6 ●All specifications in this catalog and production status of products are subject to change without notice. Prior to the purchase, please contact TOKIN for updated product data. ●Please request for a specification sheet for detailed product data prior to the purchase. ●Before using the product in this catalog, please read "Precautions" and other safety precautions listed in the printed version catalog. 2017.04.14 9603FERVOL06E1212H1 CONTENTS Precautions Before Use ‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥ ‥ 3 Notes on Design ‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥ ‥ 3 Notes of Caution on Handling and Usage ‥ ‥‥‥‥‥‥‥‥‥‥‥ ‥ 4 Terms and Definitions ‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥ ‥ 5 High-B Compound Standard Material Characteristics ‥ ‥‥‥‥‥‥‥ ‥ 8 High-µ Compound Standard Material Characteristics ‥ ‥‥‥‥‥‥‥ ‥11 E Type Ferrite Cores FEI-Type Cores ‥ ‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥ ‥12 FEE-Type Cores ‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥ ‥13 FEER Type Ferrite Cores FEER-Type Cores ‥ ‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥ ‥15 FPQ Type Ferrite Cores FPQ-Type Cores ‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥ ‥16 FQK Type Ferrite Cores FQK-Type Cores ‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥ ‥17 FEP Type Ferrite Cores FEP-Type Cores ‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥ ‥18 P Type Ferrite Cores P-Type Cores ‥ ‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥ ‥19 RM Type Ferrite Cores RM-Type Cores ‥ ‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥ ‥20 Toroidal Cores ‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥ ‥21 BH2 Compound Technical Data ‥ ‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥‥ ‥23 Ferrite Cores VOL.06 2 ●All specifications in this catalog and production status of products are subject to change without notice. Prior to the purchase, please contact -

Magnetic Cores for Switching Power Supplies INTRODUCTION the Advantages of Switching Power Supplies (SPS) Are Well Documented

® Division of Spang & Company Magnetic Cores For Switching Power Supplies INTRODUCTION The advantages of switching power supplies (SPS) are well documented. Various circuits used in these units have also been sufficiently noted in literature. Magnetic cores play an important role in SPS circuitry. They are made from a variety of raw materials, a range of manufacturing processes, and are available in a variety of geometries and sizes as shown in Figure 1. Each material has its own unique properties. Therefore, the requirements for each applica- tion of a core in the power supply must be examined in light of the properties of available magnetic materials so that a proper core choice can be made. This article describes the various magnetic materials used for cores in switching power supplies, their method of manufacture, and useful magnetic characteristics as related to major sections of the power supply. Cores can be classified into three basic Figure 1: A Multitude of Magnetic Cores. types: (1) tape wound cores, (2) powder cores, and (3) ferrites. Additional core details on material descriptions and characteristics, plus sizes and spe- cific design information, are available in the following MAGNETICS sources: Ferrite Cores . Catalog FC-601 Molypermalloy and High Flux Powder Cores . Catalog MPP-400 KOOL MU Powder Cores . ............. Catalog KMC-2.0 High Flux Powder Cores . Catalog HF-PC-01 Tape Wound Cores . Catalog TWC-500 Cut Cores . .......... Catalog MCC- 100 Inductor Design Software for Powder Cores Common Mode Inductor Design Software INDEX Tape Wound Cores . 1 Powder Cores . 3 Ferrite Cores . 5 TAPE WOUND CORES Figure 2 shows a cutaway view of a typical tape wound core. -

Magnetic Properties of Bismuth Ferrite Nanopowder Obtained by Mechanochemical Synthesis I

Vol. 126 (2014) ACTA PHYSICA POLONICA A No. 4 Proc. of the International Conference on Mechanochemistry and Mechanical Alloying, Kraków, Poland, June 2226, 2014 Magnetic Properties of Bismuth Ferrite Nanopowder Obtained by Mechanochemical Synthesis I. Szafraniak-Wizaa;*, B. Andrzejewskib and B. Hilczerb aInstitute of Materials Science and Engineering, Pozna« University of Technology, pl. M. Skªodowskiej-Curie 5, 60-965 Pozna«, Poland bInstitute of Molecular Physics, PAS, M. Smoluchowskiego 17, 60-179 Pozna«, Poland Multiferroic bismuth ferrite (BiFeO3) nanopowders have been obtained at room temperature by mechanochem- ical synthesis. Depending on the post-synthesis processing the nanopowders exhibited dierences in the mean sizes, presence of amorphous layer and/or secondary phases. Extended magnetic study performed for fresh, annealed and hot-pressed nanopowders revealed substantial improvement of the magnetic properties in the as-prepared powder. DOI: 10.12693/APhysPolA.126.1029 PACS: 81.07.Bc, 81.07.Wx, 81.20.Ev, 75.85.+t 1. Introduction 2. Experimental Multiferroics exhibit at least two primary ferroic or- Bismuth ferrite nanopowder was synthesized by ders: ferroelectric, ferromagnetic, ferroelastic or ferrotor- mechanochemical route. Details of synthesis were pub- roic in a single homogeneous phase and the order param- lished in previous paper [7]. Commercially available ox- eters can be mutually coupled [1]. Especially interest- ides (Bi2O3 and Fe2O3 purchased from Aldrich, 99% pu- ing are ferroelectromagnets (or magnetoelectric multifer- rity) in stoichiometric ratio were milled in a SPEX 8000 roics) having magnetization and dielectric polarization, Mixer Mill for 120 h. The thermal treatment was per- which can be modulated and activated by an external formed for 1 h in air atmosphere under atmospheric pres- electric eld and magnetic eld, respectively. -

Making Core Memory: Design Inquiry Into Gendered Legacies of Engineering and Craftwork Daniela K

Making Core Memory: Design Inquiry into Gendered Legacies of Engineering and Craftwork Daniela K. Rosner1, Samantha Shorey2, Brock Craft1, Helen Remick3 1Dept. of HCDE 2Dept. of Communication 3Seattle, WA University of Washington University of Washington [email protected] Seattle, WA Seattle, WA {dkrosner, bcraft}@uw.edu [email protected] ABSTRACT This paper describes the Making Core Memory project, a design inquiry into the invisible work that went into assem- bling core memory, an early form of computer information storage initially woven by hand. Drawing on feminist tradi- tions of situated knowing, we designed an electronic quilt and a series of participatory workshops that materialize the work of the core memory weavers. With this case we not only broaden dominant stories of design, but we also reflect on the entanglement of predominantly male, high status labor with the ostensibly low-status work of women’s hands. By integrating design and archival research as a means of cultural analysis, we further expand conversations on design research methods within human-computer inter- action (HCI), using design to reveal legacies of practice Figure 1: Close up view of the Core Memory Quilt. elided by contemporary technology cultures. In doing so, this paper highlights for HCI scholars that worlds of hand- broadened, too. From establishing the Jacquard loom as a work and computing, or weaving and space travel, are not precursor to the Babbage Analytical Engine [66] to re- as separate as we might imagine them to be. calling that the first “computers” were young women [11,19,31,40], gendered narratives of craftwork and engi- Author Keywords neering both haunt and inform HCI’s ideas of technological Woven memory; gendered labor; craft; handwork; compu- belonging, participation, and differentiation [44].