Digital Signal Processing Laboratory Equipment

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

The Computer History Simulation Project

The Computer History Simulation Project The Computer History Simulation Project The Computer History Simulation Project is a loose Internet-based collective of people interested in restoring historically significant computer hardware and software systems by simulation. The goal of the project is to create highly portable system simulators and to publish them as freeware on the Internet, with freely available copies of significant or representative software. Simulators SIMH is a highly portable, multi-system simulator. ● Download the latest sources for SIMH (V3.5-1 updated 15-Oct-2005 - see change log). ● Download a zip file containing Windows executables for all the SIMH simulators. The VAX and PDP-11 are compiled without Ethernet support. Versions with Ethernet support are available here. If you download the executables, you should download the source archive as well, as it contains the documentation and other supporting files. ● If your host system is Alpha/VMS, and you want Ethernet support, you need to download the VMS Pcap library and execlet here. SIMH implements simulators for: ● Data General Nova, Eclipse ● Digital Equipment Corporation PDP-1, PDP-4, PDP-7, PDP-8, PDP-9, PDP-10, PDP-11, PDP- 15, VAX ● GRI Corporation GRI-909 ● IBM 1401, 1620, 1130, System 3 ● Interdata (Perkin-Elmer) 16b and 32b systems ● Hewlett-Packard 2116, 2100, 21MX ● Honeywell H316/H516 ● MITS Altair 8800, with both 8080 and Z80 ● Royal-Mcbee LGP-30, LGP-21 ● Scientific Data Systems SDS 940 Also available is a collection of tools for manipulating simulator file formats and for cross- assembling code for the PDP-1, PDP-7, PDP-8, and PDP-11. -

MINICOMPUTER CONCEPTS by BENEDICTO CACHO Bachelor Of

MINICOMPUTER CONCEPTS By BENEDICTO CACHO II Bachelor of Science Southeastern Oklahoma State University Durant, Oklahoma 1973 Submitted to the Faculty of the Graduate College of the Oklahoma State University in partial fulfillment of the requirements for the Degre~ of MASTER OF SCIENCE July, 1976 . -<~ .i;:·~.~~·:-.~?. '; . .- ·~"' . ~ ' .. .• . ~ . .. ' . ,. , .. J:. MINICOMPUTER CONCEPTS Thesis Approved: fl. F. w. m wd/ I"'' ') 2 I"' e.: 9 tl d I a i. i PREFACE This thesis presents a study of concepts used in the design of minicomputers currently on the market. The material is drawn from research on sixteen minicomputer systems. I would like to thank my major adviser, Dr. Donald D. Fisher, for his advice, guidance, and encouragement, and other committee members, Dr. George E. Hedrick and Dr. James Van Doren, for their suggestions and assistance. Thanks are also due to my typist, Sherry Rodgers, for putting up with my illegible rough draft and the excessive number of figures, and to Dr. Bill Grimes and Dr. Doyle Bostic for prodding me on. Finally, I would like to thank members of my family for seeing me through it a 11 . iii TABLE OF CONTENTS Chapter Page I. INTRODUCTION 1 Objective ....... 1 History of Minicomputers 2 II. ELEMENTS OF MINICOMPUTER DESIGN 6 Introduction 6 The Processor . 8 Organization 8 Operations . 12 The Memory . 20 Input/Output Elements . 21 Device Controllers .. 21 I/0 Operations . 22 III. GENERAL SYSTEM DESIGNS ... 25 Considerations ..... 25 General Processor Designs . 25 Fixed Purpose Register Design 26 General Purpose Register Design 29 Multi-accumulator Design 31 Microprogramm1ng 34 Stack Structures 37 Bus Structures . 39 Typical System Options 41 IV. -

Oral History of Gary Davidian, Part 1 of 2

Oral History of Gary Davidian, part 1 of 2 Interviewed by: Hansen Hsu Recorded February 5, 2019 Mountain View, CA CHM Reference number: X8931.2019 © 2019 Computer History Museum Oral History of Gary Davidian Hsu: It is February 5th, 2019. I am Hansen Hsu here with Gary Davidian. Welcome. Davidian: Hello. Hsu: So let’s start with where and when were you born. Davidian: I was born in 1956 in New York City. And my parents were also born in New York City. Hsu: And so is that where you grew up? Davidian: I grew up-- yes. I was actually born in Manhattan but grew up in Queens. Hsu: And what’s your ethnic background? Davidian: Armenian. Both my parents were Armenian. So I grew up in an Armenian household. Hsu: What did your parents do? Davidian: My father was a mechanical engineer and he worked for-- well, while I was growing up, mostly he worked for Sperry Gyroscope in Great Neck, New York. And my mother, while I was growing up, was just a-- a housewife, but, you know, she had-- she had worked before marriage and then later when I was in college she was-- she was working again. Hsu: Do you have any siblings? Davidian: Yes. There are four of us. I have an older sister. I’m second. I have a younger brother, and then the youngest is my youngest sister. Hsu: Did you have any hobbies growing up? Davidian: Well, there were-- there were actually some things that-- when I was growing up-- which were sort of my favorite toys. -

A Large Hospital Laboratory in Singapore

Journal of Automatic Chemistry, Vol. 14, No. 6 (November-December 1992), pp. 223-229 Integrated laboratory information system in a large hospital laboratory in Singapore Edward Jacob, It-Koon Tan, Kim-Seng Chua and minicomputer running on Medical Information tech- See-Heng Lim nology (Meditech) Software written in Meditech Inter- Clinical Biockemistry Laboratories, Department of Pathology, Singapore General pretive Information System (MIIS). Two identical on- Hospital, Outram Road, Singapore 0316, Singapore line systems were purchased, one in 1983 to serve the haematology laboratories and the 24-hour emergency/ This describes an to the computerization paper integrated approach routine biochemistry laboratories sited on the same floor all medicine and of major disciplines of laboratory pathology. within and another in to serve the main Installed the General SGH, 1984, in Department of Pathology, Singapore biochemistry laboratories of the Department of Pathology Hospital the computer system discussed comprises a (SGH), which is housed in a separate building some distance RISC-based Data General Aviion 6200 computer and Meditech away. The other laboratories at SGH were not ready for MAGIC The has been with the software. system interfaced computerization. hospital host IBM computer and supports patient information result management, and compila- transfer, reporting, phlebotomy The annual number of tests in the biochemistry and tion and The main of laboratory financial management reports. haematology departments was 820000 and 700000, the include: on-line and acquisition functions of system off-line of respectively, when the two computer systems were patient and test data; single information preparation of The systems were linked modems cumulative within and between purchased. -

General Disclaimer One Or More of the Following Statements May Affect

General Disclaimer One or more of the Following Statements may affect this Document This document has been reproduced from the best copy furnished by the organizational source. It is being released in the interest of making available as much information as possible. This document may contain data, which exceeds the sheet parameters. It was furnished in this condition by the organizational source and is the best copy available. This document may contain tone-on-tone or color graphs, charts and/or pictures, which have been reproduced in black and white. This document is paginated as submitted by the original source. Portions of this document are not fully legible due to the historical nature of some of the material. However, it is the best reproduction available from the original submission. Produced by the NASA Center for Aerospace Information (CASI) " GAO .k INVESTIGATION OE 1 ^ . DISK SYSTEMS '4c: (iVASA-CE-150165) INVESTIGATION OF SELECTED N77-15669 { DISK SYSTEMS (Tcieayn e grown Engineering) c 32 p hC A03 /MF A01 CSCL 09B Uilcias G3/60 12513 !`y Iris ^ eYt Octobe r 197 ti p: INVESTIGATION OF SELECTED DISK SYSTEMS APF76-MSFC-02222 October, 1976 Prepared For Data Systems Laboratory George C. Marshall Space Flight Center Huntsville, Alabama Prepared Under Contract No. NAS8-31488 By Advanced Projects Division Teledyne Brown Engineering Huntsville, Alabama t l ABSTRACT This report examines the large disk systems offered by IBM, UNIVAC, Digital Equipment Corporation, and Data General. In particular, these disk systems are analyzed in terms of how will available operating systems take advantage of the respective disk controller's transfer rates, and to what degree all available data for optimizing disk usage is effectively employed. -

Company Private

a by Ray Smelek/Boise I am pleased to announce Bill Murph Boise Division as Marketing Man extensive marketing experience at • Bill will be moving to Boise in early January; in the meantime, will be formulating marketing strategy for Boise products while he phases out of his current position. HEwLEn~pAcKARD BOISE DIVISION NEWS by Ray SmeleklBoise I know there is considerable concern in the field regarding the long availability on 7970 Magnetic Tape Drives. First I want to assure you that everyone in Boise is equally concerned and striving hard to red~~ceit. Before I elaborate on what we are doing to rectify the situation I want to fill you in on hat lead us to this predicament. Many people feel this transfer asf Mag Tapes from Mountain View to Boise was untimely and poorly planned. Well, in looking back one Isan always see ways of doing things better, but by and large the transfer came off very smoothly. What we did not anticipate was the sudden demand on Tape Drive deliveries. You people in the field did an outstanding job in signing OEM's during the summer. The order rate in August, September, and October has been over 200% of a customers supplied with units. (Conrinued on page 2) All prices quoted in this Newsletter are domestic USA prices only I Company Private BOISE DIVISION NEWS - (Continued from page 1) work our way out of this long availability situation and still maintain good relationships with our customers overtime and have several people on loan in Bo~sewho are spending full time expediting material to ensure the I expect our availability to be down to 8-10 weeks by pull-ups occur on time. -

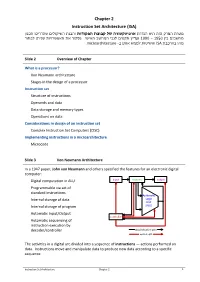

Chapter 2 Instruction Set Architecture (ISA)

Chapter 2 Instruction Set Architecture (ISA) מטרת הפרק הזה היא הגדרת ארכיטקטורה של קבוצת הפקודות והבנת השיקולים שהדריכו תכנון מחשבים בין 1950 – 1990 ועדיין תקפים לגבי המחשב האישי. נסקור את האפשרויות שניתן לבחור מהן בהרכבת ISA והשיטות לממש אותן ב- microarchitecture. Slide 2 Overview of Chapter What is a processor? Von Neumann architecture Stages in the design of a processor Instruction set Structure of instructions Operands and data Data storage and memory types Operations on data Considerations in design of an instruction set Complex Instruction Set Computers (CISC) Implementing instructions in a microarchitecture Microcode Slide 3 Von Neumann Architecture In a 1947 paper, John von Neumann and others specified the features for an electronic digital computer: Digital computation in ALU input memory output Programmable via set of standard instructions Arithmetic Internal storage of data Logic Unit Internal storage of program (ALU) Automatic Input/Output controller Automatic sequencing of instruction execution by decoder/controller data/instruction path control path The activities in a digital are divided into a sequence of instructions — actions performed on data. Instructions move and manipulate data to produce new data according to a specific sequence. Instruction Set Architecture Chapter 2 1 Slide 4 Stages in Computer Design Instruction Set Architecture (ISA) The design of a computer begins with the specification of the ISA: 1. Look at the universe of problems to be solved and define the desired capabilities 2. Define a set of atomic operations at level of a system programmer (assembly language) A set of small and orthogonal operations (each performs different task) Instructions in the set can be combined to perform any desired operation 3. -

General Disclaimer One Or More of the Following Statements May Affect

General Disclaimer One or more of the Following Statements may affect this Document This document has been reproduced from the best copy furnished by the organizational source. It is being released in the interest of making available as much information as possible. This document may contain data, which exceeds the sheet parameters. It was furnished in this condition by the organizational source and is the best copy available. This document may contain tone-on-tone or color graphs, charts and/or pictures, which have been reproduced in black and white. This document is paginated as submitted by the original source. Portions of this document are not fully legible due to the historical nature of some of the material. However, it is the best reproduction available from the original submission. Produced by the NASA Center for Aerospace Information (CASI) a S077•MSFC 1r;A^ Nr V 1+. Technical Report SURVEY: AUTOMATED FIELD OPERATIONS AND SERVICES (AFOS) (NASA-CR-150548) S g RVEY; AUTOMATED FIELD '178-11301 OPERATIONS AND SERVICES (APOS) (Teledyne Drown Enqineerinq) 36 p Fir A03/.,-IF 401 CSCL 17?1 Uncla.; G3/32 05929 November 1977 a ^^ I{ OJ ^ >' r"«1i3 ^9rr^ 07"T ELEDYNE BROWN ENGINEERING Cummings Research Park- Huntsville, Alabama 35807 ^' T TECHNICAL REPORT SD77-MSFC-2150 SURVEY: AUTOMATED FIELD OPERATIONS AND SERVICES (AFOS) Prepared For 3e DATA SYSTEMS LABORATORY MARSHALL SPACE FLIGHT CENTER NATIONAL AERONAUTICS AND SPACE ADMINISTRATION HUNTSVILLE, ALABAMA Contract No. NAS" j2539 APPROVED: O. P Ely Project Director TABLE OF CONTENTS Page 1. SPACE DATA GENERATOR ELEMENTS (Not Applicable) . 1-1 2. SPACE DATA PROCESSING ELEMENTS (Not Applicable) . -

Software Implementation a Image Display System 511

SOFTWARE IMPLEMENTATION A IMAGE DISPLAY SYSTEM 511 Mark Gross (Water Resource Analyst - Department of Water Resources - Remote Sensing Unit - Boise, ID) If you should venture to Idaho, and find yourself at the Idaho Depart- ment of Water Resources (IDWR), Remote Sensing Unit, you stand a good chance of hearing one of our senior management personnel say "you now only have to press the button, and presto, displayed in living color, an image that formerly took weeks to hand color."^ This is the current v z introduction to International Imaging System s (I S), display device and software that a visitor at our site will receive. It is with pleasure, that I would like to relate to you some of our experiences with bringing System 511 on line at IDWR. Certainly our joys and suf- fering bear sharing with those who may be considering embarking on a similar endeavor. Functionally, System 500 is the software package designed to drive 12S's Model 70 digital display device. System 500, according to 12S, is fully supported on 3 minicomputer systems. System 501 is based on the Hewlett- Packard I000, System 520 on the Data General Eclipse. System 511, to which all further comments shall be addressed, is the 12S version of System 500 designed to run on a Digital Equipment Corporation (DEC) PDP 11 Series minicomputer. It is fully compatible with the DEC opera- ting system as delivered. According to the manufacture's specifications, the minimum system hardware configuration is an 11/34 with a minimum core of 128K word, I0 megabytes of direct access disk and a floating point processor.