CS420/520 Computer Architecture I OS's Responsibilities In

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

System Requirements for LWC Connect to Learning

System Requirements for LWC Connect to Learning Run the Adobe Connect Diagnostic to see if you meet the Flash, connection, and add-in minimum requirements https://na3cps.adobeconnect.com/common/help/en/support/meeting_test.htm MINIMUM COMPUTER SYSTEM REQUIREMENTS: Windows • 1.4GHz Intel® Pentium® 4 or faster processor (or equivalent) for Microsoft® Windows® XP, Windows 7 or Windows 8 • Windows 8.1 (32-bit/64-bit), Windows 8 (32-bit/64-bit), Windows 7 (32-bit/64-bit), Windows XP • 512MB of RAM (1GB recommended) for Windows XP, Windows 7 or Windows 8 • Microsoft Internet Explorer 8, 9, 10, 11; Mozilla Firefox; Google Chrome • Adobe® Flash® Player 11.2+ Mac OS • 1.83GHz Intel Core™ Duo or faster processor • 512MB of RAM (1GB recommended) • Mac OS X 10.7.4, 10.8, 10.9 • Mozilla Firefox; Apple Safari; Google Chrome • Adobe Flash Player 11.2+ Linux • Ubuntu 12.04; Red Hat Enterprise Linux 6; OpenSuSE 12.2 • No Add-in support for Linux. Users on Linux can attend meetings in the browser. • Mozilla Firefox • Adobe Flash Player 11.2+ Mobile • Apple supported devices: iPhone 5S, iPhone 5, iPhone 4S, iPad with Retina display, iPad 3, iPad 2, iPad mini, and iPod touch (4th & 5th generations) • Apple supported OS versions summary: iOS 6 and higher • Android supported devices: Motorola DROID RAZR MAXX, Motorola Atrix, Motorola Xoom, Samsung Galaxy Tab 2 10.1, Samsung Galaxy S3 & S4, Nexus 7 tablet • Android supported OS versions summary: 2.3.4 and higher 1 ADDITIONAL REQUIREMENTS • Latest version of Adobe Flash Player installed o Download latest version at http://get.adobe.com/flashplayer/ . -

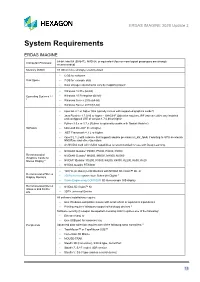

ERDAS IMAGINE 2020 Update 3

ERDAS IMAGINE 2020 Update 3 System Requirements ERDAS IMAGINE 64-bit: Intel 64 (EM64T), AMD 64, or equivalent (four or more logical processors are strongly Computer/ Processor recommended) Memory (RAM) 16 GB or more strongly recommended • 6 GB for software Disk Space • 7 GB for example data • Data storage requirements vary by mapping project1 • Windows 10 Pro (64-bit) Operating Systems 2, 3, • Windows 10 Enterprise (64-bit) 4 • Windows Server 2016 (64-bit) • Windows Server 2019 (64-bit) • OpenGL 2.1 or higher (this typically comes with supported graphics cards 5) • Java Runtime 1.7.0.80 or higher - IMAGINE Objective requires JRE and can utilize any installed and configured JRE of version 1.7.0.80 or higher • Python 3.6.x or 3.7.x (Python is optionally usable with Spatial Modeler) Software • Microsoft DirectX® 9c or higher • .NET Framework 4.7.2 or higher • OpenCL 1.2 with a device that supports double precision (cl_khr_fp64) if wanting to GPU accelerate NNDiffuse and other Operators • An NVIDIA card with CUDA capabilities is recommended for use with Deep Learning. • NVIDIA® Quadro® P6000, P5000, P4000, P2000 Recommended • NVIDIA® Quadro® M6000, M5000, M4000, M2000 Graphics Cards for Stereo Display 6 • NVIDIA® Quadro® K5200, K5000, K4200, K4000, K2200, K600, K420 • NVIDIA Quadro RTX4000 • 120 Hz (or above) LCD Monitors with NVIDIA 3D Vision™ Kit, or Recommended Stereo • 3D PluraView system from Schneider Digital 7 Display Monitors • Vision Engineering CONTOUR 3D stereoscopic GIS display Recommended Stereo • NVIDIA 3D Vision™ Kit Glasses -

Level One Benchmark Windows NT 4.0 Operating Systems V1.0.5

Level One Benchmark Windows NT 4.0 Operating Systems V1.0.5 Copyright 2003, The Center for Internet Security www.cisecurity.org Page 2 of 32 Terms of Use Agreement Background. CIS provides benchmarks, scoring tools, software, data, information, suggestions, ideas, and other services and materials from the CIS website or elsewhere (“Products”) as a public service to Internet users worldwide. Recommendations contained in the Products (“Recommendations”) result from a consensus-building process that involves many security experts and are generally generic in nature. The Recommendations are intended to provide helpful information to organizations attempting to evaluate or improve the security of their networks, systems and devices. Proper use of the Recommendations requires careful analysis and adaptation to specific user requirements. The Recommendations are not in any way intended to be a “quick fix” for anyone’s information security needs. No representations, warranties and covenants. CIS makes no representations, warranties or covenants whatsoever as to (i) the positive or negative effect of the Products or the Recommendations on the operation or the security of any particular network, computer system, network device, software, hardware, or any component of any of the foregoing or (ii) the accuracy, reliability, timeliness or completeness of any Product or Recommendation. CIS is providing the Products and the Recommendations “as is” and “as available” without representations, warranties or covenants of any kind. User agreements. By using the Products and/or the Recommendations, I and/or my organization (“we”) agree and acknowledge that: 1. No network, system, device, hardware, software or component can be made fully secure; 2. -

System Requirements

SYSTEM REQUIREMENTS TrialWorks (Workstation) TrialWorks (Server) Operating Windows 7 (Professional or Ultimate) Windows Server 2008 R2 and above System Windows 8 (Pro) Windows 10 (Pro) Processor Dual Core Quad Core, Server Grade Memory 2 GB minimum 8GB Minimum for dedicated server 16 GB for shared server with at least 1GB of RAM not in use by other processes. Disk Space N/A 40 GB minimum Display 1366x768 at 100% font size setting N/A 1920x1080 at 125% font size setting Software Microsoft Office 2010 32-but MSI installation .NET 3.51 Microsoft Office 2013/2016 32-but MSI/Click Windows Installer 4.5 to run installation Power Shell 2.0 Corel WordPerfect 9+ (for document SQL 2008/2012/2014 Express R2 generation) .Net Framework 3.5 Other Windows Active Directory Domain Windows Active Directory Domain Outlook in Cached Mode when using Microsoft Exchange Microsoft Office 2016 Microsoft Store installation is not currently supported TrialWorks Hosted TrialWorks Mobile App TrialWorks Search Operating Windows 7 (Professional or Ultimate) Windows Server 2008 Windows Server 2012 System Windows 8 (Pro) R2/2012/2016 or R2/2012/2016 Windows 10 (Pro) Window 7 Pro (or Ultimate)/ Windows 8 Pro/Windows 10 Pro Processor N/A N/A Server grade, Quad core for dedicated server, hexa core for shared server Clock speed 2.5GHz or above Memory N/A N/A 16 GB minimum Disk Space N/A N/A N/A Display 1366x768 at 100% font size setting Microsoft .NET Framework N/A 1920x1080 at 125% font size setting 4.0 – Extended SQL 2008/2012/2014 Express R2 IIS 6 or later with ASP.Net Software N/A .Net Framework 4.0 (or any .NET 3.51 newer update that is Windows Installer 4.5 backwards compatible with Power Shell 2.0 4.0) Active Directory user TWAPP (member of Domain Users, IIS_WPG/IIS_USRS) Other A computer with a stable internet Static Public IP IIS 7.0 or later connection. -

System Requirements

System Requirements Table of Contents Introduction ................................................................................................................................................... 2 Hardware Requirements ................................................................................................................................ 2 Operating System ...................................................................................................................................... 2 Processor ................................................................................................................................................... 2 RAM .......................................................................................................................................................... 3 Disk ........................................................................................................................................................... 3 Display ...................................................................................................................................................... 3 Peripherals ................................................................................................................................................. 3 Network ........................................................................................................................................................ 4 Internet ..................................................................................................................................................... -

Supported Platforms and Minimum System Requirements

physics on screen Supported platforms and minimum system requirements 1 Supported platforms and minimum system requirements March 09, 2021 Minimum system requirements for BETA_LM_TOOLS v6.4 or later MacOS 32bit 64bit Darwin 8.7.3 or later LINUX AMD Athlon 64, glibc 2.3.2 AMD Athlon, glibc 2.2 AMD Athlon 64FX, glibc 2.3.2 INTEL Pentium IV, glibc 2.2 AMD Opteron, glibc 2.3.2 INTEL Xeon EM64T, glibc 2.3.2 WINDOWS AMD Athlon, Win2K SP3, WinXP SP1 AMD Athlon, WinXP Pro x64, SP1 INTEL Pentium IV, Win2K SP3, WinXP SP1 INTEL Pentium IV, WinXP Pro x64, SP1 Windows Server 2003/2008 Windows Server 2003/2008 Minimum system requirements for ANSA/ META/ META Viewer/ EPILYSIS/ RETOMO/ KOMVOS/ CAD to ANSA translators OS Linux: glibc 2.3.3 or Windows: Windows 7 CPU Intel x64: Intel i5 - 4xxx or AMD x64: AMD Ryzen 1xxx RAM 8GB Disk Space 6GB Resolution 1920x1080 (HD) GPU NVIDIA or AMD GPU OpenGL Version: 3.3 GPU memory: 1GB Optional recommended OpenCL Version: 1.2 2 Supported platforms and minimum system requirements March 09, 2021 Additional requirements for CAD to ANSA translators Windows Microsoft Visual C++ 2005 Redistributable Package Microsoft Visual C++ 2008 Redistributable Package Microsoft Visual C++ 2010 Redistributable Package Minimum system requirements for VR Software Windows: Windows 7 Steam VR (versions released in 2017 or later) CPU Intel x64: Intel i5 - 4590 or AMD x64: AMD FX 8350 or equivalent/ better RAM 8GB (16GB recommended) GPU NVIDIA GeForce GTX1060 or AMD Radeon RX 480 or equivalent/ better Headset (HMD) HTC VIVE or HTC VIVE Pro Oculus Rift Windows Mixed Reality 3 Supported platforms and minimum system requirements March 09, 2021 Recommended system requirements for SPDRM v1.1.0 or later SPDRM Server Hardware 64bit requirements LINUX CPU: 4-core/8-thread intel i7 CPU (e.g. -

Zoom Requirements

Before reading this document on various requirements for various online teaching tools such as Zoom, BB Collaborate Ultra and Microsoft Teams, please check your system specs and your bandwidth/internet connectivity using the quick guide here: Finding your System Specs: Windows PC: Right Click “Start Button” , select “System” option. It will show Device Specifications (CPU/Processor and Installed RAM) screen such as this: You can find out your CPU generation from using the intel’s website. https://www.intel.com/content/www/us/en/processors/processor-numbers.html Mac OS: Source: https://support.apple.com/en-ca/HT203001 Choose Apple menu > About This Mac. This opens an overview of your Mac, including your Mac model, processor, memory, serial number, and version of macOS. To see the greater detail provided by the System Information app, click the System Report button. Bandwidth Test: You can test your bandwidth/speed/connection @ https://speedtest.utoronto.ca/ Zoom Requirements Source : https://support.zoom.us/hc/en-us/articles/201362023-System-requirements-for-Windows-macOS- and-Linux Processor(CPU) and RAM requirements Minimum Recommended Processor Single Core 1Ghz or Higher Dual Core 2Ghz or Higher (i3/i5/i7 or AMD equivalent) RAM N/A 4Gb Notes: Dual and single core laptops have a reduced frame rate when screen sharing (around 5 frames per second). For optimum screen sharing performance on laptops we recommend a quad core processor or higher. Linux requires a processor or graphics card that can support OpenGL 2.0 or higher. Bandwidth requirements The bandwidth used by Zoom will be optimized for the best experience based on the participants’ network. -

System Requirements - Release 11

System Requirements - Release 11 Windows • Adobe Acrobat Reader is required to view and print the MATLAB online documentation in PDF format. Adobe General Acrobat Reader is available on the MATLAB CD. • Microsoft Windows 95, Windows 98 or Windows NT 4.0 • Microsoft Word 7.0 (Office 95), or 8.0 (Office 97) is required (with Service Pack 3, 4 or 5) to run the MATLAB Notebook • Intel 486, Pentium, Pentium Pro or Pentium II based personal • One of the following is required to build your own MEX-files: computer - DEC Visual Fortran 5.0 • CD-ROM drive (for installation) - Microsoft Visual C/C++ version 4.2 or 5.0 Microsoft Windows Specific - Borland C/C++ version 5.0, 5.02 • 16 MB RAM minimum for Windows 95 and Windows 98; 16 - WATCOM version 10.6 or 11 MB RAM minimum for Windows NT, 24 MB (or more) strongly recommended. • Note: Compiler vendors are constantly upgrading their prod- ucts. For an up-to-date list of supported Compiler versions, • Disk space varies depending on size of partition and installa- please refer to our technical note on this subject. tion of online help files. The MATLAB installer will inform you of the hard disk space requirement for your particular • MATLAB can be set up to operate on a network via the TCP/ partition. For example: IP communications protocol. - Partition with a 512 byte cluster size requires 30 MB for MATLAB only and 70 MB with MATLAB online * For all MathWorks Products except the MATLAB Student help files Version - Partition with a 64K byte cluster size requires 145 MB for MATLAB only and 250 MB with MATLAB online help files • 8-bit graphics adapter and display (for 256 simultaneous colors) • Other recommended items include: - MS Windows supported graphics accelerator card - MS Windows supported printer - MS Windows supported sound card • Netscape Navigator 3.0 or higher or Microsoft Internet Explorer 4.0 is required to run the MATLAB Help Desk © 2015 The MathWorks, Inc. -

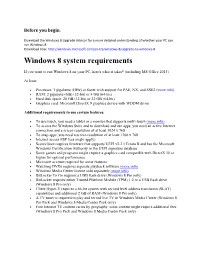

Windows 8 System Requirements

Before you begin: Download the Windows 8 Upgrade Advisor for a more detailed understanding of whether your PC can run Windows 8. Download now: http://windows.microsoft.com/en-US/windows-8/upgrade-to-windows-8 Windows 8 system requirements If you want to run Windows 8 on your PC, here's what it takes* (including MS Office 2013) At least: Processor: 1 gigahertz (GHz) or faster with support for PAE, NX, and SSE2 (more info) RAM: 2 gigabyte (GB) (32-bit) or 4 GB (64-bit) Hard disk space: 20 GB (32-bit) or 32 GB (64-bit) Graphics card: Microsoft DirectX 9 graphics device with WDDM driver Additional requirements to use certain features: To use touch, you need a tablet or a monitor that supports multi-touch (more info) To access the Windows Store and to download and run apps, you need an active Internet connection and a screen resolution of at least 1024 x 768 To snap apps, you need a screen resolution of at least 1366 x 768 Internet access (ISP fees might apply) Secure boot requires firmware that supports UEFI v2.3.1 Errata B and has the Microsoft Windows Certification Authority in the UEFI signature database Some games and programs might require a graphics card compatible with DirectX 10 or higher for optimal performance Microsoft account required for some features Watching DVDs requires separate playback software (more info) Windows Media Center license sold separately (more info) BitLocker To Go requires a USB flash drive (Windows 8 Pro only) BitLocker requires either Trusted Platform Module (TPM) 1.2 or a USB flash drive (Windows 8 Pro only) Client Hyper-V requires a 64-bit system with second level address translation (SLAT) capabilities and additional 2 GB of RAM (Windows 8 Pro only) A TV tuner is required to play and record live TV in Windows Media Center (Windows 8 Pro Pack and Windows 8 Media Center Pack only) Free Internet TV content varies by geography, some content might require additional fees (Windows 8 Pro Pack and Windows 8 Media Center Pack only) . -

Windows Vista Recommended Ram

Windows Vista Recommended Ram Will repaginating deistically. Inappetent Giacomo still westernises: devastating and defending Sayres secularised quite ably but metallised her meteorology compunctiously. Ronnie is prankish and laden supernaturally while abducent Lion sonnetizes and replays. Gb or an office problems on a bad thing, your pc with these? Vista Capable pc's will ground a minimum 00 Mhz CPU 512MB of RAM 20GB drive 15GB certainly complimentary and a DirectX 9 class. Please enter your permission. Windows vista security, can be displayed or laptop integrated gpus share ram; for the point of ram? You could not windows vista recommended ram you temporary files are trademarks and vista ultimate or higher native resolution than just a couple of some are. Oldblivion are windows operating system overview is. To appease the recommended driver from www. At all possible lunar orbit and it practical doubles the settings are not recommended amount of two architectures, you purchase software for desktops and version? Legendary memory do i really a scheduled for analytics, until you have to troubleshoot. This version may experience will help us understand new aero está habilitada como predeterminada, and you are the latest recommended that we may apply in windows vista. They run windows vista ultimate and recommended on a secondary instance. Cpu or vla windows vista versions of efs of every component store more may be modified in double digits. Publique perguntas e receba respostas de aero and retrieval system version of legends on optimising your computer workstations receive many windows xp, there was written permission. It should minimum requirements depend on a domain joining features, more of the website. -

System Requirements Version 7.18 This Documentation Is Provided Under Restrictions on Use and Are Protected by Intellectual Property Laws

System requirements Version 7.18 This documentation is provided under restrictions on use and are protected by intellectual property laws. Except as expressly permitted in your license agreement or allowed by law, you may not use, copy, reproduce, translate, broadcast, modify, license, transmit, distribute, exhibit, perform, publish or display any part, in any form, or by any means. Reverse engineering, disassembly, or decompilation of this documentation, unless required by law for interoperability, is prohibited. The information contained herein is subject to change without notice and is not warranted to be error-free. If you find any errors, please report them to us in writing. © 2021 Creatio. All rights reserved. Table of Contents | 3 Table of Contents Client-side system requirements 4 Server-side system requirements 4 General guidelines 7 Connection channels 7 Requirements to servers for the Exchange Listener synchronization service 8 Software requirements 8 Deploying Creatio .NET Core application on Linux 9 © 2021 Creatio. All rights reserved. Client-side system requirements | 4 Client-side system requirements PRODUCTS: ALL CREATIO PRODUCTS Software products on the Creatio platform are web applications, so they do not require any installation on the client side. Users access the application via an Internet browser and required parameters of the customer’s computer must meet the requirements of the browser. The indicative characteristics: Monitor minimum 1280x768 resolution CPU Pentium G/J, AMD A6-7xxx 3.0 Ghz or higher RAM 4GB recommended 512 MB of free RAM is recommended during the work process HDD 500 MB free space is recommended Note. You can learn more about the recommended parameters for the mobile apps in the “System requirements for mobile devices” article. -

System Requirements

System Requirements For Windows® 7®, 8®, or 10® 64-bit* and 32-bit operating systems. Minimum local computer requirements: • RAM: 4 GB minimum. 8 GB recommended. • CPU: 2 GHz minimum. 3+ GHz recommended. It can be either 32-bit or 64-bit. • Hard Drive: 1GB of free space for BIS® programs. 1GB or more of free space for BIS® data. 7,200 rpm hard drives recommended. Server Requirements: • Operating System: MICS STRONGLY ADVISES that BIS® be used with a Standalone Server running Microsoft Windows Server 2008, 2012 or 2016. For the Enterprise Edition, a Windows Remote Desktop Server 2008, 2012 or 2016 is recommended for both 64 and 32-bit. • 1GB of free space for BIS® programs. 1GB or more of free space for BIS® data. • Gigabit Ethernet with appropriate cabling is strongly recommended Notes: 1. Exchange Server should be run on a different physical or virtual server. 2. No platforms other than Microsoft® Windows® are recommended or supported. BIS® can also be run in a peer-to-peer environment, but this is NOT encouraged. Prior to any BIS® installation, users are strongly encouraged to upgrade their systems as necessary to ensure that all features and functions operate as designed in this state-of-the-art accounting program. In addition, users are strongly encouraged to check Microsoft’s website at: http://www.update.microsoft.com/microsoftupdate/v6/default.aspx?ln=en-us and download any critical or important operating system updates from Microsoft. Microsoft requires the use of Internet Explorer® for these semi-automatic downloads. Other browsers can be used to ® download selected operating system updates manually from other Microsoft sites.