Very High Frequency Bipolar Junction Transistor Frequency Multiplier Drive Network Design and Analysis

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Crystal Oscillators 1

Crystal oscillators 1. Objectives The aim of the exercise is to get acquainted with issues concerning the generation of waveforms (including sinewaves) in the basic structures of crystal generators. In addition, the exercise aims to familiarize with surface mount technique SMT (Surface Mount Technology/ Technics or SMD – Surface mounting Devices). 2. Components and instrumentation. In the exercise, it is possible to test quartz generators operating in the three simplest and most popular system structures: • Colpitts-Pierce quartz generator with bipolar transistor, • quartz generator implemented on TTL gates, • quartz generator implemented on CMOS inverters 2.1. Colpittsa-Pierce’s oscillator with bipolar transistor. The Colpitts-Pierce quartz generator system working in parallel resonance is shown in Fig. 1. + UCC Rb C2 XT C1 Re UWY Fig. 1. Colpittsa-Pierce oscillator with BJT. Using, in the system, quartz resonators with resonance values up to several tens of MHz, the elements C1, Re in the generator system can be selected according to the graph shown in Fig.2. RezystorRe [Ohm] Frequency [MHz] Fig. 2. Selection of C1 and Re elements in the Colpitts-Pierce oscillator 2.2. Quartz oscillator implemented using TTL digital IC Fig. 3 presents a diagram of a quartz oscillator implemented using NAND gates in TTL technology. The oscillator works in series resonance. In this system, while maintaining the same resistance values, quartz resonators with a frequency from a few to 10 MHz can be used. 560 1k8 220 220 UWY XT Fig. 3. Cristal oscillator with serial resonance implemented with NAND gates in TTL technology In the laboratory exercise, it is proposed to implement the system using TTL series 74LS00 (pins of the IC are shown in in Fig.4). -

Modelling and Characterization of DCO Using Pass Transistors

2833 E.Kanniga et al./ Elixir Power Elec. Engg. 35 (2011) 2833-2835 Available online at www.elixirpublishers.com (Elixir International Journal) Power Electronics Engineering Elixir Power Elec. Engg. 35 (2011) 2833-2835 Modelling and characterization of DCO using Pass Transistors E.Kanniga 1 and M.Sundararajan 2 1Department of ECE, Bharath University, Chennai-73 2Gojan School of Business & Technology, Chennai-52. ARTICLE INFO ABSTRACT Article history: In the field of simulation work, it could proceed to an extent that, simulate with arbitrary Received: 6 April 2011; values of the passive component and the voltage sources. The simulation results recorded Received in revised form: various strategic points in the circuit indicate and validate the fact that the circuit is working 19 May 2011; in the expected lines with regard to the energy transfer in the expected lines with regard to Accepted: 26 May 2011; the energy transfer in the tank circuit and sustenance in DC transient Analysis. Also in this proposed experimental work, it is observed that for an arbitrary load, the voltage obtained is Keywords agreeing with the theoretically computed DC-Voltage levels. The scope of the work can be Digital controlled oscillator, extended to the actual calculation of the passives, the initial voltages across the capacitors Steady state transient response, and inductors. In addition to the exciting DC levels of the sources employed. The small Simulation LTSPICE, signal analysis can also be done with due regard to the desired behavioural properties of Varactors. switching devices used. © 2011 Elixir All rights reserved. ntroduction In the digital world there is an increased requirement for Fig1 shows that NMOS transistors configured as a Varactor Digitally Controlled Oscillator (DCO). -

Analysis of BJT Colpitts Oscillators - Empirical and Mathematical Methods for Predicting Behavior Nicholas Jon Stave Marquette University

Marquette University e-Publications@Marquette Master's Theses (2009 -) Dissertations, Theses, and Professional Projects Analysis of BJT Colpitts Oscillators - Empirical and Mathematical Methods for Predicting Behavior Nicholas Jon Stave Marquette University Recommended Citation Stave, Nicholas Jon, "Analysis of BJT Colpitts sO cillators - Empirical and Mathematical Methods for Predicting Behavior" (2019). Master's Theses (2009 -). 554. https://epublications.marquette.edu/theses_open/554 ANALYSIS OF BJT COLPITTS OSCILLATORS – EMPIRICAL AND MATHEMATICAL METHODS FOR PREDICTING BEHAVIOR by Nicholas J. Stave, B.Sc. A Thesis submitted to the Faculty of the Graduate School, Marquette University, in Partial Fulfillment of the Requirements for the Degree of Master of Science Milwaukee, Wisconsin August 2019 ABSTRACT ANALYSIS OF BJT COLPITTS OSCILLATORS – EMPIRICAL AND MATHEMATICAL METHODS FOR PREDICTING BEHAVIOR Nicholas J. Stave, B.Sc. Marquette University, 2019 Oscillator circuits perform two fundamental roles in wireless communication – the local oscillator for frequency shifting and the voltage-controlled oscillator for modulation and detection. The Colpitts oscillator is a common topology used for these applications. Because the oscillator must function as a component of a larger system, the ability to predict and control its output characteristics is necessary. Textbooks treating the circuit often omit analysis of output voltage amplitude and output resistance and the literature on the topic often focuses on gigahertz-frequency chip-based applications. Without extensive component and parasitics information, it is often difficult to make simulation software predictions agree with experimental oscillator results. The oscillator studied in this thesis is the bipolar junction Colpitts oscillator in the common-base configuration and the analysis is primarily experimental. The characteristics considered are output voltage amplitude, output resistance, and sinusoidal purity of the waveform. -

Pll Applications

PLL APPLICATIONS Contents 1 Introduction 1 2 Tracking Band-Pass Filter for Angle Modulated Signals 2 3 CW Carrier Recovery 2 4 PLL Frequency Divider and Multiplier 3 5 PLL Amplifier for Angle Modulated Signals 3 6 Frequency Synthesis and Angle Modulation by PLL 4 7 Coherent Demodulation by APLL 5 7.1 PM Demodulator . 5 7.2 FM Demodulator . 5 7.3 AM Demodulator . 6 8 Suppressed Carrier Recovery Circuits 6 8.1 Squaring Loop . 6 8.2 Costas Loop . 7 8.3 Inverse Modulator . 8 9 Clock Recovery Circuit 9 1 Introduction The PLL is one of the most commonly used circuits in electrical engineering. This section discusses the most important PLL applications and gives guidelines for the design of these circuits. A detailed discussion of different applications is beyond the scope of this article; for a comprehensive survey see [1] and [2]. The baseband model of analog phase-locked loop and its linear theory were discussed on the lecture. In all PLL applications, the phase-locked condition must be achieved and maintained. In order to avoid distortion, many applications require operation in the linear region, that is, the total variance of the phase error process resulting from noise and modulation must be kept small enough. If the PLL operates in the linear region then the linearized baseband model may be used in circuit design and development. Recall that only the PD output, VCO control voltage, input phase θi(t) and output phase θo(t) appear in the PLL baseband model. All these signals are low-frequency signals. -

Commissioning of the Mice Rf System* A

5th International Particle Accelerator Conference IPAC2014, Dresden, Germany JACoW Publishing ISBN: 978-3-95450-132-8 doi:10.18429/JACoW-IPAC2014-WEPME020 COMMISSIONING OF THE MICE RF SYSTEM* A. Moss, A. Wheelhouse, T. Stanley, C. White, STFC, Daresbury Laboratory, Warrington, UK K. Ronald, C.G. Whyte, A.J. Dick, D.C. Speirs, SUPA, Dept.of Physics, University of Strathclyde, Glasgow, UK S. Alsari, Imperial College of Science and Technology, London, UK on behalf of the MICE Collaboration Abstract feature adjustable sections to change the response of the cavity to both input line and resistive load. On the output The Muon Ionisation Cooling Experiment (MICE) is of the amplifier, the cavity length and hence its resonant being constructed at Rutherford Appleton Laboratory in frequency can be adjusted, whilst a stub tuner is located in the UK. The muon beam will be cooled using multiple the output coax section to alter the coupling factor into hydrogen absorbers then reaccelerated using an RF cavity the output coax so that the amplifier may be used to drive system operating at 201MHz. This paper describes recent a range of different load conditions. For use in the MICE progress in commissioning the amplifier systems at their system the 4616 operates in long pulse mode using grid design operation conditions, installation and operation as pulsed operation and can provide up to 250kW RF output part of the MICE project. power. INTRODUCTION 4616 Power Supply The muon ionisation cooling experiment is a The power supply for the tetrode amplifier consists of a demonstration of practical cooling for future muon TDK-Lambda 500A capacitor charger power supply acceleration schemes. -

PLL) for Wideband Clock Generation

UNIVERSITY OF CALIFORNIA Los Angeles A Multi-loop Calibration-free Phase-locked Loop (PLL) for Wideband Clock Generation A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Electrical Engineering by Dihang Yang 2019 c Copyright by Dihang Yang 2019 ABSTRACT OF THE DISSERTATION A Multi-loop Calibration-free Phase-locked Loop (PLL) for Wideband Clock Generation by Dihang Yang Doctor of Philosophy in Electrical Engineering University of California, Los Angeles, 2019 Professor Asad. A. Abidi, Chair In a wide-band RF system, the RF channel is located within 50 MHz to 9 GHz. A high- frequency resolution phase-locked loop (PLL) with 100% tuning range oscillator is the core to generate the RF carrier frequency which covers such a wide range. The phase noise and spurs of the PLL are required to be low to avoid degrading RF system performance. A PLL applies Σ∆ modulation to increases its resolution and is known as a fractional-N PLL, but Σ∆ modulation introduces considerable quantization noise into the loop. The nonlinearity of the PLL also converts part of the noise into fractional-N spurs. Noise cancellation is usually applied to eliminate this quantization noise. Calibration, often with long settling time, is necessary to maintain cancellation efficiency. Power intensive calibration is also required to notch spurious tones. In this thesis, we first investigate the delay-locked loop (DLL) and attempt to use DLL to replace PLL as an RF frequency synthesizer. An LTI model of DLL is established, which indicates the limitation of DLL as a high-performance synthesizer. -

10/29/07 11:40 PM Frequency Doublers

10/29/07 11:40 PM Frequency Doublers FREQUENCY DOUBLERS AN UNDERSTANDING AIDS IN EFFICIENT TUBE OPERATION National Radio Institute No. 19C A very high-powered oscillator/transmitter will not maintain its frequency at reasonably constant value. For this reason, high-power oscillators are seldom used. Instead, a master oscillator is designed to have the best possible frequency stability, and then a series of amplifying stages is used to get the required power. With this arrangement, it is possible to draw very little power from the oscillator, thus insuring its frequency stability. Frequency Multiplication. It may happen that crystals cannot produce a frequency as high as the required output frequency. If so, it is possible to design an intermediate amplifier so that it has a strong harmonic output. The second or third harmonic of the crystal frequency may then be taken from this amplifier and amplified by the succeeding intermediate amplifier stages. This lets us get an output frequency that may be two or three times the master oscillator frequency. By using a chain of multipliers in this manner, we can get frequencies of four, six, or any other multiple of the master oscillator output. The most practical form of oscillator possessing a high degree of frequency stability is one in which the frequency is determined by mechanical oscillation of a piezoelectric quartz crystal. Because of such desirable characteristics, almost all modern transmitters use some form of crystal-controlled master oscillator. The natural mechanical resonance of a crystal is determined primarily by its thickness, and crystals are ground very carefully to a definite thickness to make them oscillate at some specific frequency. -

High-Impedance Fault Diagnosis: a Review

energies Review High-Impedance Fault Diagnosis: A Review Abdulaziz Aljohani 1,* and Ibrahim Habiballah 2 1 Unconventional Resources Engineering and Project Management Department, Saudi Arabian Oil Company (Saudi Aramco), Dhahran 31311, Saudi Arabia 2 Electrical Engineering Department, King Fahd University of Petroleum and Minerals, Dhahran 31261, Saudi Arabia; [email protected] * Correspondence: [email protected] Received: 9 November 2020; Accepted: 30 November 2020; Published: 5 December 2020 Abstract: High-impedance faults (HIFs) represent one of the biggest challenges in power distribution networks. An HIF occurs when an electrical conductor unintentionally comes into contact with a highly resistive medium, resulting in a fault current lower than 75 amperes in medium-voltage circuits. Under such condition, the fault current is relatively close in value to the normal drawn ampere from the load, resulting in a condition of blindness towards HIFs by conventional overcurrent relays. This paper intends to review the literature related to the HIF phenomenon including models and characteristics. In this work, detection, classification, and location methodologies are reviewed. In addition, diagnosis techniques are categorized, evaluated, and compared with one another. Finally, disadvantages of current approaches and a look ahead to the future of fault diagnosis are discussed. Keywords: high-impedance fault; fault detection techniques; fault location techniques; modeling; machine learning; signal processing; artificial neural networks; wavelet transform; Stockwell transform 1. Introduction High-impedance faults (HIFs) represent a persistent issue in the field of power system protection. Hence, a comprehensive understanding of such faults is a necessity for many engineers in order to innovate practical solutions. The authors of [1,2] introduced an HIF detection-oriented review. -

AN826 Crystal Oscillator Basics and Crystal Selection for Rfpic™ And

AN826 Crystal Oscillator Basics and Crystal Selection for rfPICTM and PICmicro® Devices • What temperature stability is needed? Author: Steven Bible Microchip Technology Inc. • What temperature range will be required? • Which enclosure (holder) do you desire? INTRODUCTION • What load capacitance (CL) do you require? • What shunt capacitance (C ) do you require? Oscillators are an important component of radio fre- 0 quency (RF) and digital devices. Today, product design • Is pullability required? engineers often do not find themselves designing oscil- • What motional capacitance (C1) do you require? lators because the oscillator circuitry is provided on the • What Equivalent Series Resistance (ESR) is device. However, the circuitry is not complete. Selec- required? tion of the crystal and external capacitors have been • What drive level is required? left to the product design engineer. If the incorrect crys- To the uninitiated, these are overwhelming questions. tal and external capacitors are selected, it can lead to a What effect do these specifications have on the opera- product that does not operate properly, fails prema- tion of the oscillator? What do they mean? It becomes turely, or will not operate over the intended temperature apparent to the product design engineer that the only range. For product success it is important that the way to answer these questions is to understand how an designer understand how an oscillator operates in oscillator works. order to select the correct crystal. This Application Note will not make you into an oscilla- Selection of a crystal appears deceivingly simple. Take tor designer. It will only explain the operation of an for example the case of a microcontroller. -

Fully-Integrated, Fixed Frequency, Low-Jitter Crystal Oscillator Clock

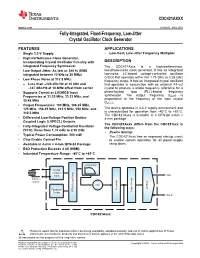

CDC421AXXX www.ti.com ....................................................................................................................................................................................................... SCAS875–MAY 2009 Fully-Integrated, Fixed-Frequency, Low-Jitter Crystal Oscillator Clock Generator 1FEATURES APPLICATIONS • 2• Single 3.3-V Supply Low-Cost, Low-Jitter Frequency Multiplier • High-Performance Clock Generator, Incorporating Crystal Oscillator Circuitry with DESCRIPTION Integrated Frequency Synthesizer The CDC421Axxx is a high-performance, • Low Output Jitter: As low as 380 fs (RMS low-phase-noise clock generator. It has an integrated integrated between 10 kHz to 20 MHz) low-noise, LC-based voltage-controlled oscillator • (VCO) that operates within the 1.75 GHz to 2.35 GHz Low Phase Noise at 312.5 MHz: frequency range. It has an integrated crystal oscillator – Less than –120 dBc/Hz at 10 kHz and that operates in conjunction with an external AT-cut –147 dBc/Hz at 10-MHz offset from carrier crystal to produce a stable frequency reference for a • Supports Crystal or LVCMOS Input phase-locked loop (PLL)-based frequency Frequencies at 31.25 MHz, 33.33 MHz, and synthesizer. The output frequency (fOUT) is 35.42 MHz proportional to the frequency of the input crystal (fXTAL). • Output Frequencies: 100 MHz, 106.25 MHz, 125 MHz, 156.25 MHz, 212.5 MHz, 250 MHz, and The device operates in 3.3-V supply environment and 312.5 MHz is characterized for operation from –40°C to +85°C. The CDC421Axxx is available in a QFN-24 4-mm × • Differential Low-Voltage Positive Emitter 4-mm package. Coupled Logic (LVPECL) Outputs • The CDC421Axxx differs from the CDC421xxx in Fully-Integrated Voltage-Controlled Oscillator the following ways: (VCO): Runs from 1.75 GHz to 2.35 GHz • Device Startup • Typical Power Consumption: 300 mW The CDC421Axxx has an improved startup circuit • Chip Enable Control Pin to enable correct operation for all power-supply • Available in 4-mm × 4-mm QFN-24 Package ramp times. -

Eimac Care and Feeding of Tubes Part 3

SECTION 3 ELECTRICAL DESIGN CONSIDERATIONS 3.1 CLASS OF OPERATION Most power grid tubes used in AF or RF amplifiers can be operated over a wide range of grid bias voltage (or in the case of grounded grid configuration, cathode bias voltage) as determined by specific performance requirements such as gain, linearity and efficiency. Changes in the bias voltage will vary the conduction angle (that being the portion of the 360° cycle of varying anode voltage during which anode current flows.) A useful system has been developed that identifies several common conditions of bias voltage (and resulting anode current conduction angle). The classifications thus assigned allow one to easily differentiate between the various operating conditions. Class A is generally considered to define a conduction angle of 360°, class B is a conduction angle of 180°, with class C less than 180° conduction angle. Class AB defines operation in the range between 180° and 360° of conduction. This class is further defined by using subscripts 1 and 2. Class AB1 has no grid current flow and class AB2 has some grid current flow during the anode conduction angle. Example Class AB2 operation - denotes an anode current conduction angle of 180° to 360° degrees and that grid current is flowing. The class of operation has nothing to do with whether a tube is grid- driven or cathode-driven. The magnitude of the grid bias voltage establishes the class of operation; the amount of drive voltage applied to the tube determines the actual conduction angle. The anode current conduction angle will determine to a great extent the overall anode efficiency. -

Crystals Load Capacitance Calculation And

Load Capacitance PRINTED: 12/21/2012 TYPICAL OSCILLATOR CIRCUIT OSC CELL OSC CELL = oscillator circuit integrated into any IC. Rf = feedback resistor, sometimes integrated in IC or is required as external resistor Rf CLOCK SIGNAL Cg = capacitance of oscillator input for IC internal use Cd = capacitance of oscillator output Rd = Phase shift resistor, necessary at lower frequencies to meet oscillation condition that phase shift all the way around the oscillator loop need to add up to 360°. Y1 = Quartz crystal unit C1 and C1 = external load capacitors. CPCB1 and CPCB2 = stray capacitances of PCB traces Cg Cd The total LOAD CAPACITANCE of the oscillator circuit is the sum of all capacitances. OSC IN OSC OUT consisting of: 1. The two external capacitors (here called C1 and C2) 2. The IC input and output capacitances (here called Cg and Cd) 3. The stray capacitances of PCB traces (here called CPCB1 and CPCB2) CPCB1 Rd Commonly being only the values of the external capacitors known so that a correct calculation of the actual load capacitance is not possible. SIGNAL OUTPUT OPTIONALCLOCK In such case we use simlified formula to calculate the load capacitance as: C1 C2 CL C TOTAL C1 C2 STRAY CPCB2 Here C1 and C2 are the external capacitors in the cricuit, values should be known. Cstray is summarized value for IC input and output capacitance and the PCB traces. Y1 Cstray in a 3.3VDC circuit is often 3~4pF. C1 C2 Cstray in a 5.0VDC circuit often 5~7pF. However, we have also seen circuits that had large deviation from these values.