Thesis Electronic In-Circuit PCB Testers Identifier PCB Tester

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Am 503 Current Probe Amplifier

AM 503 CURRENT PROBE AMPLIFIER 7eIdCOMMITTEDronbcTO EXCELLENCE PLEASE CHECK FOR CHANGE INFORMATION AT THE REAR OF THIS MANUAL. AM 503 CURRENT PROBE AMPLIFIER INSTRUCTION MANUAL Tektronix, Inc. P.O. Box 500 Beaverton, Oregon 97077 Serial Number 070-2052-01 First Printing SEP 1976 Product Group 75 Revised DEC 1985 Copyright `' 1976, 1979 Tektronix, Inc . All rights reserved. Contents of this publication may not be reproduced in any form without the written permission of Tektronix, Inc. Products of Tektronix, Inc . and its subsidiaries are covered by U .S. and foreign patents and/or pending patents. TEKTRONIX, TEK, SCOPE-MOBILE, and ilk are registered trademarks of Tektronix, Inc. TELEQUIPMENT is a registered trademark of Tektronix U .K. Limited. Printed in U .S .A. Specification and price change privileges are reserved. INSTRUMENT SERIAL NUMBERS Each instrument has a serial number on a panel insert, tag, or stamped on the chassis. The first number or letter designates the country of manufacture. The last five digits of the serial number are assigned sequentially and are unique to each instrument. Those manufactured in the United States have six unique digits. The country of manufacture is identified as follows : B000000 Tektronix, Inc., Beaverton, Oregon, USA 100000 Tektronix Guernsey, Ltd., Channel Islands 200000 Tektronix United Kingdom, Ltd., London 300000 Sony/Tektronix, Japan 700000 Tektronix Holland, NV, Heerenveen, The Netherlands TABLE OF CONTENTS Page OPERATOR'S SAFETY SUMMARY . SERVICE SAFETY SUMMARY . V SECTION 1 OPERATING INSTRUCTIONS . 1-1 SECTION 2 SPECIFICATION AND PERFORMANCE CHECK . 2-1 WARNING The remaining portion of this Table of Contents lists servicing instructions that expose personnel to hazardous voltages. -

Tektronix Cookbook of Standard Audio Tests

( Copyright © 1975, Tektronix, Inc. AI! rig hts re served P ri nt ed· in U .S.A. ForeIg n and U .S.A. Products of Tektronix , Inc. are covered by Fore ign and U .S.A . Patents and /o r Patents Pending. Inform ation in thi s publi ca tion supersedes all previously published material. Specification and price c hange pr ivileges reserve d . TEKTRON I X, SCOPE-MOBILE, TELEOU IPMENT, and @ are registered trademarks of Tekt ro nix, Inc., P. O. Box 500, Beaverlon, Oregon 97077, Phone : (Area Code 503) 644-0161, TWX : 910-467-8708, Cabl e : TEKTRON IX. Overseas Di stributors in over 40 Counlries. 1 STANDARD AUDIO TESTS BY CLIFFORD SCHROCK ACKNOWLEDGEMENTS The author would like to thank Linley Gumm and Gordon Long for their excellent technical assistance in the prepara tion of this paper. In addition, I would like to thank Joyce Lekas for her editorial assistance and Jeanne Galick for the illustrations and layout. CONTENTS PRELIMINARY INFORMATION Test Setups ________________ page 2 Input- Output Load Matching ________ page 3 TESTS Power Output _______________ page 4 Frequency Response ____________ page 5 Harmonic Distortion _____________ page 7 Intermodulation Distortion __________ page 9 Distortion vs Output _____________ page 11 Power Bandwidth page 11 Damping Factor page 12 Signal to Noise Ratio page 12 Square Wave Response page 15 Crosstalk page 16 Sensitivity page 16 Transient Intermodulation Distortion page 17 SERVICING HINTS___________ page19 PRELIMINARY INFORMATION Maintaining a modern High-Fidelity-Stereo system to day requires much more than a "trained ear." The high specifications of receivers and amplifiers can only be maintained by performing some of the standard measure ments such as : 1. -

Introduction to In-Circuit Testing.Pdf

Introduction to In-Circuit Testing Introduction In-Circuit Testing Wd,Inc. 1984 Concord, Massachusetts, U.S.A. 01742 Jmuarg l9M The following are wademarks of GenRad, lnc. SCRATCHPROBING GRnet BUSBUST The foHowing are trademarks of Digid Equipment Corporation, Maymtd, Mass. DRC Rsx VT Contents Chapter 2 Tdmtques for In-Circuit Tesdng .. .. .. .. .. 17 ; chapter 3 , A Look at an In-Circuit Tatex .. .. .. .- . .. .. .. 5 3 chapter 4 ' U* the ester .. .. , i .'. ; A:,, ;i .. 89 Chap~2 - Techniques For Mmit -~-a the mitical concepts of at- via the bed-of-& fhitwe adid&on of the components on the hdby gudhgfor analog wad W- driving for digid cumponents. Chapter 3 - A Look at an In-CWt Tester demibes the had- ware and sohcomponeflts of an in-circuit tester and the functions these components perform. Chapter 4 - Udng the T~texoutlines the stepby-step proceas wed by a programmer to develop a test program and by an operator to test bod. Fot easy reference, P of terms umdsted with bdrdt testing is hhdedat Ehe back of this docllmcnt. Chapter 1 Introduction So. tell me almut in-circuit tcqtin~, Before getting into in-circuit testing, let's review some important aspects of printed circuit (pr) board manufacturing and testing. As you know, the design and assembly of pc boards follow certain basic steps: 1. First. assembly and drill drawings of the board are developed from the schematic diagram. These drawings show where each component will be placed, where each track (wiring connection) will be etched, where each component mounting hole will be located, etc. 2. Then, holes for the component leads are dr:lled in a blank board and tracks are etched on the surfarc of the board to connect the components tqerher. -

The Trouble with Oscilloscope Probes and an “Off-Piste” Design for Microwave and Gigabit Applications

The Trouble with Oscilloscope Probes and an “off-piste” design for microwave and gigabit applications Mark V. Ashcroft Pico Technology Ltd. St. Neots, United Kingdom [email protected] Abstract—The low-cost hand-held oscilloscope probe has Two common microwave and gigabit measurement changed very little in the last three or four decades. Arguably it solutions in use today do not even achieve measurement during has lost touch with its applications as signals have become faster, system function. A third is often so invasive, or so costly that smaller and more prone to the invasive nature of their we often accept mere detection of presence, or capture of the measurement. This paper reviews the rapidly growing scale of ‘general shape’ of a signal. In doing so, we may threaten the problem and proposes a more appropriate design approach ongoing system function in the hope of not quite interrupting it. to achieve a microwave and gigabit test probe. A. Break into the Signal Transmission Line Keywords—oscilloscope; test; active; passive; hand-held; Without doubt the method having greatest measurement browser; logic; probe; microwave; RF; gigabit. integrity is to break into the transmission line and route its I. INTRODUCTION - GIGABIT DATA AND WIRELESS EVERYWHERE signal to a correctly matched terminating or ‘sniffing’ measurement instrument. The latter could in some Today we are surrounded by gigabit per second data flow circumstances re-inject the signal back into the system under and wireless technologies in our homes, our cars, the test, albeit with delay, loss of amplitude or distortions. Most workplace and on our person. -

Probe Selection Guide

Probe Selection Guide Document maintained by the Probes Marketing Team. Please submit feedback to Seamus Brokaw, [email protected] Probe / Oscilloscope Compatibility TekProbe TekProbe TekVPI w/ BNC LEVEL1 LEVEL2 TekVPI HardKey FlexChannel TekConnect Std BNC TDS1000/2000 TBS1000 TPS2000 Readout not functional 1103 POWER SUPPLY THS3000 (50Ω termination may be required) TekProbe LEVEL1 1103 POWER SUPPLY (50Ω termination may be required) TekProbe LEVEL2 TDS3000 TDS5000 *1 TDS7054/7104 TekVPI TBS2000 MSO/DPO2000 *2 *2,*3,*5 MSO/DPO3000 MSO/DPO4000 TPA-BNC DPO7000C TekVPI w/ HardKey *4,*5 3 Series MDO MSO/DPO4000B MDO3000/4000C TPA-BNC MSO/DPO5000 FlexChannel 4 Series MSO 5 Series MSO 6 Series MSO TPA-BNC TekConnect MSO/DSA/DPO70000 TDS6000 TCA-BNC TCA-1MEG TCA-1MEG TCA-VPI50 (ADA400A, P52xx) (50Ω probe only) TDS7154/B, 7254B, 7404B, or 7704B, CSA7154, 7404/B TCA-BNC *1 Some probes require an external power supply (1103) when used with the TDS3000 series *2 When using with MSO / DPO2000 series, a dedicated AC adapter (119-8726-00) and a power cable (161-0342-00) are required. *3 When using with MSO / DPO3000 series, depending on the probe you may need a separate AC adapter (119-8726-00) and a power cable (161-0342-00). *4 When using with MSO / DPO5000 series, separate AC adapter (119-8726-00) and power cable (161-0342-00) may be required depending on the probe model and number. *5 when using with TBS2000 and MDO3000 series, the total power draw capacity can not exceed the maximum power supply capacity of the oscilloscope, see here for more information. -

Simpson Electric Test Equipment Catalog

Test Equipment Catalog No One Beats Simpson on Quality When asked why they buy Simpson What establishes Simpson Electric Products, Simpson customers consistently Company as an icon of excellence in the use the word “quality.” Customers trust test equipment market? Ultimately, the Simpson products to give accurate and answer lies in Simpson Electric’s constant readings, durable and reliable reputation for quality and value and performance, and easy operation. customer trust in the superiority of Simpson products. One Simpson customer describes Simpson products as “...the best value...because they’re constant.” Customers also Phone: (715) 588-3947 appreciate Simpson’s “rugged” and “easy to Fax: (715) 588-1248 use” meters. Simpson’s durable cases Email: [email protected] or withstand chemical vapors and other harsh [email protected] environments, and no other testers on the Write to: market are easier to use than Simpson Simpson Electric Company testers. P.O. Box 99 520 Simpson Avenue Another Simpson product user remarks “No Lac du Flambeau, WI 54538 one beats Simpson on Quality.” Visit the Simpson Electric Website: www.simpsonelectric.com Simpson Electric Company is 100% owned by the Lac du Flambeau Band of Lake Superior Chippewa Indians. The Chippewa Band dedicates itself to expanding Simpson’s success in the Test Equipment Industry and to furthering economic growth in the Native American community. Simpson Electric is certified as an MBE (Minority Business Enterprise) by the Wisconsin Supplier Development Council, which is a member of the National Supplier Development Council. Table of Contents 260-9S & 260-9SP Industrial Safety VOM . .3 260-8 & 260-8P Analog VOM . -

Low Capacitance Electrical Probe for Nanoscale Devices and Circuits

The Open Nanoscience Journal, 2008, 2, 39-42 39 Open Access Low Capacitance Electrical Probe for Nanoscale Devices and Circuits Leonard Forbes*, Drake A. Miller** and Michael E. Jacob** *L. Forbes and Associates LLC, PO Box 1716, Corvallis, OR, 97339-1716 USA **Elect. Eng. and Comp. Science., Oregon State University, Corvallis, OR, 97331-5501 USA Abstract: An electrical probe is constructed of a small capacitor in contact with the circuit node under test so as not to load this circuit node and cause distortion of the input signal. The small capacitor is then placed in series with the small input resistance of a terminated coaxial signal line. The voltage signal at the output of the coaxial line will be approxi- mately the product of the small capacitance, the resistance of the coaxial line and the derivative with respect to time of the input signal. Tungsten probe tips can be sharpened to 100nm or less, enabling measurements of nanoscale devices. INTRODUCTION Tungsten probe whiskers can however still be sharpened to submicron and nanoscale dimensions, the passivation on In a commonly used measurement techniques the general integrated circuits removed and the tungsten probes placed characteristics of an electrical probe have been to measure a on internal nodes. These internal nodes however can drive voltage signal. The desirable characteristics of such a probe only very small capacitive loads of the order less than 10 fF. are: (a) the probe should not influence or “load” the response of the circuit under test; (b) and that it should provide an Cprobe MEASUREMENT accurate perhaps attenuated representation of the probed INSTRUMENT signal over a range of frequencies. -

Testing Electronic Components

Testing Electronic Components Brought to you by Jestine Yong http://www.ElectronicRepairGuide.com http://www.TestingElectronicComponents.com http://www.FindBurntResistorValue.com http://www.JestineYong.com You cannot give this E-book away for free. You do not have the rights to redistribute this E-book. Copyright@ All Rights Reserved Warning! This is a copyrighted material; no part of this guide may be reproduced or transmitted in any form whatsoever, electronic, or mechanical, including photocopying, recording, or transmitting by any informational storage or retrieval system without expressed written, dated and signed permission from the author. You cannot alter, change, or repackage this document in any manner. Jestine Yong reserves the right to use the full force of the law in the protection of his intellectual property including the contents, ideas, and expressions contained herein. Be aware that eBay actively cooperates in closing the account of copyright violators and assisting in the legal pursuit of violations. DISCLAIMER AND/OR LEGAL NOTICES The reader is expressly warned to consider and adopt all safety precaution that might be indicated by the activities herein and to avoid all potential hazards. This E-book is for informational purposes only and the author does not accept any responsibilities or liabilities resulting from the use of this information. While every attempt has been made to verify the information provided here, the author cannot assume any responsibility for any loss, injury, errors, inaccuracies, omissions or inconvenience sustained by anyone resulting from this information. Most of the tips and secrets given should only be carried out by suitably qualified electronics engineers/technicians. -

9908-TE HIGH PRECISION AUTO-RANGING DC/True RMS AC BENCH-TOP DIGITAL MULTIMETER

OWNER’S MANUAL 9908-TE HIGH PRECISION AUTO-RANGING DC/True RMS AC BENCH-TOP DIGITAL MULTIMETER IMPORTANT! Read and understand this manual before using the instrument. Failure to understand and comply with safety rules and operating Instructions can result in serious or fatal injuries and/or property damage. Distributed by: Marlin P. Jones & Associates, Inc. www.mpja.com www.briefcasetools.com www.powersupplydepot.com Owner’s Manual 9908-TE Auto-Ranging DC/True RMS AC Bench-top Digital Multimeter 1. DESCRIPTION The 9908-TE bench-top auto-ranging digital multimeter is designed for measuring resistance, DC and True RMS AC voltage, DC and True RMS AC current, frequency, capacitance, testing diodes and checking continuity. This meter is designed for indoor use at altitudes up to 2000m, temperatures between 5OC and 40OC, and a maximum humidity of 80% at temperatures up to 31OC with decreasing linearly to 50% relative humidity at 40OC and a pollution degree of 2. The large backlit LCD display with bargraph is clear and easy to read. The easy access push buttons, the auto-range, relative measurement, Maximum /Minimum measurement, data hold and data memory functions make this multimeter a versatile solution for your measurement needs now and in the future. 2. SAFETY INSTRUCTIONS This meter has been designed for safe use in accordance with IEC61010.1 CAT II, but must be operated with caution. The rules listed below must be carefully followed for safe operation. 2.1 NEVER operate this instrument when the cover is open or not properly attached in its place. 2.2 Make sure that the insulation of the test leads is not damaged. -

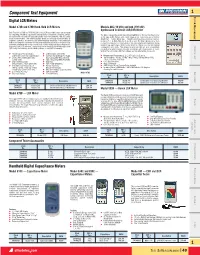

Component Test Equipment 1 T EST

49-2012:QuarkCatalogTempNew 9/20/12 1:18 PM Page 49 Component Test Equipment 1 T EST Digital LCR Meters & M Model 878B and 879B Hand-Held LCR Meters Models 885 (10 kHz) and 886 (100 kHz) EASUREMENT Synthesized In-Circuit LCR/ESR Meter B&K Precision’s 878B and 879B 40,000 count L/C/R hand-held meters are designed for measuring inductance, capacitance, and resistance components. Simple to operate, The Model 886 Synthesized In-Circuit LCR/ESR Meter is the first handheld meter the instruments not only take absolute parallel mode measurements, but also series of this type on the market, with a wide range of test frequencies up to 100 kHz mode measurements. The meters provide direct and accurate measurements of (Model 865 — 10 kHz; Model 866 — 100 kHz) and many measurement parameters inductors, capacitors, and resistors with different testing frequencies. Front panel push including Z, L, C, DCR, ESR, D, Q, and Ø as well. The 886 is designed for both buttons maximize the convenience of function and feature selection such as data hold, component evaluation on the production line and fundamental impedance testing maximum, minimum and average record mode, relative mode, tolerance sorting mode, for bench top applications. With a built-in direct test fixture, you can test the lead I frequency, and L/C/R selection. The test data can be transferred to PC through a mini components very easily. The optional 4-wire test clip can give a convenient NTERCONNECT USB connection with free downloadable software or with SCPI commands. connection to larger components and assemblies with the accuracy of 4-wire testing. -

WP-Tests-Flying-Prob

What Electronics Manufacturers Test and Inspect For, and Why It Matters Authors: Dan Kreider, Test Engineer, Axiom Electronics; John Kim, Manufacturing Engineer, Axiom Electronics October 2017 Test is extremely important when manufacturing low-volume/high-complexity electronics in critical applications, such as secure communications, target acquisition and destruction, or in space applications where the assembly is usually on a one-way trip that will not receive ser- vice calls. This white paper addresses what manufacturers test for and details the important testing and inspection routines from receiving the Printed Circuit Board (PCB) to testing the completed Printed Circuit Board Assembly (PCBA). Defective ICs and bad fabs are rare, and ICs. Boundary scan can be an effective test they can be difficult to detect with our auto- mode for highly complex boards. mated testers. Flying probe test strategy basi- cally assumes the Printed Circuit Board (PCB) Open solder/missing components is the is good (tested at the PCB fabrication facility). most common assembly defect category. Both A defective IC may be shorted or open across flying probe and ICT (bed-of-nails) test for a set of pins. This may lead to a failure of an these issues, particularly for passive and dis- automated test like flying probe or ICT, or it crete components. Lifted pins on IC legs (or may affect a diode junction or capacitance open solder joints on BGAs) can be detected test, otherwise the defect may go undetected. in many cases. It is possible to measure the protection diodes built into many ICs to detect JTAG/boundary-scan testing is effective at open/shorted pins or defective components. -

Integrated Circuit Test Engineering Iana.Grout Integrated Circuit Test Engineering Modern Techniques

Integrated Circuit Test Engineering IanA.Grout Integrated Circuit Test Engineering Modern Techniques With 149 Figures 123 Ian A. Grout, PhD Department of Electronic and Computer Engineering University of Limerick Limerick Ireland British Library Cataloguing in Publication Data Grout, Ian Integrated circuit test engineering: modern techniques 1. Integrated circuits - Verification I. Title 621.3’81548 ISBN-10: 1846280230 Library of Congress Control Number: 2005929631 ISBN-10: 1-84628-023-0 e-ISBN: 1-84628-173-3 Printed on acid-free paper ISBN-13: 978-1-84628-023-8 © Springer-Verlag London Limited 2006 HSPICE® is the registered trademark of Synopsys, Inc., 700 East Middlefield Road, Mountain View, CA 94043, U.S.A. http://www.synopsys.com/home.html MATLAB® is the registered trademark of The MathWorks, Inc., 3 Apple Hill Drive Natick, MA 01760- 2098, U.S.A. http://www.mathworks.com Verifault-XL®, Verilog® and PSpice® are registered trademarks of Cadence Design Systems, Inc., 2655 Seely Avenue, San Jose, CA 95134, U.S.A. http://www.cadence.com/index.aspx T-Spice™ is the trademark of Tanner Research, Inc., 2650 East Foothill Blvd. Pasadena, CA 91107, U.S.A. http://www.tanner.com/ Apart from any fair dealing for the purposes of research or private study, or criticism or review, as permitted under the Copyright, Designs and Patents Act 1988, this publication may only be reproduced, stored or transmitted, in any form or by any means, with the prior permission in writing of the publishers, or in the case of reprographic reproduction in accordance with the terms of licences issued by the Copyright Licensing Agency.