Analysis of Lightning Arrester Overloading in Future

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Hvdc Back to Back Connection for Power Exchange Between Electrical Grids

HVDC BACK TO BACK CONNECTION FOR POWER EXCHANGE BETWEEN ELECTRICAL GRIDS by MD. ARIFUR RAHMAN DEPARTMENT OF ELECTRICAL AND ELECTRONIC ENGINEERING DHAKA UNIVERSITY OF ENGINEERING AND TECHNOLOGY GAZIPUR December-2014 HVDC BACK TO BACK CONNECTION FOR POWER EXCHANGE BETWEEN ELECTRICAL GRIDS A Project Report Submitted in partial fulfillment of the requirements for the degree of Master of Electrical and Electronic Engineering By MD. ARIFUR RAHMAN Student No: 022219 Session: 2003-2004 Supervised By Dr. Md. Bashir Uddin Professor DEPARTMENT OF ELECTRICAL AND ELECTRONIC ENGINEERING DHAKA UNIVERSITY OF ENGINEERING AND TECHNOLOGY GAZIPUR December-2014 Declaration It is hereby declared that this project or any part of it has not been submitted elsewhere for the award of any degree or diploma. Candidate’s Signature (Md. ArifurRahman) ii Acknowledgement It is a great pleasure of the author to acknowledge respect and gratitude to the supervisor Dr. Md. Bashir Uddin, Professor, Department of Electrical and Electronic Engineering, DUET, Gazipur, for his kind cooperation, constant encouragement, valuable advice and guidance throughout the project work. Dr. Md. Bashir Uddin provided with information, comments, corrections and criticisms pertaining to the preparation of this project hand note. Without his whole-hearted supervision, this work would not have been possible. I am grateful to Dr. Md. AnowarulAbedin,Professor & Head, Department of Electrical and Electronic Engineering for providing the opportunity of completion of M. Engineering degree through extending my student-ship. I am thankful to Project Director, Manager and Engineer Colleagues of Grid Interconnection Project, Power Grid Company of Bangladesh Ltd. for providing the information against HVDC and Grid Interconnection. -

Lightning on Transmission Line of the Harm and Prevention Measures

Lightning on transmission lines hazards and Prevention Measures Wang Qinghao, Ge Changxin, Xue Zhicheng, Sun Fengwei, Wu Shaoyong, Li Zhixuan, Shi Dongpeng, Ren Hao, Li Jinye, Ma Hui, Cao Feiyi Fushun Power Supply Company, Liaoning Electric Power Company Limited, State Grid, China, [email protected] Keywords: power transmission line, lightning hazard, prevention measures Abstract. Through the analysis of lightning to the harmfulness of the power transmission line, puts forward the specific measures to prevent lightning accidents, improving insulation, installing controllable discharge lightning rod, reducing the tower grounding resistance, adding coupling ground wire and the proper use of send arrester electrical circuit transmission line. And take on the unit measures nearly were compared, statistics and analysis. Introduction Lightning accident is always an important factor affecting the reliability of the power supply of the electric line to send. Because of the randomness and complexity of lightning activity in the atmosphere, currently the world's research on knowledge transmission line lightning and many unknown elements. Lightning accident of overhead power transmission line is always a problem of safe power supply, lightning accidents accounted for almost all the accidents of 1/2 or more line. Therefore, how to effectively prevent lightning, lightning damage reduced to more and more by transmission line of the relevant personnel to pay attention[1-2]. At present, the measures of lightning protection of transmission line itself mainly rely on the erection of the overhead ground wire of the tower top, its operation and maintenance work is mainly on the detection and reconstruction of tower grounding resistance. Due to its single lightning protection measures, can not well meet the requirements of lightning protection. -

Application and Analysis for Surge Arrester on Lightning Protection of Distribution Network

MATEC Web of Conferences 40, 007 10 (2016) DOI: 10.1051/matecconf/20164007010 C Owned by the authors, published by EDP Sciences, 2016 Application and Analysis for Surge Arrester on Lightning Protection of Distribution Network Daxing WANG1 , Bin HE 1 ,Wei ZHONG 1,Bo LIN 1, Dong WANG1, Tingbin LI 1 1 SICHUAN TONG YUAN ELECTRIC POWER SCIENCE&TECHNOLOGY CO., LTD, Chengdu,China Abstract. In order to effectively reduce lightning stroke outage rate, effect of lightning protection with surge arrester on transmission line has been generally acknowledged relative to other lightning protection measures. This article introduces in such aspects as the working principle of line surge arrester and effect of lightning protection, and also explores application for lightning arrester of distribution network to achieve difference lightning protection and improve the lightning protection performance of distribution network. Keywords: Surge arrester, lightning protection, distribution network. 1 Introduction According to operational experience at home and abroad, 2 The working principle of surge lightning stroke is the main reason to cause line tripping arrester and service interruption, according to the statistical report of interruption of service in china, 40%~70% of the Surge arrester generally uses the body and air gap, and accident in the power system are caused by lightning surge arrester does not assume system operating voltage, which has brought a great loss to national economy. without considering the long-running voltage electrical In general, the methods which include improving the aging, also the body failure does not affect operation. insulation level of line, decreasing grounding resistance, When a lightning flash directly strikes the tower, part decreasing protection angle and so on have been used in of the lightning current flows through the grounding wire cutting down lightning accidents. -

Lightning Performance of Medium Voltage Transmission

ISSN 2319-8885 Vol.03,Issue.16 July-2014, Pages:3362-3367 www.semargroup.org, www.ijsetr.com Lightning Performance of Medium Voltage Transmission Line Protected by Surge Arresters 1 2 NANG KYU KYU THIN , KHIN THUZAR SOE 1Dept of Electrical Power Engineering, Mandalay Technological University, Mandalay, Myanmnar, E-mail: [email protected]. 2Assoc Prof, Dept of Electrical Power Engineering, Mandalay Technological University, Mandalay, Myanmnar, E-mail: [email protected]. Abstract: Lightning strikes to overhead transmission lines are a usual reason for unscheduled supply interruption in the modern power system, In an effort to maintain failure rates in a low level, providing high power quality and avoiding damages and disturbances, plenty of lightning performance estimation studies have been conducted and several design methodologies have been proposed. The protection of overhead transmission lines is achieved using shield wires and surge arresters. Surge arresters should be insulators at any voltage below the protected voltage, and good conductor at ant voltage above. to pass the energy of the lightning strike to ground. In this work an analysis of the lightning performance of 33 kV Aung Pin Lae - Myoma transmission line. The line is protected with only surge arresters and the current simulation of surge arrester is implemented on the sending end and receiving end of the network. By increasing the tower footing resistance, the lightning failure rate become greater. Smaller arresters intervals decerase the failure rate. The results of the current work could be useful for the maintenance and the design of Aung Pin Lae - Myoma 33 kV transmission line. Keywords: Shield Wire, Surge Arrester, Tower Footing Resistance, Transmission Line. -

"Lightning" Arrester

SECONDARY HE900 SURGE 480VAC "LIGHTNING" 3∅, 3W FEATURES ARRESTER • Industrial/Commercial Version • MOV Circuit Design • Made in America utilizing American Components • Cost Effective • Reliable Solid-State Protection • Maintenance Free • Molded Plastic Case • Threaded 1/2" NPT conduit nipple with locknut • 18 " Stranded 12 AWG color coded leads • Suitable for indoor or outdoor installation • Automatic Recovery, Self Restoring DESCRIPTION The HE900 is a MOV (Metal Oxide Varistor) based hardwired Secondary Surge Arrester, often referred to as a Lightning Arrester. The device is designed to protect electrical equipment from damaging effects of Spikes (+) and Notches (-) caused by lightning, utility switching, insulation arcing, electrical motor cycling, and other large or sudden changes in electrical power flow on incoming AC power lines. The HE900 is a three phase, three wire arrester intended to protect 480 VAC systems. The epoxy encapsulated arrester is designed to be easily installed in any position indoors or outdoors utilizing the integral 1/2" threaded nipple and supplied metal lock nut. The housing is molded from flame retardant plastic that is both weather and UV resistant, and complies with the UL standard for strength and flame resistance properties. The arrester is sealed with UL component recognized epoxy potting compound. The HE900 has three 18" long, 12 AWG multi-stranded leads that are color coded for ease of installation. The HVPSI HE900 is ideal protection for outdoor lighting and pole lamps, panelboards, oilfield pumps, workshops, irrigation and sump pumps, refrigeration systems, farm equipment including milking machines and poultry processing equipment, electric motors and controls, heat pumps and air conditioning equipment and many other electrical devices. -

Investigation of the Lightning Arrester Operation in Electric Power Distribution Network

Nigerian Journal of Technology (NIJOTECH) Vol. 37, No. 2, April 2018, pp. 490 – 497 Copyright© Faculty of Engineering, University of Nigeria, Nsukka, Print ISSN: 0331-8443, Electronic ISSN: 2467-8821 www.nijotech.com http://dx.doi.org/10.4314/njt.v37i2.27 INVESTIGATION OF THE LIGHTNING ARRESTER OPERATION IN ELECTRIC POWER DISTRIBUTION NETWORK P. O. Oluseyi1, *, T. O. Akinbulire2 and O. Amahian3 1, 2, 3 DEPARTMENT OF ELECTRICAL/ELECTRONICS ENGINEERING, UNIVERSITY OF LAGOS, LAGOS STATE. NIGERIA E-mail addresses: 1 [email protected] , 2 [email protected] , 3 [email protected] ABSTRACT Lightning phenomenon has resulted into several losses to both supply-side and load-side of the electricity infrastructure. Quite a handful of research has investigated strategies for its mitigation. This work is an application of the Fernandez-Diaz arrester model to the section of Eko Distribution network. The procedure involves simulation of the network in respect of the influence of the surges and surge arresters using MATLAB/SIMULINK. The study reveals that whenever lightning strikes, the resulting overvoltage causes distortion to the voltage waveform, as well as the current waveform. This indicates the presence of harmonics. Meanwhile, with the installation of the arresters, the overvoltage reduces by 86% at the nearest node of installation. However, at the other nodes within the same branch, the installed arrester attenuated the surge overvoltage by approximately 60%. This suggests that more arresters need to be installed at other nodes along the branch in order to eliminate the occurrence of overvoltage. Moreover, the study reveals that a surge arrester installed at one of the two branches of the network has negligible effect in attenuating voltage surge at the other branch of the same network. -

Lightning Protection for Telecommunication Stations Imp

Lightning protection for Telecommunication Stations Imp. Carret-Vène - Octobre 2006 ABB Lightning Protection Group 22, rue du 8 Mai 1945 95340 - Persan France Tel : +33 (0) 1 30 28 60 88 Fax : +33 (0) 1 30 28 60 79 Impacts on structures: direct effects ABB Soulé located in Bagnères-de- Lightning protection (strikes Bigorre (South West of France) has with indirect effects) for SKILLSseveral decades of experience, and uses HOW? telecommunication stations by its technological expertise to provide lightning arresters, is protection against lightning and applicable for all electrical overvoltage. networks. It is also compulsory In addition to up-to-date expertise with its to provide protection against global lightning protection offer (external lightning strikes with direct and internal), ABB Soulé now offers a effects by placing a lightning range of lightning conductors and arrester (near the top of the stations ? lightning arresters to protect a Telecom tower) for which the earthing site. device installed to be at the ABB Soulé also has a laboratory same potential as the earth of comprising several generators capable of the electrical network, will give testing all equipment under real a good path for the lightning conditions with different amplitude surge current from the entire currents, in order to optimize protection installation. solutions. The owner of the line is responsible for protecting the HV transformer and the LV circuit breaker: - either the energy distributor (EDF, Impacts public corporation, on electrical lines: others, etc.) indirect effect LESPS laboratory in Bagnères-de-Bigorre, France - or a large private Impacts subscriber / on the ground, How to protect Telecommunication to protect How consumer (tertiary potential rising from A recognized skill in lightning protection industry, others). -

The Crystal Valve Arrester Story

The Crystal Valve Arrester and Electric Supply Services Company Story In the first half of the 20th century The Electric Supply Services Co. (ESSCo) was a thriving manufacturing enterprise serving the electrical, railroad, and porcelain industry. The product that is of interest to me of course is the Crystal Valve Arrester that was used on distribution medium voltage systems. By the end of the 20th century, they were only known to collectors of antiques. Whatever happened to ESSCo is the question at hand. Was it bought out and its name lost in the history of another company? Did it fail as a business; did it change its name? Read on to learn some of the story. The main offices and factory of ESSC0 were located on the corner of North 17th and West Cambria St. in Philadelphia Pa. USA. Only 3 short miles from downtown Philly. My research so far has not revealed the founders or officers of the business. The only person I have been able to associate with this company was John Robert McFarlin a prolific design engineer who patented several arrester associated products for ESSCo from as early as 1918 and as late as 1950. More on John Robert McFarlin later. We know from a superb brochure published by ESSCo in 1935 titled “43 Years” that they proudly produced distribution arresters from 1892 until 1935. Other data suggest they produced arresters into the 1940s (perhaps even into the 50s). The last model of arrester they manufactured was called the Crystal Valve Arrester. It took its name from the fact that the Silicon Carbide (SiC) material used in the arrester was a crystalline in form, and the SiC acted as an electrical valve in its application. -

Concept and Application of Lightning Arrester for 11Kv Electric Power Systems Protection

Asian Journal of Basic Science & Research (AJBSR) Volume 2, Issue 1, Pages 35-49, January-March 2020 Concept and Application of Lightning Arrester for 11kV Electric Power Systems Protection Research Article Received: 22 November 2019 Accepted: 27 December 2019 Published: 23 January 2020 1 Uche C. Ogbuefi , Cajetan M. Abstract: The phenomenon of lightning is an exciting natural incident. However, its rate of 2 3 Nwosu & Cosmas U. Ogbuka occurrence can be as critical as it is electrifying. The magnitude of energy contained in lightning 1,2,3 Department of Electrical Engineering, strikes is very high and can be destructive. In order to prevent electric power equipment from University of Nigeria, Nsukka, Enugu State, Nigeria. lightning, protection schemes like the use of lightning rods, ground wires and surge diverters are put in place to curtail its effects on electric equipment. This device is used for the protection of Corresponding Author Author Email: substations equipment against high travelling waves, by arresting the abnormal high voltage spike [email protected] to the general mass of the earth devoid of affecting the continuity of supply. In this paper, a detailed design of surge diverter or lightning arrester for protection of electric power system is presented. 1. INTRODUCTION SOLIDWORKS software was utilized in this study to access the performance analysis and Lightning is unpredictable and it application of an 11kV valve-type surge diverter modelled after the IEEE lightning arrester model. Different lightning arrester models are presented. By Slight variation to the IEEE model, a 92% is the most destructive of all reduction in the lightning-induced voltage was recorded. -

Transient Lightning Protection for Electronic Measurement Devices

TRANSIENT LIGHTNING PROTECTION FOR ELECTRONIC MEASUREMENT DEVICES Patrick S. McCurdy Presented by: Dick McAdams Phoenix Contact Inc. P.O. Box 4100 Harrisburg, PA 17111-0100 INTRODUCTION LIGHTNING MAGNITUDE AND FREQUENCY Technology advances in the world of semiconductors and microprocessors are increasing at a breathtaking pace. Most of the continental United States experiences at least The density of transistor population on integrated circuits two cloud to ground flashes per square kilometer per has increased at a rate unimaginable just a few years ago. year. About one half of the United States will see three The advantages are many: faster data acquisition, real cloud to ground events per square kilometer per year. time control, and fully automated factories, to name a This is equivalent to about 10 discharges per square mile few. per year. An Isokeraunic map of thunderstorm days developed by ANSI/NFPA 780-1992 is shown in Figure Semiconductor technology is also prevalent in field #1. This shows the average number of thunderstorm days mounted instrumentation and electronic measurement per year by geographic region. A relationship can be devices. Unfortunately, a tradeoff to the increased made between thunderstorm days and flash density (i.e., performance is the susceptibility of these semiconductor the number of lightning-to-ground flashes in a specified devices to voltage and current transient events. The period over a certain area, expressed in flashes / km2 minimum results are unreliable instrumentation readings [Table 1]). and operation, with periodic failures. The worst case result is a completely destroyed measurement device. As can be seen, depending on the region, locations such as Tampa, Florida or Columbia, South Carolina can have Such power surges are often the work of mother nature. -

Surge Arresters: Applications and Selection 18/683 18.1 Surge Arresters and Blown-Off by the Force of the Gases Thus Produced

18/681 Surge arresters: applications and 18 selection Contents 18.1 Surge arresters 18/683 18.1.1 Gapped surge arresters 18/683 18.1.2 Gapless surge arresters 18/684 18.2 Electrical characteristics of a ZnO surge arrester 18/684 18.3 Basic insulation level (BIL) 18/687 18.4 Protective margins 18/688 18.4.1 Steepness (t1) of the FOW 18/688 18.4.2 Effect of discharge or co-ordinating current (In) on the protective level of an arrester 18/688 18.4.3 Margin for contingencies 18/688 18.5 Protective level of the a surge arrester 18/688 18.5.1 Reflection of the travelling waves 18/691 18.5.2 Surge transference through a transformer 18/694 18.5.3 Effect of resonance 18/699 18.6 Selection of a gapless surge arrester 18/699 18.6.1 TOV capability and selection of rated voltage, Vr 18/699 18.6.2 Selecting the protective level of the arrester 18/703 18.6.3 Required energy capability in kJ/kVr 18/706 18.7 Classification of arresters 18/707 18.8 Application of distribution class surge arresters 18/708 18.9 Pressure relief facility 18/709 18.10 Assessing the condition of an arrester 18/710 Relevant Standards 18/718 List of formulae used 18/718 Further Reading 18/719 Surge arresters: applications and selection 18/683 18.1 Surge arresters and blown-off by the force of the gases thus produced. The enclosure is so designed that after blowing off the arc it forcefully expels the gases into the When surge protection is considered necessary, surge atmosphere. -

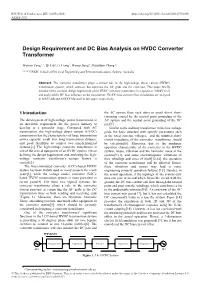

Design Requirement and DC Bias Analysis on HVDC Converter Transformer

E3S Web of Conferences 257, 01038 (2021) https://doi.org/10.1051/e3sconf/202125701038 AESEE 2021 Design Requirement and DC Bias Analysis on HVDC Converter Transformer Weijian Peng 1,*, Qi Liu2, Li Liang3, Wenqi Jiang4, Zhuoyuan Zhang 5 1,2,3,4,5UNSW, School of Electrical Engineering and Telecommunications, Sydney, Australia Abstract. The converter transformer plays a critical role in the high-voltage direct current (HVDC) transmission system, which connects but separates the AC grids and the converter. This paper briefly introduced the essential design requirement of the HVDC converter transformer in a system at ±800kV level and analyzed the DC bias influence on the transformer. The DC bias current effect simulations are analyzed in MATLAB and ANSYS Maxwell in this paper, respectively. 1 Introduction the AC system from each other to avoid direct short- circuiting caused by the neutral point grounding of the The development of high-voltage power transmission is AC system and the neutral point grounding of the DC an inevitable requirement for the power industry to part[7]. develop to a particular stage. Compared with AC Similar to the ordinary transformer in the low-voltage transmission, the high-voltage direct current (HVDC) grids, the basic structure with specific parameters such transmission has the characteristics of large transmission as the rated currents, voltages, and the minimal short- power capacity, small loss, long transmission distance, circuit impedance of the converter transformer should and good flexibility to connect two unsynchronized be calculated[8]. Moreover, due to the nonlinear systems.[1] The high-voltage converter transformer is operation characteristic of the converter in the HVDC one of the critical equipment of an HVDC system.