Intel Woodcrest: an Evaluation for Scientific Computing Philip C

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Fully-Buffered DIMM Memory Architectures: Understanding Mechanisms, Overheads and Scaling

Fully-Buffered DIMM Memory Architectures: Understanding Mechanisms, Overheads and Scaling Brinda Ganesh†, Aamer Jaleel‡, David Wang†, and Bruce Jacob† †University of Maryland, College Park, MD ‡VSSAD, Intel Corporation, Hudson, MA {brinda, blj}@eng.umd.edu Abstract Consequently the maximum number of DIMMs per channel in Performance gains in memory have traditionally been successive DRAM generations has been decreasing. SDRAM obtained by increasing memory bus widths and speeds. The channels have supported up to 8 DIMMs of memory, some diminishing returns of such techniques have led to the types of DDR channels support only 4 DIMMs, DDR2 channels proposal of an alternate architecture, the Fully-Buffered have but 2 DIMMs, and DDR3 channels are expected to support DIMM. This new standard replaces the conventional only a single DIMM. In addition the serpentine routing required for electrical path-length matching of the data wires becomes memory bus with a narrow, high-speed interface between the challenging as bus widths increase. For the bus widths of today, memory controller and the DIMMs. This paper examines the motherboard area occupied by a single channel is signifi- how traditional DDRx based memory controller policies for cant, complicating the task of adding capacity by increasing the scheduling and row buffer management perform on a Fully- number of channels. To address these scalability issues, an alter- Buffered DIMM memory architecture. The split-bus nate DRAM technology, the Fully Buffered Dual Inline Mem- architecture used by FBDIMM systems results in an average ory Module (FBDIMM) [2] has been introduced. improvement of 7% in latency and 10% in bandwidth at The FBDIMM memory architecture replaces the shared par- higher utilizations. -

Architectural Techniques to Enhance DRAM Scaling

Architectural Techniques to Enhance DRAM Scaling Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical and Computer Engineering Yoongu Kim B.S., Electrical Engineering, Seoul National University Carnegie Mellon University Pittsburgh, PA June, 2015 Abstract For decades, main memory has enjoyed the continuous scaling of its physical substrate: DRAM (Dynamic Random Access Memory). But now, DRAM scaling has reached a thresh- old where DRAM cells cannot be made smaller without jeopardizing their robustness. This thesis identifies two specific challenges to DRAM scaling, and presents architectural tech- niques to overcome them. First, DRAM cells are becoming less reliable. As DRAM process technology scales down to smaller dimensions, it is more likely for DRAM cells to electrically interfere with each other’s operation. We confirm this by exposing the vulnerability of the latest DRAM chips to a reliability problem called disturbance errors. By reading repeatedly from the same cell in DRAM, we show that it is possible to corrupt the data stored in nearby cells. We demonstrate this phenomenon on Intel and AMD systems using a malicious program that generates many DRAM accesses. We provide an extensive characterization of the errors, as well as their behavior, using a custom-built testing platform. After examining various potential ways of addressing the problem, we propose a low-overhead solution that effec- tively prevents the errors through a collaborative effort between the DRAM chips and the DRAM controller. Second, DRAM cells are becoming slower due to worsening variation in DRAM process technology. To alleviate the latency bottleneck, we propose to unlock fine-grained paral- lelism within a DRAM chip so that many accesses can be served at the same time. -

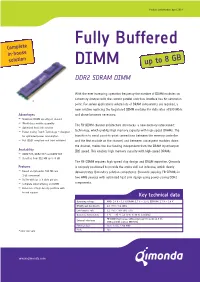

Fully Buffered Dimms for Server

07137_Fully_Buffered_DIMM.qxd 22.03.2007 12:08 Uhr Seite 1 Product Information April 2007 Fully Buffered Complete in-house solution DIMM up to 8 GB DDR2 SDRAM DIMM With the ever increasing operation frequency the number of DIMM modules on a memory channel with the current parallel stub-bus interface has hit saturation * point. For server applications where lots of DRAM components are required, a new solution replacing the Registered DIMM modules for data rates of 533 Mb/s Advantages and above becomes necessary. s Maximum DRAM density per channel s World-class module assembly The FB-DIMM channel architecture introduces a new memory interconnect s Optimized heat sink solution s Power Saving Trench Technology – designed technology, which enables high memory capacity with high-speed DRAMs. The for optimized power consumption transition to serial point-to-point connections between the memory controller s Full JEDEC compliant and Intel validated and the first module on the channel, and between subsequent modules down the channel, makes the bus-loading independent from the DRAM input/output Availability (IO) speed. This enables high memory capacity with high-speed DRAMs. s DDR2-533, DDR2-667 and DDR2-800 s Densities from 512 MB up to 8 GB The FB-DIMM requires high-speed chip design and DRAM expertise. Qimonda Features is uniquely positioned to provide the entire skill set in-house, which clearly s Based on Qimonda’s 512 Mb and demonstrates Qimonda’s solution competence. Qimonda supplies FB-DIMMs in 1 Gb component two AMB sources with optimized heat sink design using power-saving DDR2 s Buffer with up to 6 Gb/s per pin s Complete data buffering on DIMM components. -

PGI Fortran Guide

PGI® User’s Guide Parallel Fortran, C and C++ for Scientists and Engineers The Portland Group® STMicroelectronics Two Centerpointe Drive Lake Oswego, OR 97035 While every precaution has been taken in the preparation of this document, The Portland Group® (PGI®), a wholly-owned subsidiary of STMicroelectronics, Inc., makes no warranty for the use of its products and assumes no responsibility for any errors that may appear, or for damages resulting from the use of the information contained herein. The Portland Group ® retains the right to make changes to this information at any time, without notice. The software described in this document is distributed under license from STMicroelectronics, Inc. and/or The Portland Group® and may be used or copied only in accordance with the terms of the license agreement ("EULA"). No part of this document may be reproduced or transmitted in any form or by any means, for any purpose other than the purchaser's or the end user's personal use without the express written permission of STMicroelectronics, Inc and/or The Portland Group®. Many of the designations used by manufacturers and sellers to distinguish their products are claimed as trademarks. Where those designations appear in this manual, STMicroelectronics was aware of a trademark claim. The designations have been printed in caps or initial caps. PGF95, PGF90, and PGI Unified Binary are trademarks; and PGI, PGHPF, PGF77, PGCC, PGC++, PGI Visual Fortran, PVF, Cluster Development Kit, PGPROF, PGDBG, and The Portland Group are registered trademarks of The Portland Group Incorporated. PGI CDK is a registered trademark of STMicroelectronics. *Other brands and names are the property of their respective owners. -

The Portland Group

® PGI Compiler User's Guide Parallel Fortran, C and C++ for Scientists and Engineers Release 2011 The Portland Group While every precaution has been taken in the preparation of this document, The Portland Group® (PGI®), a wholly-owned subsidiary of STMicroelectronics, Inc., makes no warranty for the use of its products and assumes no responsibility for any errors that may appear, or for damages resulting from the use of the information contained herein. The Portland Group retains the right to make changes to this information at any time, without notice. The software described in this document is distributed under license from STMicroelectronics and/or The Portland Group and may be used or copied only in accordance with the terms of the end-user license agreement ("EULA"). PGI Workstation, PGI Server, PGI Accelerator, PGF95, PGF90, PGFORTRAN, and PGI Unified Binary are trademarks; and PGI, PGHPF, PGF77, PGCC, PGC++, PGI Visual Fortran, PVF, PGI CDK, Cluster Development Kit, PGPROF, PGDBG, and The Portland Group are registered trademarks of The Portland Group Incorporated. Other brands and names are property of their respective owners. No part of this document may be reproduced or transmitted in any form or by any means, for any purpose other than the purchaser's or the end user's personal use without the express written permission of STMicroelectronics and/or The Portland Group. PGI® Compiler User’s Guide Copyright © 2010-2011 STMicroelectronics, Inc. All rights reserved. Printed in the United States of America First Printing: Release 2011, 11.0, December, 2010 Second Printing: Release 2011, 11.1, January, 2011 Third Printing: Release 2011, 11.2, February, 2011 Fourth Printing: Release 2011, 11.3, March, 2011 Fourth Printing: Release 2011, 11.4, April, 2011 Technical support: [email protected] Sales: [email protected] Web: www.pgroup.com ID: 1196151 Contents Preface ..................................................................................................................................... -

The Portland Group

® PGI Compiler Reference Manual Parallel Fortran, C and C++ for Scientists and Engineers Release 2011 The Portland Group While every precaution has been taken in the preparation of this document, The Portland Group® (PGI®), a wholly-owned subsidiary of STMicroelectronics, Inc., makes no warranty for the use of its products and assumes no responsibility for any errors that may appear, or for damages resulting from the use of the information contained herein. The Portland Group retains the right to make changes to this information at any time, without notice. The software described in this document is distributed under license from STMicroelectronics and/or The Portland Group and may be used or copied only in accordance with the terms of the end-user license agreement ("EULA"). PGI Workstation, PGI Server, PGI Accelerator, PGF95, PGF90, PGFORTRAN, and PGI Unified Binary are trademarks; and PGI, PGHPF, PGF77, PGCC, PGC++, PGI Visual Fortran, PVF, PGI CDK, Cluster Development Kit, PGPROF, PGDBG, and The Portland Group are registered trademarks of The Portland Group Incorporated. Other brands and names are property of their respective owners. No part of this document may be reproduced or transmitted in any form or by any means, for any purpose other than the purchaser's or the end user's personal use without the express written permission of STMicroelectronics and/or The Portland Group. PGI® Compiler Reference Manual Copyright © 2010-2011 STMicroelectronics, Inc. All rights reserved. Printed in the United States of America First printing: Release 2011, 11.0, December, 2010 Second Printing: Release 2011, 11.1, January 2011 Third Printing: Release 2011, 11.3, March 2011 Fourth Printing: Release 2011, 11.4, April 2011 Fifth Printing: Release 2011, 11.5, May 2011 Technical support: [email protected] Sales: [email protected] Web: www.pgroup.com ID: 111162228 Contents Preface ..................................................................................................................................... -

The Portland Group

PGI Visual Fortran® 2013 Installation Guide Version 13.5 The Portland Group While every precaution has been taken in the preparation of this document, The Portland Group® (PGI®), a wholly-owned subsidiary of STMicroelectronics, Inc., makes no warranty for the use of its products and assumes no responsibility for any errors that may appear, or for damages resulting from the use of the information contained herein. The Portland Group retains the right to make changes to this information at any time, without notice. The software described in this document is distributed under license from STMicroelectronics and/or The Portland Group and may be used or copied only in accordance with the terms of the license agreement ("EULA"). PGI Workstation, PGI Server, PGI Accelerator, PGF95, PGF90, PGFORTRAN, and PGI Unified Binary are trademarks; and PGI, PGHPF, PGF77, PGCC, PGC++, PGI Visual Fortran, PVF, PGI CDK, Cluster Development Kit, PGPROF, PGDBG, and The Portland Group are registered trademarks of The Portland Group Incorporated. Other brands and names are property of their respective owners. No part of this document may be reproduced or transmitted in any form or by any means, for any purpose other than the purchaser's or the end user's personal use without the express written permission of STMicroelectronics and/or The Portland Group. PVF® Installation Guide Copyright © 2010-2013 STMicroelectronics, Inc. All rights reserved. Printed in the United States of America First Printing: Release 2013, version 13.1, January 2013 Second Printing: Release 2013, version 13.2, February 2013 Third Printing: Release 2013, version 13.3, March 2013 Fourth Printing: Release 2013, version 13.4, April 2013 Fourth Printing: Release 2013, version 13.5, May 2013 Technical support: [email protected] Sales: [email protected] Web: www.pgroup.com ID: 07183206 Contents 1. -

The Portland Group

PGI® 2013 Release Notes Version 13.3 The Portland Group While every precaution has been taken in the preparation of this document, The Portland Group® (PGI®) makes no warranty for the use of its products and assumes no responsibility for any errors that may appear, or for damages resulting from the use of the information contained herein. The Portland Group retains the right to make changes to this information at any time, without notice. The software described in this document is distributed under license from The Portland Group and/or its licensors and may be used or copied only in accordance with the terms of the end-user license agreement ("EULA"). PGI Workstation, PGI Server, PGI Accelerator, PGF95, PGF90, PGFORTRAN, PGI Unified Binary, and PGCL are trademarks; and PGI, PGHPF, PGF77, PGCC, PGC++, PGI Visual Fortran, PVF, PGI CDK, Cluster Development Kit, PGPROF, PGDBG, and The Portland Group are registered trademarks of The Portland Group Incorporated. Other brands and names are property of their respective owners. No part of this document may be reproduced or transmitted in any form or by any means, for any purpose other than the purchaser's or the end user's personal use without the express written permission of The Portland Group, Inc. PGI® 2013 Release Notes Copyright © 2013 The Portland Group, Inc. and STMicroelectronics, Inc. All rights reserved. Printed in the United States of America First Printing: Release 2013, version 13.1, January 2013 Second Printing: Release 2013, version 13.2, February 2013 Third Printing: Release 2013, version 13.3, March 2013 Technical support: [email protected] Sales: [email protected] Web: www.pgroup.com ID: 07135184 Contents 1. -

SBA-7121M-T1 Blade Module User's Manual

SBA-7121M-T1 Blade Module User’s Manual Revison 1.0c SBA-7121M-T1 Blade Module User’s Manual The information in this User’s Manual has been carefully reviewed and is believed to be accurate. The vendor assumes no responsibility for any inaccuracies that may be contained in this document, makes no commitment to update or to keep current the information in this manual, or to notify any person or organization of the updates. Please Note: For the most up-to-date version of this manual, please see our web site at www.supermicro.com. Super Micro Computer, Inc. ("Supermicro") reserves the right to make changes to the product described in this manual at any time and without notice. This product, including software and documentation, is the property of Supermicro and/or its licensors, and is supplied only under a license. Any use or reproduction of this product is not allowed, except as expressly permitted by the terms of said license. IN NO EVENT WILL SUPERMICRO BE LIABLE FOR DIRECT, INDIRECT, SPECIAL, INCIDENTAL, SPECULATIVE OR CONSEQUENTIAL DAMAGES ARISING FROM THE USE OR INABILITY TO USE THIS PRODUCT OR DOCUMENTATION, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. IN PARTICULAR, SUPERMICRO SHALL NOT HAVE LIABILITY FOR ANY HARDWARE, SOFTWARE, OR DATA STORED OR USED WITH THE PRODUCT, INCLUDING THE COSTS OF REPAIRING, REPLACING, INTEGRATING, INSTALLING OR RECOVERING SUCH HARDWARE, SOFTWARE, OR DATA. Any disputes arising between manufacturer and customer shall be governed by the laws of Santa Clara County in the State of California, USA. The State of California, County of Santa Clara shall be the exclusive venue for the resolution of any such disputes. -

Tuning C++ Applications for the Latest Generation X64 Processors with PGI Compilers and Tools

Tuning C++ Applications for the Latest Generation x64 Processors with PGI Compilers and Tools Douglas Doerfler and David Hensinger Sandia National Laboratories Brent Leback and Douglas Miles The Portland Group (PGI) ABSTRACT: At CUG 2006, a cache oblivious implementation of a two dimensional Lagrangian hydrodynamics model of a single ideal gas material was presented. This paper presents further optimizations to this C++ application to allow packed, consecutive-element storage of vectors, some restructuring of loops containing neighborhood operations, and adding type qualifiers to some C++ pointer declarations to improve performance. In addition to restructuring of the application, analysis of the compiler-generated code resulted in improvements to the latest PGI C++ compiler in the area of loop-carried redundancy elimination, resolution of pointer aliasing conflicts, and vectorization of loops containing min and max reductions. These restructuring and compiler optimization efforts by PGI and Sandia have resulted in application speedups of 1.25 to 1.80 on the latest generation of x64 processors. KEYWORDS: Compiler, C, C++, Optimization, Vectorization, Performance Analysis, AMD Opteron™, Intel Core™ 2, Micro-architecture vector or SIMD units to increase FLOP rates in general 1. Introduction purpose processors. While first-generation AMD and Intel 64-bit x86 Although modern compilers do an admirable job of (x64) processors contain 128-bit wide Streaming SIMD optimization when provided with nothing other than the Extensions (SSE) registers, their 64-bit data paths and “–fast” switch, many times there are still significant floating-point units limit the performance benefit of performance gains to be obtained with detailed analysis vectorizing double-precision loops. -

Supercomputing in Plain English Exercise #3: Arithmetic Operations in This Exercise, We’Ll Use the Same Conventions and Commands As in Exercises #1 and #2

Supercomputing in Plain English Exercise #3: Arithmetic Operations In this exercise, we’ll use the same conventions and commands as in Exercises #1 and #2. You should refer back to the Exercise #1 and #2 descriptions for details on various Unix commands. You MUST complete Exercises #1 and #2 BEFORE starting Exercise #3. For Exercise #3, YOU ARE EXPECTED TO KNOW HOW TO ACCOMPLISH BASIC TASKS, based on your experiences with Exercises #1 and #2. In the exercise, you’ll benchmark various arithmetic operations, using various compilers and levels of compiler optimization. Specifically, you’ll benchmark using the following compilers: the GNU Fortran compiler, gfortran, for various optimization levels; the Intel Fortran compiler, ifort, for various optimization levels; the Portland Group Fortran compiler, pgf90, for various optimization levels. Here are the steps for this exercise: 1. Log in to the Linux cluster supercomputer (sooner.oscer.ou.edu). 2. Copy the ArithmeticOperations directory: % cp -r ~hneeman/SIPE2011_exercises/ArithmeticOperations/ ~/SIPE2011_exercises/ 3. Choose which language you want to use (C or Fortran90), and cd into the appropriate directory: % cd ~/SIPE2011_exercises/ArithmeticOperations/C/ OR: % cd ~/SIPE2011_exercises/ArithmeticOperations/Fortran90/ 4. Edit the batch script arithmetic_operations.bsub so that it contains your username and your e-mail address. 5. Compile, using the shell script named make_cmd (a shell script is a file containing a sequence of Unix commands), which in turn invokes the make command: % make_cmd If that doesn’t work, try this: % ./make_cmd 6. Submit the batch job: % bsub < arithmetic_operations.bsub 7. Once the batch job completes, examine the several output files to see the timings for your runs with executables created by the various compilers under the various levels of optimization. -

PGI Visual Fortran Reference Manual

® PGI Visual Fortran Reference Manual Parallel Fortran for Scientists and Engineers Release 2011 The Portland Group While every precaution has been taken in the preparation of this document, The Portland Group® (PGI®), a wholly-owned subsidiary of STMicroelectronics, Inc., makes no warranty for the use of its products and assumes no responsibility for any errors that may appear, or for damages resulting from the use of the information contained herein. The Portland Group retains the right to make changes to this information at any time, without notice. The software described in this document is distributed under license from STMicroelectronics and/or The Portland Group and may be used or copied only in accordance with the terms of the end-user license agreement ("EULA"). PGI Workstation, PGI Server, PGI Accelerator, PGF95, PGF90, PGFORTRAN, and PGI Unified Binary are trademarks; and PGI, PGHPF, PGF77, PGCC, PGC++, PGI Visual Fortran, PVF, PGI CDK, Cluster Development Kit, PGPROF, PGDBG, and The Portland Group are registered trademarks of The Portland Group Incorporated. Other brands and names are property of their respective owners. No part of this document may be reproduced or transmitted in any form or by any means, for any purpose other than the purchaser's or the end user's personal use without the express written permission of STMicroelectronics and/or The Portland Group. PGI® Visual Fortran Reference Manual Copyright © 2010-2012 STMicroelectronics, Inc. All rights reserved. Printed in the United States of America First printing: