A Fully Integrated CMOS Receiver by Dan Shi a Dissertation Submitted in Partial Fulfillment of the Requirements for the Degree O

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Bull Electrical-Jun03.Qxd

Constructional Project PRACTICAL RADIO CIRCUITS RAYMOND HAIGH Part 1: Introduction, Simple Receivers and a Headphone Amp. Dispelling the mysteries of radio. This new series features a variety of practical circuits for the set builder and experimenter. owards the end of the 19th century, physicist who first demonstrated the exis- (V. Poulsen), and by mechanical alterna- sending a radio signal a few hun- tence of electromagnetic waves in 1886. tors (E. Alexanderson). Semiconductors T dred yards was considered a major Before the valve era, radio frequency now play an increasing role, but valves are achievement. At the close of the 20th, man oscillations were generated by using an still used in high-power transmitters. was communicating with space probes at electrical discharge to shock-excite a tuned As their name suggests, the waves com- the outermost edge of the solar system. circuit (H. Hertz and G. Marconi), by the prise an electric and a magnetic field No other area of science and technology negative resistance of an electric arc which are aligned at right angles to one has affected the lives of people another. The electric field is more completely. And because it formed by the rapid voltage fluctu- is so commonplace and afford- ations (oscillations) in the aerial. able, it is accepted without a sec- Current fluctuations create the ond thought. The millions who magnetic field. enjoy it, use it, even those whose lives depend upon it, often have HITCHING A RIDE little more than a vague notion of Electromagnetic waves cannot, A) how it works. by themselves, convey any informa- This series of articles will view tion. -

Regenerative Radio Receivers 2/1/16, 7:47 PM

regenerative radio receivers 2/1/16, 7:47 PM WWW.ELECTRONICS-TUTORIALS.COM Recommend 28 Share 28 4 •NEW! ‣ - Amazon Electronic Component Packs. Check out the Amazon Electronic Component Packs page. What are the basics of regenerative radio receivers? Foreword - by Ian C. Purdie VK2TIP A regenerative radio receiver is unsurpassed in comparable simplicity, weak signal reception, inherent noise-limiting and agc action and, freedom from overloading and spurious responses. The regenerative radio receiver or, even super-regenerative radio receiver or, "regen" if you prefer, are basically oscillating detector receivers. They are simple detectors which may be used for cw or ssb when adjusted for oscillation or a-m phone when set just below point of oscillation. In contrast direct conversion receivers use a separate hetrodyne oscillator to produce a signal. In the comprehensive electronic project presented here, Charles Kitchin, N1TEV has provided us with a three stage receiver project which overcomes some of the limitations of this type of receiver, principally the provision of an rf amplifier ahead of the detector. We are indeed particularly grateful to "Chuck" Kitchin, a well noted technical author, for sharing this very valuable material with us to use, learn, experiment and above all, to enjoy. Introduction to the regenerative radio receiver project designed by "Chuck" Kitchin, N1TEV The radio described here is a two band short wave receiver which is both very sensitive and very portable. It receives AM, single sideband (SSB), and CW (code) signals over a frequency range of approximately 3.5 to 12MHz. This includes the 80, 40, and 30 meter Ham bands plus several international short wave bands. -

Build an Old Time One-Valve Radio T

•~ a.. e e Ifito .ega'3a, . tr Ssc~ . a~:r"..,`'r"'~g~~ t.~.= ~ y~~..i•'`'E~;sr,:~ .?-~`.r ;~'~I:i'Y ~~":'-:2i:5'-~'r:" *: ap~ i d -.t e -•i' e'•,y`. z'a--'~ ~a.r •~`,`'t ,'-yerk',t"3-c .rLt ~`u"r. ,~,`.~f'F' 06***104r"' G: _•ad2r. r,`r,*•r--,.x-00-fti;,s -,yr-4.o o-+J-0,0_4 03-c?'rv7-F * Special `nostalgia' project: BUILD AN OLD TIME ONE-VALVE RADIO T There's a lot of interest nowadays in building simple valve-based radio sets, of the type that were popular from the 1920s right up until the 1960s. Here's the first of two articles which give all the information you'll need to construct an authentic one-valver starting with a basic `grid-leak' set and progressing to a regenerative circuit with surprisingly good performance. Enough information is given to allow you to use almost any old valve or other components to hand. by PETER LAUGHTON Cleaning out my radio `shack' (read had, and how much I'd learned. This, cussion is the following project. mess) the other day, I came across a along with several recent Letters to The circuits described can be built number of radio receivers that I con- the Editor asking for more vintage using almost any combination of com- structed years ago based on valves, radio projects, resulted in me talking ponents, even from junked valve TV and remembered how much fun I'd to Jim Rowe, and the result of that dis- sets. -

Man of High Fidelity

Man of High Fidelity: EDWIN HOWARD ARMSTRONG A Biography – By Lawrence Lessing With a new forward by the author Page iii Pratt DISCLAIMER DISCLAIMER TO THIS SCANNED AND OCR PROCESSED COPY This PDF COPY is for use at Pratt Institute for Educational Purposes Only I affirm that sufficient print copies of the original Bantam Book Paperback are in stock in ARC E-08 that would more than adequately cover a full class use of the text. HOWEVER, due to the fact that the 1969 text is no longer in publication, complicated by the fact that these copies are forty-four (44) years old and in a very fragile condition, this PDF version of the text was created for student use in the Department of Mathematics and Science. - Professor Charles Rubenstein, January 2013 Man of High Fidelity: Edwin Howard Armstrong EDWIN HOWARD ARMSTRONG Was the last – and perhaps the least known – of the great American Inventors. Without his major contributions, the broadcasting industry would not be what it is today, and there would be no FM radio. But in time of mushrooming industry and mammoth corporations, the recognition of individual genius is often refused, and always minimized. This is the extraordinary true story of the discovery of high fidelity, the brilliant man and his devoted wife who battled against tremendous odds to have it adopted, and their long fight against the corporations that challenged their right to the credit and rewards. Mrs. Armstrong finally ensured that right nearly ten years after her husband’s death. Page i Cataloging Information Page This low-priced Bantam Book has been completely reset in a type face designed for easy reading, and was printed from new plates. -

SOME RECENT DEVELOPMENTS of REGENERATIVE Fication Which Is Based Fundamentally on Regeneration, but Which Existing Therein) Is E

SOME RECENT DEVELOPMENTS OF REGENERATIVE CIRCUITS* BY EDWIN H. ARMSTRONG (MARCELLUS HARTLEY RESEARCH LABORATORY, COLUMBIA UNIVERSITY, NEW YORK) It is the purpose of this paper to describe a method of ampli- fication which is based fundamentally on regeneration, but which involves the application of a principle and the attainment of a result which it is believed is new. This new result is obtained by the extension of regeneration into a field which lies beyond that hitherto considered its theoretical limit, and the process of amplification is therefore termed super-regeneration. Before proceeding with a description of this method it is in order to consider a few fundamental facts about regenerative circuits. It is well known that the effect of regeneration (that is, the supplying of energy to a circuit to reinforce the oscillations existing therein) is equivalent to introducing a negative resistance reaction in the circuit, which neutralizes positive resistance reaction, and thereby reduces the effective resistance of the cir- cuit. There are three conceivable relations between the nega- tive and positive resistances: namely-the negative resistance introduced may be less than the positive resistance, it may be equal to the positive resistance, or it may be greater than the positive resistance of the circuit. We will consider what occurs in a regenerative circuit con- taining inductance and capacity when an alternating electro- motive force of the resonant frequency is suddenly impressed for each of the three cases. In the first case (when the negative resistance is less than the positive), the free and forced oscillations have a maximum amplitude equal to the impnressed electomotive force over the effective resistance, and the free oscillation has a damping determined by this effective resistance. -

Edwin H. Armstrong Papers

Edwin H. Armstrong papers 1981.4 Finding aid prepared by Sarah Leu and Jack McCarthy through the Historical Society of Pennsylvania's Hidden Collections Initiative for Pennsylvania Small Archival Repositories. Last updated on September 12, 2016. The Historical and Interpretive Collections of The Franklin Institute Edwin H. Armstrong papers Table of Contents Summary Information....................................................................................................................................3 Biography/History..........................................................................................................................................4 Scope and Contents..................................................................................................................................... 10 Administrative Information......................................................................................................................... 11 Related Materials......................................................................................................................................... 12 Controlled Access Headings........................................................................................................................12 - Page 2 - Edwin H. Armstrong papers Summary Information Repository The Historical and Interpretive Collections of The Franklin Institute Creator Armstrong, Edwin H. (Edwin Howard), 1890-1954 Title Edwin H. Armstrong papers Call number 1981.4 Date [inclusive] 1909-1956 Extent -

Communications Frequency Based on Surface Acoustic

- (1) - COMMUNICATIONS FREQUENCY BASED ON SURFACE ACOUSTIC WAVE OSCILLATORS by ICassirn Muhawi Hussain B.Sc. (E.Epg.) A thesis submitted to the Faculty of Science of the University of Edinburgh, for the degree of Doctor of Philosophy Department of Electrical Engineering July 1978 .1Fk% (4' - (ii) T ABSTRACT Surface Acoustic Wave (SAW) -controlled oscillators possess many features which make them attractive as frequency sources in communications applications. This thesis deals with SAW oscillators, both resonator and delay stabilised, and their incorporation in communications synthesisers modules intended primarily for mobile radio applications. A review of SAW technology and the theory and design of SAW controlled oscillators together with related topics on frequency synthesis techniques is included. A SAW resonator-based personal radio-telephone module is described. This module demonstrates improved performance over existing commercial equipment. VHF and UHF multi-channel digital frequency synthesisers in which SAW delay line oscillators were successfully employed as frequency sources are also presented. Finally, a SAW based UHF Gemini synthesiser is demonstrated. This module is capable of fast switching, a feature of particular interest in frequency-hopped communications. All these modules are designed using the indirect frequency synthesis approach, in which the medium and long term stabilities of the SAW oscillators are cont- rolled by a highly stable crystal reference. 7 - (iv) - ACKNOWLEDGEMENTS I would like to express my sincere gratitude to Professor J H Collins, Dr P M Grant and Dr J H Hannah for their supervision and kind help, without which this work would not have reached this level. I gratefully acknowledge the financial support of the Iraqi Government (Ministry of Defence). -

1 a Stuoy of the Feasibility of Designing a Super

1 A STUOY OF THE FEASIBILITY OF DESIGNING A SUPER-REGENERATIVE RECEIVER TO MEET CERTAIN CRITICAL RE~Urn.EMENTS Thaddeus Francis Kycia, B.Sc. A thesis submitted to the Faculty of Graduate Studies and Research, McGill University, in partial fulfilment of the requirements ror the degree of Master of Science. ABSTRACT A super-regenerative reeeiver has been designed for linear mode operation in a band from 455 Mc ./see. to 510 Me ./see. For 1inear mode operation it was neeessary to use automatie gain stabi1ization, whieh a1so kept the oscillator output pulses at a steady amplitude. The reeeiver was constructed, having a band-width of 630 Ke./see and a noise figure of 20 db. The experimenta1 resu1ts were in good agreement with the theoretiea1 estimates, and numerical values for eomparison are provided wherever possible. The reeeiver ean deteet a minimum signal of 1.5~volts, and it therefore IOOre than meets the sensitivity recpirements for use as a deteetor in a l.I.h.f. "bridge". ACKNOWLEOOEMENTS The writer wishes to express his appreciation to Dr. J.R. Whitehead who originated the project and under whose direction i t was carried out; to Dr. H. G.I. ivatson for allowing the use of his laboratory equipment and workshop, and to Mr. W. Avarlaid, Mr. B. Meunier, Mr. M. Kingsmill, and the staif of the Physics building for their kind cooperation. Special thank s are due to Dr. T. w. h. East for hi s frequent assistance and advice during both the project and the writing of this thesis. The writer is also indebted to the Defence Research Board, whose financial assistance made this work possible. -

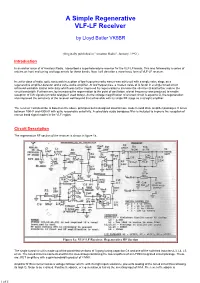

A Simple Regenerative VLF-LF Receiver

A Simple Regenerative VLF-LF Receiver by Lloyd Butler VK5BR (Originally published in "Amateur Radio", January, 1992 ) Introduction In an earlier issue of of Amateur Radio, I described a superheterodyne receiver for the VLF-LF bands, This was followed by a series of articles on front end tuning and loop aerials for these bands. Now I will describe a more basic form of VLF-LF receiver. In earlier days of radio, quite successful reception of low frequency radio waves was achieved with a single valve stage as a regenerative amplifier-detector and a valve audio amplifier. At low frequencies, a modest value of Q factor in a single tuned circuit achieved workable station selectivity which was further improved by regeneration to increase the effective Q and further reduce the circuit bandwidth. Furthermore, by increasing the regeneration to the point of oscillation, a beat frequency was produced to enable reception of CW signals (or radio teletype if used today). As the voltage magnification of a tuned circuit is equal to Q, the regeneration also improved the sensitivity of the receiver well beyond that achievable with its single RF stage as a straight amplifier. The receiver I will describe is based on the above principles but is designed around more modern solid state amplifier packages. It tunes between 10kHz and 430kHz with quite reasonable selectivity. A selectable audio bandpass filter is included to improve the reception of narrow band signal modes in the VLF region. Circuit Description The regenerative RF section of the receiver is shown in figure 1a. Figure 1a: VLF-LF Receiver, Regenerative RF Section The single tuned circuit is made up of the paralleled sections of 3 gang tuning capacitor C8 and one of the switched inductors L3, L4, L5, or L6. -

When 1 Think Back

When 1 Think Back... by Neville Williams Reader comments on the past, and Superregen. receivers in a new light Faced with an assortment of letters and phone calls prompted by past instalments of this column, it is fitting that I should interrupt the present series on vintage receiver design to acknowledge readers' comments and contributions to do with the history of electronics. Of special interest is information about a little-known major wartime role of superregenerative receivers. One thing that stands out from readers' Bob inquired as to whether we could Relevant to Bob Cooper's quest, we letters is that no one writer or source has help. Yes, we could, because Ross Hull had to be careful not to confuse the a monopoly on historical information. had been the first pioneer to be featured various wavebands, which were Mention almost any subject, it seems, in the series, back in February 1989. It so described in different ways during Ross and someone comes up with spontaneous happened because Ross had served brief- Hull's lifetime. personal recollections — or a clipping or ly as Technical Editor of our forerunner Transmissions in the present broadcast article that didn't make it into accessible Wireless Weekly. band were originally classified as 'short reference files. In the absence of any known biog- wave', as distinct from those on 'long It is saddening to contemplate, with raphy, we had been able to piece together waves' — around 1000m or 300kHz. hindsight, how much other electronics a reasonably cohesive story based on They were later redefined as 'medium history must already have been lost with published references to his activities, waves' with 'short waves' then signifying the passing of industry pioneers, along deduction from his articles and the fading HF (high frequency) channels up to with their dusty old books and papers recollections of some who remembered around 10 metres or 30MHz. -

THE SUPER-HETERODYNE-ITS ORIGIN, DEVELOP- Direction-Finding Service in the Signal Corps of the American Receiver, Which, with Ou

THE SUPER-HETERODYNE-ITS ORIGIN, DEVELOP- MENT, AND SOME RECENT IMPROVEMENTS* BY EDWIN H. ARMSTRONG (MARCELLUS HARTLEY RESEARCH LABORATORY, COLUMBIA UNIVERSITY NEW YORK) The purpose of this paper is to describe the development of the super-heterodyne receiver from a wartime invention, primar- ily intended for the exceedingly important radio telegraphic direction-finding service in the Signal Corps of the American Expeditionary Force, into a type of household broadcasting receiver, which, with our present vision, appears likely to become standard. The invention of the super-heterodyne dates back to the early part"of 1918. The full technical details of this system were made public in the Fall of 1919.1 Since that time it has been widely used in experimental work and is responsible for many of the recent accomplishments in long distance reception from broad- casting stations. While the superiority of its performance over all other forms of receivers was unquestioned, very many dif- ficulties rendered it unsuitable for use by the general public and confined it to the hands of engineers and skilled amateurs. Years of concentrated effort from many different sources have pro- duced improvements in vacuum tubes, in transformer construc- tion, and in the circuits of the super-heterodyne itself, with the result that at the beginning of the present month there has been made available for the general public a super-heterodyne re- ceiver which meets the requirements of household use. It is a peculiar circumstance that this invention was a direct outgrowth to meet a very important problem confronting the American Expeditionary Force. This problem was the reception of extremely weak spark signals of frequencies varying from about 500,000 cycles to 3,000,000 cycles, with an absolute minimum of adjustments to enable rapid change of wave length. -

Some Recent Developments of Regenerative Circuits* by Edwin H

SOME RECENT DEVELOPMENTS OF REGENERATIVE CIRCUITS* BY EDWIN H. ARMSTRONG (MARCELLUS HARTLEY RESEARCH LABORATORY, COLUMBIA UNIVERSITY, NEW YORK) It is the purpose of this paper to describe a method of ampli- fication which is based fundamentally on regeneration, but which involves the application of a principle and the attainment of a result which it is believed is new. This new result is obtained by the extension of regeneration into a field which lies beyond that hitherto considered its theoretical limit, and the process of amplification is therefore termed super-regeneration. Before proceeding with a description of this method it is in order to consider a few fundamental facts about regenerative circuits. It is well known that the effect of regeneration (that is, the supplying of energy to a circuit to reinforce the oscillations existing therein) is equivalent to introducing a negative resistance reaction in the circuit, which neutralizes positive resistance reaction, and thereby reduces the effective resistance of the cir- cuit. There are three conceivable relations between the nega- tive and positive resistances: namely-the negative resistance introduced may be less than the positive resistance, it may be equal to the positive resistance, or it may be greater than the positive resistance of the circuit. We will consider what occurs in a regenerative circuit con- taining inductance and capacity when an alternating electro- motive force of the resonant frequency is suddenly impressed for each of the three cases. In the first case (when the negative resistance is less than the positive), the free and forced oscillations have a maximum amplitude equal to the impnressed electomotive force over the effective resistance, and the free oscillation has a damping determined by this effective resistance.