Esl Wallchart

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

EP Activity Report 2014

EUROPRACTICE IC SERVICE THE RIGHT COCKTAIL OF ASIC SERVICES EUROPRACTICE IC SERVICE OFFERS YOU A PROVEN ROUTE TO ASICS THAT FEATURES: • Low-cost ASIC prototyping • Flexible access to silicon capacity for small and medium volume production quantities • Partnerships with leading world-class foundries, assembly and testhouses • Wide choice of IC technologies • Distribution and full support of high-quality cell libraries and design kits for the most popular CAD tools • RTL-to-Layout service for deep-submicron technologies • Front-end ASIC design through Alliance Partners Industry is rapidly discovering the benefits of using the EUROPRACTICE IC service to help bring new product designs to market quickly and cost-effectively. The EUROPRACTICE ASIC route supports especially those companies who don’t need always the full range of services or high production volumes. Those companies will gain from the flexible access to silicon prototype and production capacity at leading foundries, design services, high quality support and manufacturing expertise that includes IC manufacturing, packaging and test. This you can get all from EUROPRACTICE IC service, a service that is already established for 20 years in the market. THE EUROPRACTICE IC SERVICES ARE OFFERED BY THE FOLLOWING CENTERS: • imec, Leuven (Belgium) • Fraunhofer-Institut fuer Integrierte Schaltungen (Fraunhofer IIS), Erlangen (Germany) This project has received funding from the European Union’s Seventh Programme for research, technological development and demonstration under grant agreement N° 610018. This funding is exclusively used to support European universities and research laboratories. By courtesy of imec FOREWORD Dear EUROPRACTICE customers, Time goes on. A year passes very quickly and when we look around us we see a tremendous rapidly changing world. -

Japanese Manufacturing Affiliates in Europe and Turkey

06-ORD 70H-002AA 7 Japanese Manufacturing Affiliates in Europe and Turkey - 2005 Survey - September 2006 Japan External Trade Organization (JETRO) Preface The survey on “Japanese manufacturing affiliates in Europe and Turkey” has been conducted 22 times since the first survey in 1983*. The latest survey, carried out from January 2006 to February 2006 targeting 16 countries in Western Europe, 8 countries in Central and Eastern Europe, and Turkey, focused on business trends and future prospects in each country, procurement of materials, production, sales, and management problems, effects of EU environmental regulations, etc. The survey revealed that as of the end of 2005 there were a total of 1,008 Japanese manufacturing affiliates operating in the surveyed region --- 818 in Western Europe, 174 in Central and Eastern Europe, and 16 in Turkey. Of this total, 291 affiliates --- 284 in Western Europe, 6 in Central and Eastern Europe, and 1 in Turkey --- also operate R & D or design centers. Also, the number of Japanese affiliates who operate only R & D or design centers in the surveyed region (no manufacturing operations) totaled 129 affiliates --- 125 in Western Europe and 4 in Central and Eastern Europe. In this survey we put emphasis on the effects of EU environmental regulations on Japanese manufacturing affiliates. We would like to express our great appreciation to the affiliates concerned for their kind cooperation, which have enabled us over the years to constantly improve the survey and report on the results. We hope that the affiliates and those who are interested in business development in Europe and/or Turkey will find this report useful. -

Co-Emulation of Scan-Chain Based Designs Utilizing SCE-MI Infrastructure

UNLV Theses, Dissertations, Professional Papers, and Capstones 5-1-2014 Co-Emulation of Scan-Chain Based Designs Utilizing SCE-MI Infrastructure Bill Jason Pidlaoan Tomas University of Nevada, Las Vegas Follow this and additional works at: https://digitalscholarship.unlv.edu/thesesdissertations Part of the Computer Engineering Commons, Computer Sciences Commons, and the Electrical and Computer Engineering Commons Repository Citation Tomas, Bill Jason Pidlaoan, "Co-Emulation of Scan-Chain Based Designs Utilizing SCE-MI Infrastructure" (2014). UNLV Theses, Dissertations, Professional Papers, and Capstones. 2152. http://dx.doi.org/10.34917/5836171 This Thesis is protected by copyright and/or related rights. It has been brought to you by Digital Scholarship@UNLV with permission from the rights-holder(s). You are free to use this Thesis in any way that is permitted by the copyright and related rights legislation that applies to your use. For other uses you need to obtain permission from the rights-holder(s) directly, unless additional rights are indicated by a Creative Commons license in the record and/ or on the work itself. This Thesis has been accepted for inclusion in UNLV Theses, Dissertations, Professional Papers, and Capstones by an authorized administrator of Digital Scholarship@UNLV. For more information, please contact [email protected]. CO-EMULATION OF SCAN-CHAIN BASED DESIGNS UTILIZING SCE-MI INFRASTRUCTURE By: Bill Jason Pidlaoan Tomas Bachelor‟s Degree of Electrical Engineering Auburn University 2011 A thesis submitted -

Partial Reconfiguration: a Simple Tutorial

Partial Reconfiguration: A Simple Tutorial Richard Neil Pittman Microsoft Research February 2012 Technical Report MSR-TR 2012-19 Microsoft Research Microsoft Corporation One Microsoft Way Redmond, WA 98052 Partial Reconfiguration: A Simple Tutorial A Tutorial for XILINX FPGAs Neil Pittman – 2/12, version 1.0 Introduction Partial Reconfiguration is a feature of modern FPGAs that allows a subset of the logic fabric of a FPGA to dynamically reconfigure while the remaining logic continues to operate unperturbed. Xilinx has provided this feature in their high end FPGAs, the Virtex series, in limited access BETA since the late 1990s. More recently it is a production feature supported by their tools and across their devices since the release of ISE 12. The support for this feature continues to improve in the more recent release of ISE 13. Altera has promised this feature for their new high end devices, but this has not yet materialized. Partial Reconfiguration of FPGAs is a compelling design concept for general purpose reconfigurable systems for its flexibility and extensibility. Despite the significant improvements in software tools and support, the Xilinx partial reconfiguration design option has a reputation for being an expert level flow that is difficult to use. In this tutorial we will show that it can actually be quite simple. As a case study, we apply Partial Reconfiguration to the Simple Interface for Reconfigurable Computing (SIRC) toolset. Combining SIRC and partial reconfiguration makes the idea of general purpose hardware and software user systems deployed on demand on generic platforms viable. The goal is to make developers more confident in the practicality of this concept and in their own ability to use it, so that more will take advantage of what it has to offer. -

Xilinx-Solution-Brief-Bluedot.Pdf

SOLUTION BRIEF Product Name DeepField-SR – Deep Learning based Video Super Resolution Accelerator INTRODUCTION DeepField-SR is a fixed functional hardware accelerator leveraging Xilinx Alveo Cards to offer the highest computational efficiency for Video Super Resolution. Based Solution Image on proprietary Neural Network trained with real world video data from the internet and fusing spatio-temporal information in multiple frames, it produces superior high resolution video quality. BENEFITS Key Features Comparing with EDSR(NTIRE 2017) on Tesla V100 > A fixed functional hardware > 45x faster than GPU accelerator offering high throughput > Scalable architecture to support multiple FPGA cards > Low upscaling latency > Deep Neural Network suitable for resource limited FPGA > 0.03 better quality assessment in LPIPS metric than > Deep Neural Network trained EDSR with real world video data > 44x lower latency than GPU > Designed with High Level Synthesis > Easy to update and upgrade per market demands > 1x FPGA card required Adaptable. Intelligent. © Copyright 2020 Xilinx SOLUTION OVERVIEW DeepField-SR is deployable on both public cloud and on-premise with Xilinx Alveo U200/U50 Accelerator Cards. As it is designed in scalable architecture and supports multiple FPGA cards, it can flexibly respond to various resolution upscale request. Its runtime performance on single Alveo U50 is 11 ~ 14fps to upscale video up to 4K resolution. The API is integrated within an FFmpeg workflow, meaning that simple command enables DeepField-SR acceleration and upscaling user input video. TAKE THE NEXT STEP Learn more about BLUEDOT Inc. For DeepField-SR quality evaluation, please visit http://kokoon.cloud Reach out to BLUEDOT sales at [email protected] Corporate Headquarters Europe Japan Asia Pacific Pte. -

Technical Portion

50 50 YEARS OF INNOVATION DESIGN AUTOMATION CONFERENCE Celebrating 50 Years of Innovation! www.DAC.com JUNE 2-6, 2013 AUSTIN CONVENTION CENTER - AUSTIN, TX SPONSORED BY: IN TECHNICAL COOPERATION WITH: 1 2 TABLE OF CONTENTS General Chair’s Welcome ....................................................................................................................... 4 Sponsors ................................................................................................................................................. 5 Important Information ............................................................................................................................ 6 Networking Receptions .......................................................................................................................... 7 Keynotes ....................................................................................................................................8,9,13-15 Kickin’ it up in Austin Party .................................................................................................................. 10 Global Forum ........................................................................................................................................ 11 Awards .................................................................................................................................................. 12 Technical Sessions ..........................................................................................................................16-36 -

Simulating Altera Designs

1. Simulating Altera Designs May 2013 QII53025-13.0.0 QII53025-13.0.0 This document describes simulating designs that target Altera® devices. Simulation verifies design behavior before device programming. The Quartus® II software supports RTL and gate level design simulation in third-party EDA simulators. Altera Simulation Overview Simulation involves setting up your simulator working environment, compiling simulation model libraries, and running your simulation. Generate simulation files in an automated or custom flow. Refer to Figure 1–1 and Table 1–3. Figure 1–1. Simulation in Quartus II Design Flow Design Entry (HDL, Qsys, DSP Builder) Altera Simulation RTL Simulation Models Quartus II Design Flow Gate-Level Simulation Post-synthesis functional Post-synthesis Analysis & Synthesis simulation netlist functional simulation EDA Fitter Netlist Post-fit functional Post-fit functional (place-and-route) Writer simulation netlist simulation Post-fit timing TimeQuest Timing Analyzer (Optional)Post-fit timing Post-fit simulation netlist (1) timing simulation simulation (3) Device Programmer (1) Timing simulation is not supported for Arria® V, Cyclone® V, Stratix® V, and newer families. You can use the Quartus II NativeLink feature to automatically generate simulation files and scripts. NativeLink can launch your simulator a from within the Quartus II software. Use a custom flow for more control over all aspects of simulation file generation. © 2013 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. -

Alveo U50 Data Center Accelerator Card Installation Guide

Alveo U50 Data Center Accelerator Card Installation Guide UG1370 (v1.6) June 4, 2020 Revision History Revision History The following table shows the revision history for this document. Section Revision Summary 06/04/2020 Version 1.6 Chapter 1: Introduction Updated the information. Card Features Added new section. Chapter 2: Card Interfaces and Details Added a caution. Known Issues • Added a known issue about installing the U50 card deployment package. • Added a known issue about downgrading to a beta platform. Downgrading Packages Added information about downgrading to a beta platform. Downgrading Packages Added information about downgrading to a beta platform. 02/27/2020 Version 1.5 XRT and Deployment Platform Installation Procedures on Replaced steps 4, 6, 7, 8, and 9 to document the new RedHat and CentOS installation steps for U50. Replaced all mentions of zip files with tar.gz. XRT and Deployment Platform Installation Procedures on Replaced steps 1, 2, 3, and the log file of step 6 to document Ubuntu the new installation steps for U50. Replaced all mentions of zip files with tar.gz. Running lspci Revised log file in step 2. Running xbmgmt flash --scan Revised output, platform, and ID information in step 1. Upgrading Packages Updated step 1 to include a link to chapter 4; removed steps 2-6. Upgrading Packages Updated step 1 to include a link to chapter 4; removed steps 2-6. 01/07/2020 Version 1.4 Installing the Card Updated to add notes about UL Listed Servers and card handling. 12/18/2019 Version 1.3 General Updated output logs. -

Verisilicon and Cadence

VeriSilicon and Cadence “Using Allegro FPGA System Planner XL, we completed pin assignment in one week. A manual pin-assignment process would have been error-prone, tedious, and time-consuming—it would have taken at least one month.“ Steven Guo, Package Design and PCB Implementation Manager, VeriSilicon The Customer Business Challenges VeriSilicon Holdings Co. is a world-class IC design foundry • Meet an aggressive timeline for an FPGA- that provides custom silicon solutions and system-on-chip based ASIC prototyping project (SoC) / system-in-package (SiP) turnkey services. The company’s • Develop a scalable prototyping platform solutions combine licensable digital signal processing cores, for hardware/software integration and eDRAM, value-added mixed-signal IP, and other IP into SoC co-verification platforms that extends to sub-65nm process technologies. These platforms are used in a wide range of consumer Design Challenges electronics devices, including set-top boxes, home gateway • Accelerate the design process with devices, mobile Internet devices, cell phones, HDTV devices, automated, placement-aware pin and Blu-ray/DVD players. assignment • Optimize the physical connectivity, even as For five consecutive years, Deloitte LLP has ranked VeriSilicon it changes among the top 50 high-tech, high-growth companies in China. Red Herring named VeriSilicon one of the top 100 private • Ensure quality and reduce complexity with companies in Asia, and EE Times named the company one of reuse of interface rules and protocols 60 emerging start-ups. Headquartered in Shanghai, China, Cadence Solutions VeriSilicon has R&D centers in both China and the United States, • Allegro FPGA System Planner XL with sales and customer support offices throughout Asia, the United States, and Europe. -

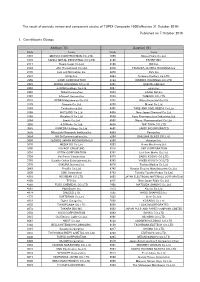

Published on 7 October 2016 1. Constituents Change the Result Of

The result of periodic review and component stocks of TOPIX Composite 1500(effective 31 October 2016) Published on 7 October 2016 1. Constituents Change Addition( 70 ) Deletion( 60 ) Code Issue Code Issue 1810 MATSUI CONSTRUCTION CO.,LTD. 1868 Mitsui Home Co.,Ltd. 1972 SANKO METAL INDUSTRIAL CO.,LTD. 2196 ESCRIT INC. 2117 Nissin Sugar Co.,Ltd. 2198 IKK Inc. 2124 JAC Recruitment Co.,Ltd. 2418 TSUKADA GLOBAL HOLDINGS Inc. 2170 Link and Motivation Inc. 3079 DVx Inc. 2337 Ichigo Inc. 3093 Treasure Factory Co.,LTD. 2359 CORE CORPORATION 3194 KIRINDO HOLDINGS CO.,LTD. 2429 WORLD HOLDINGS CO.,LTD. 3205 DAIDOH LIMITED 2462 J-COM Holdings Co.,Ltd. 3667 enish,inc. 2485 TEAR Corporation 3834 ASAHI Net,Inc. 2492 Infomart Corporation 3946 TOMOKU CO.,LTD. 2915 KENKO Mayonnaise Co.,Ltd. 4221 Okura Industrial Co.,Ltd. 3179 Syuppin Co.,Ltd. 4238 Miraial Co.,Ltd. 3193 Torikizoku co.,ltd. 4331 TAKE AND GIVE. NEEDS Co.,Ltd. 3196 HOTLAND Co.,Ltd. 4406 New Japan Chemical Co.,Ltd. 3199 Watahan & Co.,Ltd. 4538 Fuso Pharmaceutical Industries,Ltd. 3244 Samty Co.,Ltd. 4550 Nissui Pharmaceutical Co.,Ltd. 3250 A.D.Works Co.,Ltd. 4636 T&K TOKA CO.,LTD. 3543 KOMEDA Holdings Co.,Ltd. 4651 SANIX INCORPORATED 3636 Mitsubishi Research Institute,Inc. 4809 Paraca Inc. 3654 HITO-Communications,Inc. 5204 ISHIZUKA GLASS CO.,LTD. 3666 TECNOS JAPAN INCORPORATED 5998 Advanex Inc. 3678 MEDIA DO Co.,Ltd. 6203 Howa Machinery,Ltd. 3688 VOYAGE GROUP,INC. 6319 SNT CORPORATION 3694 OPTiM CORPORATION 6362 Ishii Iron Works Co.,Ltd. 3724 VeriServe Corporation 6373 DAIDO KOGYO CO.,LTD. 3765 GungHo Online Entertainment,Inc. -

EP Activity Report 2015

EUROPRACTICE IC SERVICE THE RIGHT COCKTAIL OF ASIC SERVICES EUROPRACTICE IC SERVICE OFFERS YOU A PROVEN ROUTE TO ASICS THAT FEATURES: · .QYEQUV#5+%RTQVQV[RKPI · (NGZKDNGCEEGUUVQUKNKEQPECRCEKV[HQTUOCNNCPFOGFKWOXQNWOGRTQFWEVKQPSWCPVKVKGU · 2CTVPGTUJKRUYKVJNGCFKPIYQTNFENCUUHQWPFTKGUCUUGODN[CPFVGUVJQWUGU · 9KFGEJQKEGQH+%VGEJPQNQIKGU · &KUVTKDWVKQPCPFHWNNUWRRQTVQHJKIJSWCNKV[EGNNNKDTCTKGUCPFFGUKIPMKVUHQTVJGOQUVRQRWNCT%#&VQQNU · 46.VQ.C[QWVUGTXKEGHQTFGGRUWDOKETQPVGEJPQNQIKGU · (TQPVGPF#5+%FGUKIPVJTQWIJ#NNKCPEG2CTVPGTU +PFWUVT[KUTCRKFN[FKUEQXGTKPIVJGDGPG«VUQHWUKPIVJG'74124#%6+%'+%UGTXKEGVQJGNRDTKPIPGYRTQFWEVFGUKIPUVQOCTMGV SWKEMN[CPFEQUVGHHGEVKXGN[6JG'74124#%6+%'#5+%TQWVGUWRRQTVUGURGEKCNN[VJQUGEQORCPKGUYJQFQP°VPGGFCNYC[UVJG HWNNTCPIGQHUGTXKEGUQTJKIJRTQFWEVKQPXQNWOGU6JQUGEQORCPKGUYKNNICKPHTQOVJG¬GZKDNGCEEGUUVQUKNKEQPRTQVQV[RGCPF RTQFWEVKQPECRCEKV[CVNGCFKPIHQWPFTKGUFGUKIPUGTXKEGUJKIJSWCNKV[UWRRQTVCPFOCPWHCEVWTKPIGZRGTVKUGVJCVKPENWFGU+% OCPWHCEVWTKPIRCEMCIKPICPFVGUV6JKU[QWECPIGVCNNHTQO'74124#%6+%'+%UGTXKEGCUGTXKEGVJCVKUCNTGCF[GUVCDNKUJGF HQT[GCTUKPVJGOCTMGV THE EUROPRACTICE IC SERVICES ARE OFFERED BY THE FOLLOWING CENTERS: · KOGE.GWXGP $GNIKWO · (TCWPJQHGT+PUVKVWVHWGT+PVGITKGTVG5EJCNVWPIGP (TCWPJQHGT++5 'TNCPIGP )GTOCP[ This project has received funding from the European Union’s Seventh Programme for research, technological development and demonstration under grant agreement N° 610018. This funding is exclusively used to support European universities and research laboratories. © imec FOREWORD Dear EUROPRACTICE customers, We are at the start of the -

In the United States District Court for the Eastern District of Texas Tyler Division

Case 6:06-cv-00480-LED Document 1 Filed 11/08/06 Page 1 of 8 IN THE UNITED STATES DISTRICT COURT FOR THE EASTERN DISTRICT OF TEXAS TYLER DIVISION NARPAT BHANDARI § § Plaintiff § § v. § Case No. 6:06-cv-480 § CADENCE DESIGN SYSTEMS, INC.; § MAGMA DESIGN AUTOMATION, § INC.; DYNALITH SYSTEMS, INC.; § JURY TRIAL DEMANDED ALTERA CORP.; MENTOR GRAPHICS § CORP.; AND ALDEC, INC. § § Defendants § § § § § PLAINTIFF’S ORIGINAL COMPLAINT Plaintiff, Narpat Bhandari (“Bhandari”), files this Original Complaint against Defendants, Cadence Design Systems, Inc. (“Cadence”), Magma Design Automation, Inc. (“Magma”), Dynalith Systems, Inc. (“Dynalith”), Altera Corp. (“Altera”), Mentor Graphics Corp. (“Mentor”), and Aldec, Inc. (“Aldec”) and alleges as follows: THE PARTIES 1. Bhandari is an individual who resides at 14530 Deer Park Court, Los Gatos, CA 95032. 2. Cadence, on information and belief, is a corporation organized under the laws of the State of Delaware. Cadence is doing business in Texas, and, on information and belief, has a principal place of business at 2655 Seely Ave, Building 5, San Jose, CA 95134-1931. Case 6:06-cv-00480-LED Document 1 Filed 11/08/06 Page 2 of 8 Cadence may be served with process by serving its registered agent, CT Corp System at 350 N. St. Paul Street, Dallas, TX 75201. 3. Magma, on information and belief, is a corporation organized under the laws of the State of Delaware. Magma is doing business in Texas, and, on information and belief, has a principal place of business at 5460 Bayfront Plaza, Santa Clara, CA 95054. Magma may be served with process by serving its registered agent, Corporation Service Company, d/b/a CSC-Lawyers Incorporating Service Company at 701 Brazos Street Suite 1050, Austin, TX 78701.