Dance Dance Revolution on FPGA

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

CPR for the Arcade Culture a Case History on the Development of the Dance Dance Revolution Community

CPR for the Arcade Culture A Case History on the Development of the Dance Dance Revolution Community Alexander Chan SUID 5075504 STS 145: History of Computer Game Design Stanford University March 16, 2004 Introduction Upon entering an arcade, you come across an unusual spectacle. Loud Japanese techno and a flashing neon glow pour out of the giant speakers and multicolored lights of an arcade console at the center of the room. Stranger than the flashy arcade cabinet is the sweaty teenager stomping on a metal platform in front of this machine, using his feet to vigorously press oversized arrows as the screen in front of him displays arrows scrolling upward. A growing group of people crowd around to watch this unusual game-play, cheering the player on. In large letters, the words “Dance Dance Revolution 3rd Mix” glow above the arcade machine. Most people who stumble upon a scene similar to this one would rarely believe that such a conceptually simple arcade game could foster an enormous nation-wide game community, both online and offline. Yet the rules of the game are deceptively simple. The players (one or two) must press the arrows on the platform (either up, down, left, or right) when the corresponding arrows on the screen reach the top, usually on beat with the techno/pop song being played. If the player doesn’t press the arrows on time, the song will quickly come to an end, and the machine will Arrows scrolling up a DDR screen ask for more quarters to continue play. Yet despite its simplicity, Dance Dance Revolution, or DDR for short, has helped create a giant player community in the United States, manifesting itself though various forms. -

Exerlearn Bike: an Exergaming System for Children's Educational and Physical Well-Being by Rajwa Alharthi a Thesis Submitted T

EXERLEARN BIKE: AN EXERGAMING SYSTEM FOR CHILDREN’S EDUCATIONAL AND PHYSICAL WELL-BEING BY RAJWA ALHARTHI A THESIS SUBMITTED TO THE FACULTY OF GRADUATE AND POSTDOCTORAL STUDIES IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER IN COMPUTER SCIENCE OTTAWA-CARLETON INSTITUTE FOR COMPUTER SCIENCE SCHOOL OF ELECTRICAL ENGINEERING AND COMPUTER SCIENCE UNIVERSITY OF OTTAWA © RAJWA ALHARTHI, OTTAWA, CANADA 2012 Abstract Inactivity and sedentary behavioural patterns among children contribute greatly to a wide range of diseases including obesity, cancer, cardiovascular disease, and diabetes. It is also associated with other important health effects like mental health issues, anxiety, and depression. In order to reduce these trends, we need to focus on the highest contributing factor, which is lack of physical activity in children’s daily lives. 'Exergames' are believed to be a very good solution in promoting physical activity in children. Such games encourage children to engage in physical activity for long periods of time while enjoying their gaming experience. The purpose of this thesis is to provide means of directing child behaviour in a healthy direction by using gaming enhancements that encourage physical exertion. We believe that the combination of both exercising and learning modalities in an attractive gaming environment could be more beneficial for the child's well-being. In order to achieve this, we present an adaptive exergaming system, the "ExerLearn Bike", which combines physical, gaming, and educational features. The main idea of the system is to have children learn about new objects, new language, practice their math skills, and improve their cognitive ability through enticing games and effective exercise. -

Operation Manual

9 WEBSITE: WWW.EXTREMEHOMEARCADES.COM; EMAIL: [email protected] OPERATION MANUAL Last Updated: 9/12/2021 Extreme Home Arcades – Operation Manual - 1 | Page EXTREME HOME ARCADES OPERATION MANUAL QUICK START GUIDE This Quick Start Guide is for fast learners, and customers who do not like user’s manuals and just want to dive in)! To receive your machine from the shipping company, unpack it, and move it into your residence, please see those sections later in this manual. This Quick Start Guide presumes you have your machine in a safe location, have plugged it in and the machine has electrical power. 1. Turning On Your Machine: • Uprights (MegaCade, Classic, Stealth) – The power button is located on top of the machine (upper left or right top of machine). It is a standard arcade push button (typically black). Push it, and it will turn on your machine. • Tabletops – The power button is located on the back center portion of the cabinet. • Pedestals – The power button is located on the back of the machine, near the center of the pedestal cabinet, opposite the HDMI port. 2. Loading a Game: • After you turn on your machine, an introduction video will automatically load. To skip the introduction video, push any button or push any position on any joystick on the machine. You will be at the Main Hyperspin Wheel. a. You can move down the HyperSpin wheel by pressing the Player 1 or Player 2 Joystick down (towards your body). Alternatively, you can move up the HyperSpin wheel by pressing the Player 1 or Player 2 Joystick up (away from your body). -

CPR for the Arcade Culture a Case History on the Development of the Dance Dance Revolution Community

CPR for the Arcade Culture A Case History on the Development of the Dance Dance Revolution Community Alexander Chan SUID 5075504 STS 145: History of Computer Game Design Stanford University March 16, 2004 Introduction Upon entering an arcade, you come across an unusual spectacle. Loud Japanese techno and a flashing neon glow pour out of the giant speakers and multicolored lights of an arcade console at the center of the room. Stranger than the flashy arcade cabinet is the sweaty teenager stomping on a metal platform in front of this machine, using his feet to vigorously press oversized arrows as the screen in front of him displays arrows scrolling upward. A growing group of people crowd around to watch this unusual game-play, cheering the player on. In large letters, the words “Dance Dance Revolution 3rd Mix” glow above the arcade machine. Most people who stumble upon a scene similar to this one would rarely believe that such a conceptually simple arcade game could foster an enormous nation-wide game community, both online and offline. Yet the rules of the game are deceptively simple. The players (one or two) must press the arrows on the platform (either up, down, left, or right) when the corresponding arrows on the screen reach the top, usually on beat with the techno/pop song being played. If the player doesn’t press the arrows on time, the song will quickly come to an end, and the machine will Arrows scrolling up a DDR screen ask for more quarters to continue play. Yet despite its simplicity, Dance Dance Revolution, or DDR for short, has helped create a giant player community in the United States, manifesting itself though various forms. -

Playstation Games

The Video Game Guy, Booths Corner Farmers Market - Garnet Valley, PA 19060 (302) 897-8115 www.thevideogameguy.com System Game Genre Playstation Games Playstation 007 Racing Racing Playstation 101 Dalmatians II Patch's London Adventure Action & Adventure Playstation 102 Dalmatians Puppies to the Rescue Action & Adventure Playstation 1Xtreme Extreme Sports Playstation 2Xtreme Extreme Sports Playstation 3D Baseball Baseball Playstation 3Xtreme Extreme Sports Playstation 40 Winks Action & Adventure Playstation Ace Combat 2 Action & Adventure Playstation Ace Combat 3 Electrosphere Other Playstation Aces of the Air Other Playstation Action Bass Sports Playstation Action Man Operation EXtreme Action & Adventure Playstation Activision Classics Arcade Playstation Adidas Power Soccer Soccer Playstation Adidas Power Soccer 98 Soccer Playstation Advanced Dungeons and Dragons Iron and Blood RPG Playstation Adventures of Lomax Action & Adventure Playstation Agile Warrior F-111X Action & Adventure Playstation Air Combat Action & Adventure Playstation Air Hockey Sports Playstation Akuji the Heartless Action & Adventure Playstation Aladdin in Nasiras Revenge Action & Adventure Playstation Alexi Lalas International Soccer Soccer Playstation Alien Resurrection Action & Adventure Playstation Alien Trilogy Action & Adventure Playstation Allied General Action & Adventure Playstation All-Star Racing Racing Playstation All-Star Racing 2 Racing Playstation All-Star Slammin D-Ball Sports Playstation Alone In The Dark One Eyed Jack's Revenge Action & Adventure -

An Exclusive Tour of Mad Catz Interactive, Inc

An Exclusive Tour of Mad Catz Interactive, Inc. By Bruce Pechman, The Muscleman of TechnologySM www.mrbicep.com August, 2003 Inside the World’s Number One Third Party Video Game Accessory Manufacturer Entering the Threshold The non-descript exterior of the white building bears no resemblance to the impeccably managed, yet frenzied daily routines taking place inside the world’s number one third party video game console accessory maker. Perhaps just the clean Mad Catz logo brandished atop the main doors lets only the well-informed gamer know a very special blend of magical creativity lurks inside the confines of these walls. Mad Catz Product Managers, Matt and Vincent My tour of duty begins with the Product Management team lead by my gracious host, Vincent Tucker. Vincent instantly introduces me to his dynamic duo, Matt Bennion and Richi Wang. Although the three share many similar responsibilities, each has their own respective specialties. Matt, for example, is hard at work on a newfangled Dance Pad for Xbox’s upcoming title Dance Dance Revolution Ultramix. A Dance Pad sounds like an amusing product, but bringing it from design to market is serious business for Matt and the Mad Catz team. The Pad requires co-branding and direct communication with the game’s publisher and producers. Contemplate getting those blinking light patterns in sync with a step-sensitive pad and you realize this is anything but child’s play (with a nation of plump offspring, I praise Dance Pads). Adjacent to Matt’s cubicle, I see Richi hard at work manipulating a mock-up for a yet to be announced accessory for Nokia’s soon to be released N-Gage handheld gaming system. -

DIY Wireless DDR Dance Pad with Bluefruit EZ-Key Created by Paul Beaudet

DIY Wireless DDR Dance Pad with Bluefruit EZ-Key Created by Paul Beaudet Last updated on 2018-08-22 03:40:07 PM UTC Guide Contents Guide Contents 2 Overview 3 What's DDR? 3 Materials 3 Cheapo method - As Shown 3 Quality approach- Recommended 4 Holding it all together 4 Controller 4 Tools and Prep 6 Tools 6 Design Note 6 Preparation 6 Assembly 8 Step 1 8 Step 2 8 Step 3 8 Step 4 8 Build Buttons 10 Step 5 10 Step 6 or 7 10 Test Conection 13 Break out the multimeter! 13 Finishing touches 14 Glue the vinyl graphic on 14 Manage the wires 14 Add some Velcro straps 15 Done! 15 © Adafruit Industries https://learn.adafruit.com/diy-wireless-ddr-dance-pad-bluefruit-ez-key Page 2 of 16 Overview What's DDR? Dance Dance Revolution or DDR for short is a rhythm game that is played with a directional pad made for feet. Coordination and rhythm is tested by watching on screen dance notes making steps to the keys of the beat. It's a simple step on up down left or right and sometimes even combinations of steps. DDR has been very popular in arcades and on game consoles. Now-a-days, however, the game can be enjoyed with a clone games like "Beats" for android, "Stepmania" for the desktop, or even FFR (flash flash revolution) online. This tutorial generally explains how to go about building a wireless game pad on the cheap to avoid buy expensive adapters or pads. Bluetooth control with Bluefruit EZ-Key honestly works so easily for that there is very little to explain about the controller beyond what is covered in the Bluefruit tutorial. -

La Alfombra De Baile Como Periférico De Entrada Al Ordenador

LA ALFOMBRA DE BAILE COMO PERIFÉRICO DE ENTRADA AL ORDENADOR Rafael García Cabrera Equipo de orientación educativa especializado Jaén [email protected] Resumen La alfombra de baile es un periférico para juegos de videoconsolas y de ordenador. Las alfombras de baile suelen estar divididas en una matriz de 3x3 casillas. Las casillas son como grandes botones pensados para ser pulsados con los pies. El nombre de alfombra de baile, en inglés dance mat o dance pad, tiene su justificación en que la mayoría de los videojuegos para los que está diseñada se basan en el baile al ritmo de la música o de una canción. Otros videojuegos requieren que el jugador se mueva accionando las casillas apropiadas para interactuar con el juego en la pantalla del televisor o del ordenador. En este taller se pretende explicar y practicar cómo utilizar la alfombra de baile como periférico de entrada al ordenador, ampliando sus usos como ayuda técnica de bajo coste. Usos que le podemos dar a la alfombra: para acceder al ordenador, para comunicarse, para aprender, para estimulación (visual, táctil y auditiva), para ejercitar el movimiento y, cómo no, para jugar. Palabras clave Ayudas técnicas, necesidades educativas especiales, comunicación aumentativa y alternativa, estimulación multisensorial. ¿QUÉ ES UNA ALFOMBRA DE BAILE? Una alfombra de baile, denominada en inglés dance mat o dance pad, es un periférico para juegos de videoconsolas y de ordenador. El nombre de alfombra de baile tiene su justificación en que la mayoría de los videojuegos para los que está diseñada se basan en el baile al ritmo de la música o de una canción. -

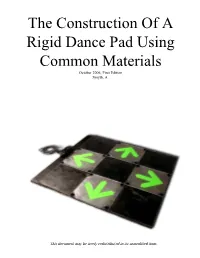

The Construction of a Rigid Dance Pad Using Common Materials October 2006, First Edition Smyth, A

The Construction Of A Rigid Dance Pad Using Common Materials October 2006, First Edition Smyth, A. This document may be freely redistributed in its unmodified form. DESCRIPTION: A custom built Stepmania compatible dance pad designed for high reliability, low maintenance, easy repair and rapid response. The purpose of this project is to create a rigid dance pad similar to an arcade DDR machine or a more expensive “hard” pad. The mechanics of this dance pad are quite simple. Four air-gap switches are wired to a disassembled USB gamepad which are both attached to a rigid substrate such as wood. The air-gap switches have a conductive material (aluminum foil or sheet metal) on both interior surfaces. When pressure is applied by the foot of the player, the acrylic bends, pushing the two metal contacts together and a button press is registered on the controller. MATERIALS: COST: 1 x Logitech Precision $9.99 @ Target (less online) Gamepad 1 x (36inch x 39inch) wood $17 @ Lowe's Home base (plywood or melamine) Improvement Center 5 x (12inch x 12inch) squares $6 @ Home Depot “hardboard” aka high density fiberboard 4 x tagboard arrows $1.50 (sheet) @ Michael's Craft Store 8 x (11.75inch x 11.75inch) Foil – free squares heavy duty sheet metal - $20? aluminum foil or thin sheet metal 10 x (12inch x 12inch) $40 @ Tap Plastics squares .125inch acrylic sheet 16 x adhesive velcro squares $6 @ Joann Fabric & Crafts 1 x plastic enclosure (5inch x $4 @ Radioshack 2.5inch x 2inch) 2 x momentary (N.O.) Approx. $1 each @ pushbutton switches allelectronics.com spray adhesive $3 @ craft store contact cement $3 @ Michael's Craft Store black paint $2 @ hardware store wire Free – probably stolen junk CDs Free – America Online PROCEDURE: 1. -

Raising Heart Rate with Dance Pad Based Computer Games

Edith Cowan University Research Online ECU Publications Pre. 2011 2009 Raising heart rate with dance pad based computer games Martin Masek Edith Cowan University Philip Hingston Edith Cowan University Matthew Carrigy Edith Cowan University Liam Collins Edith Cowan University Kazunori Nosaka Edith Cowan University Follow this and additional works at: https://ro.ecu.edu.au/ecuworks Part of the Computer Sciences Commons Masek, M., Hingston,P., Carrigy, M., Collins, L. & Nosaka, K. (2009) Raising heart rate with dance pad based computer games. Computer Games, Multimedia and Allied Technology 2009 (pp. 245-252). Singapore: Computer Games, Multimedia and Allied Technology . This Conference Proceeding is posted at Research Online. https://ro.ecu.edu.au/ecuworks/455 Computer Games, Multimedia and Allied Technology 09 Raising Heart Rate with Dance Pad Based Computer Games Martin Masek, Philip Hingston, Matthew Carrigy Ken Nosaka and Liam Collins School of Exercise, Biomedical and Health Sciences School of Computer and Information Science Edith Cowan University Edith Cowan University Perth, Western Australia Perth, Western Australia +81 8 6304 5655 [email protected]; [email protected]; [email protected] [email protected]; [email protected] Abstract Floor-positioned computer game controllers that require movement of large muscles are well known, most commonly in the form used in the rhythm-based game Dance Dance Revolution. Studies of the health benefits of such devices are often reported in the context of using the controller to play a particular game. In this paper we take a different approach, analyzing the controller as an exercise device in its own right, and using the findings to implement an appropriate game prototype. -

2 - Player Input Handling Csc 165 Computer Game Architecture Overview

CSc 165 Lecture Notes 2 - Player Input Handling CSc 165 Computer Game Architecture Overview • Device Types • Device Abstractions 2 - Input Handling • Controllers • Input Handling Packages • Event Queues • Input Action Commands (making the inputs do things) 2 CSc 165 Lecture Notes CSc 165 Lecture Notes 2 - Player Input Handling 2 - Player Input Handling Types of Input Devices Input Handling Goals • Keyboard • Steering Wheel Keep games device-independent o Game shouldn’t contain hard-coded device details • Mouse • Dance Pad o Game shouldn’t fail when a particular device is absent • Joystick (“POV”) • Guitar (allow substitution) • “POV Hat Switch” • WiiMote Keep engine device-independent o Engine components should not contain hard-coded • Gamepad • Kinect device details • Paddle • others? … isolate details in an Input Manager 3 4 CSc 165 Lecture Notes CSc 165 Lecture Notes 2 - Player Input Handling 2 - Player Input Handling Device Abstractions “D-pad” (Directional-pad) Axes Two fundamental device types: Discrete axis devices D-pad o Can have either one or two axes ▪ Button – returns pressed or not pressed Frequently represented as 1.0 or 0.0 Single-axis form: one component; U returns one value: L R ▪ Axis – returns a float .25 D Two types of Axis: .125 .375 Dual axis form: two components; each returns a value: ▪ Continuous: returns a value in a range 1.0 0 .5 e.g. { -1 … 1 } or { 0 … 1 } L N R X: ▪ Discrete: returns a value from a set .875 .625 -1 0 +1 e.g. [ 0, 1 ] or [ -1, 0, 1 ] .75 D N U Can be absolute or relative N UL U UR R DR D DL L Y: -1 0 +1 0 .125 .25 .375 .5 .625 .75 .875 1.0 5 6 CSc 165 Lecture Notes CSc 165 Lecture Notes 2 - Player Input Handling 2 - Player Input Handling Controllers Controller Example: GamePad Most “devices” are really collections : o Keyboard: collection of (e.g. -

Virtual Reality

Virtual reality L. Katz, J. Parker, H. Tyreman & R. Levy Sport Technology Research Laboratory, University of Calgary, Calgary, Canada. Abstract Virtual reality (VR) involves technology and visual art that allows a user to inter- act with a computer-simulated environment. These environments can range from a simulation of an authentic situation to the creation of a wholly imagined world. While most virtual reality environments (VREs) are primarily visual experi- ences (computer screens, large screen displays, multiple screens and stereoscopic displays) new tools are being developed that enhance the visual experience by addressing other sensory modalities (e.g. sound, tactile feedback and smell). VR has been used effectively to train astronauts, pilots, physicians, military person- nel, and now, even athletes. While the cost of creating VRE is the most expensive type of computer development, the entry of game manufacturers into the fi eld is drastically changing the cost of producing and using these environments. This chapter provides an overview of VR and focuses on the most promising develop- ments in VR, especially in the area of sport and exercise. The implications of these innovations for other spheres of activity are also discussed. Keywords: virtual reality, virtual environments, virtual reality environments, simulation, gaming, reaction time 1 Introduction This chapter acquaints the reader with the issues related to virtual reality (VR) in sport and human performance and also highlights the potential of these types of environments to revolutionize the approach to equipping and training athletes and coaches. Extrapolation of the impact of this promising technology to other diverse fi elds is provided. VR has been defi ned previously [1].