CXD1217Q Synchronizing Signal Generator for Video Camera

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Specific Signals to Ensure Optimum CAY

.4 versions of the 1515 are available .Specific signals to ensure optimum to suit specific needs. Each version CAY performance. Custom signals supports composite and GBR formats also available. plus the following component analog .Optional component digital (D1- formats: 4:2:2) signals to meet SMPTE Version M ...M-IITM RP125-l987 standards. Version S SMPTE Parallel .Optional composite digital (D2) Version SP ...Betacam TMand outputs of all available NTSC test Betacam SpTM signals. Version U Universal: BetacamTM .Optional composite digital (D2) to + M-IITM + SMPTE analog (NTSC) converter module. + S- VHS + formats .Digital signal storage for greater .Sized for side-by-side rack mount- precision and reliable replication. ing with a waveform monitor/ .Modular design allows easy testing vectorscope. and maintenance. .Full genlock with remote control- .l2-character source ID. .Black burst option to provide full RS-170A sync generator capability. .Dual Timing Pulses and Timing Bow tie test signals to guarantee precise interchannel timing and amplitude measurements in CAV. Providing both Component Analog timing can be adjusted from 45 micro- -COMPONENT Video and Composite NTSC test sig- seconds of advance to 15 microseconds nals, the Magni 1515fills a vital niche of delay, and overlaid on the test signal DIGITAL OUTPUT in today's studio or post-production for viewing on a picture monitor and This option (Option -04) provides 4:2:2 environment by allowing the perform- setting. component digital signals to SMPTE RP125-1987 standards. 75% Color Bars ance of equipment in either format to The reference input is switch-selectable, are available at the output connector be measured without costly duplication loop-through or 75 Ohm internally ter- with any signal selection from the of test instrumentation. -

SC/H and Color-Framing (Orig

The Final Word on SC/H and Color-framing (Orig. 2/1990 Rev. 7 1/2000 © Eric Wenocur) Anyone editing with 1” Type-C VTRs and today’s complex interformat systems has experienced the unwanted appearance of a horizontal shift in the picture, and the ensuing search for the cause. While the terms “SC/H phase” and “color-framing” are used regularly, they continue to be sources of confusion and misunderstanding to users of VTRs and editing equipment. Although at times we are tempted to attribute problems to the “gremlins” that we know live in our facilities, there really are answers to most color-framing issues! This article is intended to help explain and de-mystify the principles of color-framing in the hope that solutions become more obvious. It will cover a small amount of SC/H phase technical theory, and then explore TBC operation, 1” VTR color-framing and editing, Betacam and MII operation, framestores, and setting up an SC/H timed system. Emphasis has been placed on both the theory and its practical ramifications. SC/H BACKGROUND BASICS The term SC/H phase, short for “subcarrier-to-horizontal” phase, describes a phase (time) relationship between colorburst and horizontal sync in a composite video signal. Because of the relationship between the frequencies of horizontal rate, subcarrier, and number of lines per frame, the phase of colorburst changes 90 degrees every field, while the phase of picture subcarrier (chroma) changes 180 degrees every two fields. Consequently, every two fields the chroma and burst are in phase, but 180 degrees reversed from the previous frame. -

Glossary of Digital Video Terms

Glossary of Digital Video Terms 24P: 24 frame per second, progressive scan. This has been the frame rate of motion picture film since talkies arrived. It is also one of the rates allowed for transmission in the DVB and ATSC television standards – so they can handle film without needing any frame-rate change (3:2 pull-down for 60 fields-per-second systems or running film at 25fps for 50 Hz systems). It is now accepted as a part of television production formats – usually associated with high definition 1080 lines, progressive scan. A major attraction is a relatively easy path from this to all major television formats as well as offering direct electronic support for motion picture film and D-cinema. 24Psf: 24 frame per second, progressive segmented frame. A 24P system in which each frame is segmented – recorded as odd lines followed by even lines. Unlike normal television, the odd and even lines are from the same snapshot in time – exactly as film is shown today on 625/50 TV systems. This way the signal is more compatible (than normal progressive) for use with video systems, e.g. VTRs, SDTI or HD-SDI connections, mixers/switchers etc., which may also handle interlaced scans. It can also easily be viewed without the need to process the pictures to reduce 24-frame flicker. 3:2 pull-down: Method used to map the 24 fps of film onto the 30 fps (60 fields) of 525-line TV, so that one film frame occupies three TV fields, the next two, etc. It means the two fields of every other TV frame come from different film frames making operations such as rotoscoping impossible, and requiring care in editing. -

Analog Waveform Monitors

Analog Waveform Monitors 1740A Series • 1750A Series • 1760 Series Data Sheet Applications Analog Baseband Video Monitoring for Broadcast and Postproduction Applications The 1740A/1750A/1760 Series make up a family of analog video waveform/vector monitors with progressive features in support of today’s demanding television environment. Each model in the series provides improved video performance and ease of operation and incorporates application-specific features. The family includes the 1740A Series composite analog waveform/vector monitors, the 1750A Series, which adds SCH and color frame verification capabilities, and the 1760 Series for mixed-format component/composite applications. (While the 1740A and 1750A do provide basic component waveform monitoring capabilities with parade and overlay displays, only the 1760 provides full component monitoring capabilities.) 1740A Series NTSC, PAL, and dual-standard models in accessory 1700F02 portable Each series includes models for NTSC, PAL, or dual-standard NTSC/PAL cases. operation. For NTSC models, the last digit of the model number is ’0’ (1740A, 1750A, or 1760); ’1’ for PAL (1741A, 1751A, or 1761); and ’5’ for Features & Benefits dual-standard NTSC/PAL (1745A, 1755A, or 1765). The family features a common, straightforward operator interface, allowing Composite or Component Waveform Monitoring the operator to take immediate advantage of the instrument’s extensive Composite Vector Display feature set. Each operating mode provides a full set of operating controls, Picture Display clearly labeled and within easy reach. Key controls are always available, Stereo Audio Display with bezel buttons and knobs identified by intuitive on-screen labels. Time Code Phasing and Amplitude SCH and Color Framing Display Component Vector, Lightning, Diamond, and Bowtie Data Sheet Selection Guide in a production suite or outside production vehicle. -

Responsive Field Service Are Available Worldwide for the Ampex CVR-65

General responsive field service are available D Versatile Time Code System Originally developed for ENG, worldwide for the Ampex CVR-65 -Vertical Interval Time Code the Betacam format is used today as studio player. (VITC) and SMPTE/EBU the acquisition format for all types longitudinal track format of production. But with new applica- Features -Presetable User Bits, free-run tions came demands for improved D Built-in time base corrector pro- or record-run modes picture and sound quality, together vides broadcast quality video -Genlock for setting/syn- with longer play times. The Beta- while eliminating any other sig- chronizing to an external time cam SP format was developed to nal processing requirements code master generator meet these demands and provide D TBC remote control interface -Built-in time code generator/ playback compatibility, while main- D High speed picture-in-shuttle up reader taining the reliability and durability to 24x normal speed in mono- D 'fu'o composite outputs of the original format. chrome, either forward or reverse D 'fu'o dub/component outputs: D Full-featured editor: -Y, R-Y, B-Y or Compressed The CVR-70 studio VTR com- -Assemble and insert edits for Time Division Multiplexed bines the performance of Betacam Video, Audio I and 2, and time (CTDM) output for high- code SP with features such as dynamic quality component editing motion control, viewable pictures in -Preview/Review allows check D Color framing: superior color shuttle, a full-featured editing sys- of edit accuracy framing operation, using both tem, a built-in time base corrector -In/Out marks may be trimmed the CF flag and the Vertical and a versatile time code system. -

DPS-235 Transcoding TBC/Synchronizer Available in Both Single and Dual Channel Con- Figurations, the DPS-235 Is an Ideal General Pur- Pose TBC/Synchronizer

Section8 PHOTO - VIDEO - PRO AUDIO Studio Equipment Horita.....................................482-491 Hotronics...............................492-494 Prime Image .................................495 DPS .........................................496-501 Nova Systems........................502-506 SourceBook Video Allen Avionics...............................506 Miranda.........................................507 Test and Measurement Hamlet ...................................508-509 CompuVideo .........................510-513 Magni Systems .....................514-519 Leader....................................520-531 The rofessional P HORITA TIME-CODE EQUIPMENT For Desktop, Rack Mount or Field Use Horita offers a full line of SMPTE LTC and VlTC Time-Code Readers, Generators, Inserters and Translators. The LTC line offers choice and flexibility, from the basic WG-50 Play Speed Reader/Inserter to the complete TRG-50 PC Generator/Search Speed Reader/Window Inserter with RS-232 interface and TC-TOOL KIT tape logging software. VITC products provide Generator, Reader/Window Inserter and Translator functions, enabling translation between LTC and VITC, as well as having a full-function VITC system. LED units, like the TCD-100 and VLR-100, provide visual displays, as well as reader/generator functions. The TCI-50 and RLT-50 allow time-code to be inserted into, or extracted from, an RS4-22 data stream. The GPI-50 is a time code based dual general purpose interface. Horita also offers color bar, test signal, blackburst and sync generators, a video titler with serial interface and a Safe Area Generator. All products are available in desk top, rackmount and field pack- ages. They are all versatile, affordable and easy to use. TIME-CODE EQUIPMENT WHAT IS SMPTE TIME CODE? Adopted in the late 1960s by the Society of Motion Picture and Why is SMPTE time code so important? The answer can be stated Television Engineers, SMPTE Time Code is an industry standard in two words: Accuracy and repeatability. -

Standards Converter / TBC FC-5000

GROUP 4 CV YC KRAMER ELECTRONICS, LTD Standards Converter / TBC FC-5000 The Kramer FC-5000 is a high quality time base base correction has full proc-amp facilities. Two corrector and standards converter. It features reference inputs with H and SC adjustments. Re-inserts onscreen graphic-based menus for efficient control. burst and sync on the outputs. Vertical blanking can be Converts between PAL B/M/N, NTSC M/443/J, switched to blank or pass VITC and Teletext. Extensive SECAM, and MESECAM. Features: PAL/NTSC range of color and frame lock settings to deal with poor (dynamic) switchable Composite comb filter. The time VT and color framing problems. 4 INTERFACES AND SYNC PROCESSORS TECHNICAL SPECIFICATIONS INPUTS: Input 1composite video. Inputs2&3composite or s-Video (YC), 1Vpp / 75W. OUTPUTS: 2 s-Video (YC) 1Vpp / 75W. 2 composite video 1Vpp / 75W . On screen menu display on output 1. VIDEO BANDWIDTH: Composite video with comb filter 5.0 MHz. +0.5/-1dB. Without comb filter 3.0 MHz. +0.5/-2dB. HF peaking adjustable. AGC: Composite video and (Y) input 0.5 Volts to 2 Volts with AGC acting on sync tip. (C) input nominal 0.3 Volt burst with AGC from -12dB to +3dB. INPUT FORMATS: Pal B/I/G/M/N, NTSC M/443/J and SECAM-H/V. OUTPUT FORMATS: Pal B/I/G/M/N, NTSC M/443/J and SECAM-H/V. CONTROL: All controls including adjustments for H and SC on the front panel. Control of contrast, brightness, color saturation, hue (NTSC only), RS 232 and chroma / luma timing (H and V). -

Brighteye 56 Manual

BrightEye 56 HD/SD/Analog Test Signal and Sync Pulse Generator User Guide Revision 1.3 SW v1.2.1 Clearly, Ensemble wants to be in the broadcast equipment business. It’s so rare anymore to find a company of this caliber that has not been gobbled up by a large corporation. They are privately held so they don’t have to please the money people. They really put their efforts into building products and working with customers. I’m really happy with the BrightEye products and Ensemble’s service, and even more important my engineers are happy. We’ve continued to upgrade the product and add more cards. We will be rebuilding our production control room and we will use BrightEye again. ~ Don McKay, Vice President Engineering, Oregon Public Broadcasting Who is Ensemble Designs? By Engineers, For Engineers In 1989, a former television station engineer who loved BrightEye frames handle 270 designing and building video equipment, decided to Mb/s, 1.5 Gb/s and 3 Gb/s signals, start a new company. He relished the idea of taking audio and MPEG signals. Used an existing group of equipment and adding a few worldwide in broadcast, mobile, production, and post. special pieces in order to create an even more elegant ensemble. So, he designed and built his first product and the company was born. Focused On What You Need As the company has grown, more former TV station We’re focused on engineers have joined Ensemble Designs and this wealth processing gear– of practical experience fuels the company’s innovation. -

![United States Patent [19] M 3.551111](https://docslib.b-cdn.net/cover/0254/united-states-patent-19-m-3-551111-4480254.webp)

United States Patent [19] M 3.551111

United States Patent [19] [11] Patent Number: 4,660,074 Schine [45] Date of Patent: Apr. 21, 1987 [54] NTSC COLOR TELEVISION Primary Examiner-John W. Shepperd TRANSMISSION WITHOUT CHROMA Attorney, Agent, or Firm—Freilich, Hombaker, Rosen & CRAWL Fernandez [76] Inventor: Jonathan M. Schine, 626 S. Hudson [57] ABSTRACT Ave" Los Angeles’ Calif‘ 90005 An improved color television transmission compatible [21] Appl' NW 787,156 with NTSC standards produces a controlled horizontal _ scan rate at about 15,768 Hz with 227 cycles of color [22] Flled: Oct- 15’ 1985 subcarrier per line, and a controlled horizontal scan rate [51] Int. cu ...................... .. H04N 9/44; H04N 11/14 at about 60-070 HZ to Produce frames of two interlaced [52] ‘‘‘‘ " 358/16; 353/17 ?elds each at a rate of about 30.035 Hz with 227.5 cycles [58] Field of Search ...................... .. 358/11, 12, 16, 17 Qfthe color subcarrier Per ?eld Phase Shifted 180° 0f the color subcarrier at the beginning of each ?eld, thereby [56] References Cited eliminating “chroma crawl,” and reducing the size of Us, PATENT DOCUMENTS the teeth in the “zipper" effect produced by NTSC encoded color at the edge of vertical color borders. The """"""""""""""""""" vertical scan rate is controlled by dividing a clock fre 4’295’157 10/1981 Machid 358/17 quency of four times the color subciar‘rier by four to 4$001908 2/1985 Mandeberg 358/11 produce the color subcarner, and dividing the clock 4,517,587 5/1985 Aizawa et aL _ 358/17 frequency by some set of multiples to produce the hori 4,s5s,349 12/1985 Sasuki ................................ -

SPG8000A Master Sync / Master Clock Reference

Master Sync / Master Clock Reference Generator SPG8000A datasheet Dual hot-swappable power supplies ensure continuous availability of The SPG8000A is a precision multiformat video signal generator, suitable reference signals for master synchronization and reference applications. It provides multiple Easy to manage with Web-based interface for remote configuration and video reference signals, such as black burst, HD tri-level sync, and serial SNMP for status and alert information digital and composite analog test patterns, and it provides time reference signals such as time code, NTP (Network Time Protocol), and IEEE 1588 PTP (Precision Time Protocol). Applications Sync generator and time reference generator for broadcast, studio, Key features mobile, and post-production facilities Multiple independent black burst and HD tri-level sync outputs provide Master or slave (genlock) operation for distributed system architectures all the video reference signals required in a video broadcast or production facility Video equipment verification, facility link testing, and display calibration Four LTC outputs, VITC on black burst outputs, and NTP server provide time reference signals in a variety of formats Master video synchronization and time PTP (IEEE 1588) support, including SMPTE ST 2059-2 and AES67 reference generator profiles The base configuration includes three sync outputs that can be configured GPS/GLONASS-based synchronization gives an accurate time-of-day with independent output formats and independently adjustable timing reference and deterministic video phase reference across multiple offsets. With Option BG, four more analog outputs can be added. A high- independent systems accuracy, oven-controlled crystal oscillator provides a stable frequency reference for the system, or the pass-through genlock input can be used to Stay GenLock® and Holdover Recovery prevent synchronization shock lock to an external video reference or 10 MHz continuous wave signal. -

NTSC Studio Timing: Principles and Applications

NTSC Studio Timing: Principles and Applications —i •a r— ^ GRASS VALLEY GROUP A TEKTRONIX COMPANY NTSC Studio Timing: Principles and Applications Issue 3 u u u u u u u — u — u — u — u IT u u — u — I f U I T ¥ II U II IT U I T i r I I I I F_r~LJLJl_L_LJl i i i r~r~\i Produced and Published by Grass Valley Group, Inc. Preface This booklet on studio timing has been structured to meet a variety of needs. The video novice can read through from Section 1, noting the margin definitions, and gain a general understanding of the subject Section 2, starting with system timing, offers approaches and options for the timing of a television facility. Section 3 emphasizes the importance of SC/H phase, defines and clarifies it, and explains how to achieve it © 1988 by the Grass Valley Group, Inc., Grass Valley, California, U.S.A. Printed in U.S.A. All rights reserved. Contents of this publication may not by reproduced in any form without permission of The Grass Valley Group, Inc. Products of The Grass Valley Group, Inc. are covered by U.S.A. and Foreign Patents and/or Patents Pending. /fpN Contents /§P^\ Section 1 Video Basics Section 2 System Timing ........ ....... 5 Studio Planning.................................. 6 System Design Using Delay.............. 9 NTSC Standard 12 System Design Using Sync Generators 14 Section 3 SC/H Phase 18 NTSC Studio Timing: Principles and Applications The most critical design in every teleproduction facility is the system Introduction timing. The final video product will always reflect the quality of the system design. -

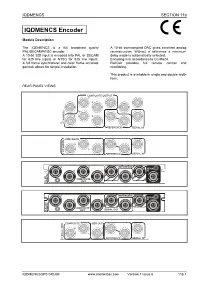

IQDMENCS Encoder C

IQDMENCS SECTION 11b IQDMENCS Encoder C Module Description The IQDMENCS is a full broadcast quality A 10-bit oversampled DAC gives excellent analog PAL/SECAM/NTSC encoder reconstruction. Without a reference a minimum A 10-bit SDI input is encoded into PAL or SECAM delay mode is automatically selected. for 625 line inputs or NTSC for 525 line inputs. Encoding is in accordance to CCIR624. A full frame synchronizer and color frame accurate RollCall provides full remote control and genlock allows for simple installation. monitoring. This product is available in single and double width form. REAR PANEL VIEWS COMPOSITE OUTPUT 3 1 2 IQDMENCS 5 6 4 2 -2 REFERENCE SERIAL IN IQDMENCS-1 COMPOSITE 3 1 2 REFERENCE SERIAL IN IQDMENCS/SES-1-S COMPOSITE SER OUT 2 1 1 REFERENCE SERIAL IN IQDMENCSOPS 040304 www.snellwilcox.com Version 1 Issue 6 11b.1 IQDMENCS SECTION 11b Versions of the module cards available are: IQDMENCS-2 6 Composite output genlockable encoder Double width module IQDMENCS-1 3 Composite output genlockable encoder Single width module IQDMENCS-1-S 2 Composite 1 Serial output genlockable encoder Single width module IQDMENCS-1A 4 Composite output genlockable encoder Single width module IQDMENCS-1A-S 3 Composite 2 Serial output genlockable encoder Single width module IQDMENCS-2A-S 5 Composite 2 Serial output genlockable encoder Double width module Note that there are two styles of rear panels available. They are not interchangeable between the two styles of enclosures. However, the cards may be fitted into any style of enclosure. ‘A’ Style Enclosure ‘O’ Style Enclosures Rear panels with the suffix A may only be fitted Rear panels without the suffix A may only be fitted into the ‘A’ style enclosure shown below.