Department of Electronics and Communication Engineering Name : …………………………………… Reg No Branch : ……

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Optoelectronic Oscillators: Recent and Emerging Trends Optoelectronic Oscillators: Recent and Emerging Trends

Optoelectronic Oscillators: Recent and Emerging Trends Optoelectronic Oscillators: Recent and Emerging Trends October 11, 2018 Afshin S. Daryoush(1), Ajay Poddar(2), Tianchi Sun(1), and Ulrich L. Rohde(2), Drexel University(1); Synergy Microwave(2) Highly stable oscillators are key components in many important applications where coherent processing is performed for improved detection. The optoelectronic oscillator (OEO) exhibits low phase noise at microwave and mmWave frequencies, which is attractive for applications such as synthetic aperture radar, space communications, navigation and meteorology, as well as for communications carriers operating at frequencies above 10 GHz, with the advent of high data rate wireless for high speed data transmission. The conventional OEO suffers from a large number of unwanted, closely-spaced oscillation modes, large size and thermal drift. State-of-the- art performance is reported for X- and K-Band OEO synthesizers incorporating a novel forced technique of self-injection locking, double self phase-locking. This technique reduces phase noise both close-in and far-away from the carrier, while suppressing side modes observed in standard OEOs. As an example, frequency synthesizers at X-Band (8 to 12 GHz) and K-Band (16 to 24 GHz) are demonstrated, typically exhibiting phase noise at 10 kHz offset from the carrier better than −138 and −128 dBc/Hz, respectively. A fully integrated version of a forced tunable low phase noise OEO is also being developed for 5G applications, featuring reduced size and power consumption, less sensitivity to environmental effects and low cost. Electronic oscillators generate low phase noise signals up to a few GHz but suffer phase noise degradation at higher frequencies, principally due to low Q-factor resonators. -

Multivibrator Circuits

Multivibrator Circuits Bistable multivibrators Multivibrators Circuits characterized by the existence of some well defined states, amongst which take place fast transitions, called switching processes. A switching process is a fast change in value of a current or a voltage, the fast process implying the existence of positive reaction loops, or negative resistances. The switching can be triggered from outside, by means of command signals, or from inside, by slow charge accumulation and the reaching of a critical state by certain electrical quantities in the circuit. Circuits have two, well defined states, which can be either stable or unstable A stable state is a state, in which the circuit, in absence of a driving signal, can remain for an unlimited period of time The circuit can remain in an unstable state only for a limited period of time, after which, in the absence of any exterior command signals, it switches into the other state. The multivibrator circuits can be grouped, according to their number of stable (steady) states, into: - flip-flops (bistable circuits) with both states being stable - monostable circuits , having a stable and an unstable state - astable circuits , with both states being unstable Flip-flop circuits The main feature of the flip-flop circuits is the existence of two stable states, in which the circuit may remain for a long time. The switching from one state to the other is triggered by command signals Flip flop: an example for a sequential circuit (a circuit with outputs that present logical values depending on a certain sequence of signals, that have previously existed in the circuit). -

Analysis of BJT Colpitts Oscillators - Empirical and Mathematical Methods for Predicting Behavior Nicholas Jon Stave Marquette University

Marquette University e-Publications@Marquette Master's Theses (2009 -) Dissertations, Theses, and Professional Projects Analysis of BJT Colpitts Oscillators - Empirical and Mathematical Methods for Predicting Behavior Nicholas Jon Stave Marquette University Recommended Citation Stave, Nicholas Jon, "Analysis of BJT Colpitts sO cillators - Empirical and Mathematical Methods for Predicting Behavior" (2019). Master's Theses (2009 -). 554. https://epublications.marquette.edu/theses_open/554 ANALYSIS OF BJT COLPITTS OSCILLATORS – EMPIRICAL AND MATHEMATICAL METHODS FOR PREDICTING BEHAVIOR by Nicholas J. Stave, B.Sc. A Thesis submitted to the Faculty of the Graduate School, Marquette University, in Partial Fulfillment of the Requirements for the Degree of Master of Science Milwaukee, Wisconsin August 2019 ABSTRACT ANALYSIS OF BJT COLPITTS OSCILLATORS – EMPIRICAL AND MATHEMATICAL METHODS FOR PREDICTING BEHAVIOR Nicholas J. Stave, B.Sc. Marquette University, 2019 Oscillator circuits perform two fundamental roles in wireless communication – the local oscillator for frequency shifting and the voltage-controlled oscillator for modulation and detection. The Colpitts oscillator is a common topology used for these applications. Because the oscillator must function as a component of a larger system, the ability to predict and control its output characteristics is necessary. Textbooks treating the circuit often omit analysis of output voltage amplitude and output resistance and the literature on the topic often focuses on gigahertz-frequency chip-based applications. Without extensive component and parasitics information, it is often difficult to make simulation software predictions agree with experimental oscillator results. The oscillator studied in this thesis is the bipolar junction Colpitts oscillator in the common-base configuration and the analysis is primarily experimental. The characteristics considered are output voltage amplitude, output resistance, and sinusoidal purity of the waveform. -

Npn Transistor Pnp Transistor

ELL 100 - Introduction to Electrical Engineering LECTURE 23: BIPOLAR JUNCTION TRANSISTOR (BJT) 1 CONTENTS • Introduction • Construction & working principle of BJT • Common-base and common-emitter circuits 2 BJT INTRODUCTION • Bipolar: Both electrons and holes (positively charged quasi- particles, absence of electron) contribute to current flow • Junction: Consists of an n- (or p-) type silicon sandwiched between two p- (or n-) type silicon regions • Transistor: 3-terminal device (Base, Emitter, Collector) Two types: npn & pnp 3 Bipolar Junction Transistor (BJT) 4 Various Types of General-Purpose or Switching Transistors: (a) Low Power (b) Medium Power (c) Medium to high power 5 First Working Transistor, Invented in 1947. Earliest Raytheon Blue transistors, Replica of 1st device made by first appearing in 1955 Shockley, Bardeen & Brattain at Bell Labs 6 Applications: Transistor As Switch 7 Applications: Transistor As Relay (Switch) Single channel 5V relay breakout board 8 Applications: Transistor As Amplifier TDA7297 Power Amplifier & Audio amplifier Module 9 Applications: Transistors in Radio 10 Applications: Transistor in Oscillator Colpitts Oscillator 11 Applications: Transistor in Oscillator Astable Multivibrator 12 Transistors in Timer Circuits 13 Transistor As NOT Gate 14 Transistors in NAND Gate 15 Bipolar Junction Transistor (BJT) The three terminals of the BJT are called the Base (B), the Collector (C) and the Emitter (E). n p p n n p npn transistor pnp transistor 16 Bipolar Junction Transistor (BJT) npn pnp 17 p-n-p Transistor IE, IB, IC – Emitter, Base and Collector currents VEB, VCB, VCE – Emitter-Base, Collector-Base and Collector-Emitter voltages 18 n-p-n Transistor IE, IB, IC – Emitter, Base and Collector currents VEB, VCB, VCE – Emitter-Base, Collector-Base and Collector-Emitter voltages 19 BJT Construction 20 Bipolar Junction Transistor (BJT) Basic Principle The voltage between two terminals (B and E) controls the current through the third terminal (C). -

Silicon Bipolar Distributed Oscillator Design and Analysis

Science World Journal Vol 9 (No 4) 2014 www.scienceworldjournal.org ISSN 1597-6343 SILICON BIPOLAR DISTRIBUTED OSCILLATOR DESIGN AND ANALYSIS Article Research Full Length Aku, M. O. and *Imam, R. S. Department of Physics, Bayero University, Kano-Nigeria * Department of Physics, Kano University of Science and Technology, Wudil-Nigeria ABSTRACT between its input and output. It can be shown that there is a The design of high frequency silicon bipolar oscillator using trade-off between the bandwidth and delay in an amplifier common emitter (CE) with distributed output and analysis is (Lee, 1998). Distributed amplification provides a means to carried out. The general condition for oscillation and the take advantage of this trade-off in applications where the resulting analytical expressions for the frequency of delay is not a critical specification of the system and can be oscillators were reviewed. Transmission line design was compromised in favour of the bandwidth (distributed carried out using Butterworth LC filters in which the oscillator). It is noteworthy that the physical size of a normalised values and where used to obtain the distributed amplifier does not have to be comparable to the actual values of the inductors and capacitors used; this wavelength for it to enhance the bandwidth. Dividing the gain largely determines the performance of distributed oscillators. between multiple active devices avoids the concentration of The values of inductor and capacitors in the phase shift the parasitic at one place and hence eliminates a dominant network are used in tuning the oscillator. The simulated pole scenario in the frequency domain transfer function. -

Chapter 3: Oscillators and Waveform-Shaping Circuits

mywbut.com CHAPTER3:OSCILLATORSANDWAVEFORM-SHAPING CIRCUITS Inthedesignofelectronicsystems,theneed frequentlyarises forsignals havingprescribed standardwaveforms(e.g.,sinusoidal, square,triangle,pulse,etc).Thesewaveformsarecommonly usedincomputers,controlsystems,communicationsystemsandtestmeasurementsystems. Therearetwocommonwaysforgeneratingsinusoids: 1. Positivefeedbackloopwithnon-lineargainlimiting 2. Appropriatelyshapingotherwaveformssuchasatrianglewaves. Circuitsthatdirectlygeneratesquare,triangleandpulsewaveformsgenerallyemploycircuit blocksknownasmultivibrators.Threebasictypesarebistable,astableandmonostable. I.SINUSOIDALOSCILLATORS: Commonly referred to as linear sine-wave oscillators although some forms of non-linearity havetobeemployedtolimittheoutputamplitude.Analysisofthecircuitsismoredifficultass-plane analysis cannot be directly applied to the non-linear part of the circuit. The basic structure of a sinusoidal oscillator consists of an amplifier and a frequency selective network connected in a positivefeedbackloop. AmplifierA xS + Σ xO + xf Freq.Selective networkβ Figure1:Basicstructureofasinusoidaloscillator. Apositive-feedbackloopisformedbyanamplifierandafrequency-selectivenetwork.Inan actualoscillatorcircuit,noinputsignalwillbepresent;hereaninputsignalxsisemployedtohelp explaintheprincipleofoperation.NotethatthefeedbacksignalXFissummedwithapositivesign: A(s) A (s) = f 1− A(s) β (s) Theloopgainis: )s(L =A(s) β (s) Andthecharacteristicequationcanbewrittenas: 1-L(s)=0 If at a specific frequency -

Durham Research Online

Durham Research Online Deposited in DRO: 07 November 2018 Version of attached le: Accepted Version Peer-review status of attached le: Peer-reviewed Citation for published item: Brennan, D.R. and Chan, H.K. and Wright, N.G. and Horsfall, A.B. (2018) 'Silicon carbide oscillators for extreme environments.', in Low power semiconductor devices and processes for emerging applications in communications, computing, and sensing. Boca Raton, FL: CRC Press, pp. 225-252. Devices, circuits, and systems. Further information on publisher's website: https://doi.org/10.1201/9780429503634-10 Publisher's copyright statement: This is an Accepted Manuscript of a book chapter published by Routledge in Low power semiconductor devices and processes for emerging applications in communications, computing, and sensing on 31 July 2018 available online: http://www.routledge.com/9780429503634 Additional information: Use policy The full-text may be used and/or reproduced, and given to third parties in any format or medium, without prior permission or charge, for personal research or study, educational, or not-for-prot purposes provided that: • a full bibliographic reference is made to the original source • a link is made to the metadata record in DRO • the full-text is not changed in any way The full-text must not be sold in any format or medium without the formal permission of the copyright holders. Please consult the full DRO policy for further details. Durham University Library, Stockton Road, Durham DH1 3LY, United Kingdom Tel : +44 (0)191 334 3042 | Fax : +44 (0)191 334 2971 https://dro.dur.ac.uk Silicon Carbide Oscillators for Extreme Environments D.R. -

Quartz Resonator & Oscillator Tutorial

Rev. 8.5.3.6 Quartz Crystal Resonators and Oscillators For Frequency Control and Timing Applications - A Tutorial January 2007 John R. Vig Consultant. Most of this Tutorial was prepared while the author was employed by the US Army Communications-Electronics Research, Development & Engineering Center Fort Monmouth, NJ, USA [email protected] Approved for public release. Distribution is unlimited NOTICES Disclaimer The citation of trade names and names of manufacturers in this report is not to be construed as official Government endorsement or consent or approval of commercial products or services referenced herein. Table of Contents Preface………………………………..……………………….. v 1. Applications and Requirements………………………. 1 2. Quartz Crystal Oscillators………………………………. 2 3. Quartz Crystal Resonators……………………………… 3 4. Oscillator Stability………………………………………… 4 5. Quartz Material Properties……………………………... 5 6. Atomic Frequency Standards…………………………… 6 7. Oscillator Comparison and Specification…………….. 7 8. Time and Timekeeping…………………………………. 8 9. Related Devices and Applications……………………… 9 10. FCS Proceedings Ordering, Website, and Index………….. 10 iii Preface Why This Tutorial? “Everything should be made as simple as I was frequently asked for “hard-copies” of possible - but not simpler,” said Einstein. The the slides, so I started organizing, adding main goal of this “tutorial” is to assist with some text, and filling the gaps in the slide presenting the most frequently encountered collection. As the collection grew, I began concepts in frequency control and timing, as receiving favorable comments and requests simply as possible. for additional copies. Apparently, others, too, found this collection to be useful. Eventually, I I have often been called upon to brief assembled this document, the “Tutorial”. visitors, management, and potential users of precision oscillators, and have also been This is a work in progress. -

Experiment No: 14 ASTABLE MULTIVIBRATOR USING IC

Experiment No: 14 ASTABLE MULTIVIBRATOR USING IC 555 AIM To design and set up astable multivibrator of 1000 Hz frequency and 60% duty cycle using IC 555 THEORY IC 555 timer is an analog IC used for generating accurate time delay or oscillations. The entire circuit is usually housed in an 8-pin package as specified in figures 1 & 2 below. A series connection of three resistors inside the IC sets the reference voltage levels to the two 2 1 comparators at V and V , the output of these comparators setting or resetting the flip- 3 CC 3 CC flop unit. The output of the flip-flop circuit is then brought out through an output buffer stage. In the stable state the 푄 output of the flip-flop is high (ie Q low). This makes the output (pin 3) low because of the buffer which basically is an inverter.The flip-flop circuit also operates a transistor inside the IC, the transistor collector usually being driven low to discharge a timing capacitor connected at pin 7. The description of each pin s described below, Pin 1: (Ground): Supply ground is connected to this pin. Pin 2: (Trigger): This pin is used to give the trigger input in monostable multivibrator. When trigger of amplitude greater than (1/3)Vcc is applied to this terminal circuit switches to quasi-stable state. Pin 3: (Output) Pin 4 (Reset): This pin is used to reset the output irrespective of input. A logic low at this pin will reset output. For normal operation pin 4 is connected to Vcc. -

An Electronic Switch ?Or Transient Studies

AN ELECTRONIC SWITCH ?OR TRANSIENT STUDIES A THESIS Presented to the Faculty of the Division of Graduate Studies Georgia Institute of Technology In Partial Fulfillment of the Requirements for the Degree Master of Science in Slectrical Engineering by Marshall Joseph McCann September 1949 107545 ii AN ELECTRONIC SWITCH FOR TRANSIENT STUDIES Approved: zf r ~~v Bate Approved by Chairman A up. d±, f^4f ACKNOWLEDGMENTS I wish to express my sincerest thanks to Prof. M. A. Honnell for his patient guidance and assistance, which were an immense aid in the prosecution of this work. I am also indebted to the Photographic and Repro duction Laboratory at the State Engineering Experiment Station of the Georgia Institute of Technology for their splendid cooperation with the photographic work herein. iv TABLE 0? CONTENTS PAGE Acknowledgments iii List of figures vi I- Introduction 1 II- A Survey of the Literature 3 Mechanical Systems.. • 3 Electronic Systems 4 III- Design Considerations for an Electronic Switch 8 General , , 8 Possible Approaches 8 IV- The Switch 12 V- The Square Wave Generator 16 Design Requirement s 16 Symmetrical Multivibrator 16 Improvement of Waveform 22 VI- The Synchronizing Section 37 General 37 Phase Shifting 27 Amplification and V/ave shaping 29 Synchronization of the Multivibrator 39 Summary of the Synchronizing Action 31 VII- Operation 34 VIII- Siamples of Operation 37 Lumped Constant Circuits 37 V P-4GE VIII- Examples of Operation (continued) Transmission Line Transients 41 IX- Summary • 46 appendix I, Analysis of Plate-Inductance Compensation of the Multivibrator 47 appendix II, Scaling of Circuits for A-C Transients 50 appendix III, Parts List 55 Bibliography ... -

How to Configure a 555 Timer IC 555 Timer Tutorial

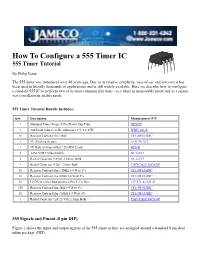

How To Configure a 555 Timer IC 555 Timer Tutorial By Philip Kane The 555 timer was introduced over 40 years ago. Due to its relative simplicity, ease of use and low cost it has been used in literally thousands of applications and is still widely available. Here we describe how to configure a standard 555 IC to perform two of its most common functions - as a timer in monostable mode and as a square wave oscillator in astable mode. 555 Timer Tutorial Bundle Includes: Qty. Description Manufacturer P/N 1 Standard Timer Single 8-Pin Plastic Dip Tube NE555P 1 400-Point Solderless Breadboard 3.3"L x 2.1"W WBU-301-R 10 Resistor Carbon Film 10kΩ CF1/4W103JRC 1 9V Alkaline Battery ALK 9V 522 1 9V Battery Snap with 6" 26AWG Leads BC6-R 2 3-Pin SPDT Slide Switch SS-12E17 2 Radial Capacitor 0.01µF 2.54mm Bulk SS-12E17 1 Radial Capacitor 4.7µF 2.5mm Bulk TAP475K025SCS-VP 10 Resistor Carbon Film 1.0MΩ 1/4 Watt 5% CF1/4W105JRC 10 Resistor Carbon Film 220Ω 1/4 Watt 5% CF1/4W221JRC 10 LED Uni-Color Red 660nm 2-Pin T-1¾ Box UT1871-81-M1-R 100 Resistor Carbon Film 3kΩ 1/4 Watt 5% CF1/4W302JRC 10 Resistor Carbon Film 330kΩ 1/4 Watt 5% CF1/4W334JRC 1 Radial Capacitor 1µF 25 Volt 2.5mm Bulk TAP105K025SCS-VP 555 Signals and Pinout (8 pin DIP) Figure 1 shows the input and output signals of the 555 timer as they are arranged around a standard 8 pin dual inline package (DIP). -

UNIVERSITY of NEVADA, RENO Introduction to Quartz Resonator

UNIVERSITY OF NEVADA, RENO Introduction to Quartz Resonator Based Electronic Oscillators and Development of Electronic Oscillators Using Inverted-Mesa Etched Quartz Resonators A thesis submitted on partial fulfillment of the requirements for the degree of MASTER OF SCIENCE IN ELECTRICAL ENGINEERING By Matthew B. Anthony Thesis Advisor Dr. Indira Chatterjee August 2009 Copyright by Matthew B. Anthony 2009 All Rights Reserved THE GRADUATE SCHOOL We recommend that the thesis prepared under our supervision by MATTHEW B. ANTHONY entitled Introduction To Quartz Resonator Based Electronic Oscillators And Development Of Electronic Oscillators Using Inverted-Mesa Etched Quartz Resonators be accepted in partial fulfillment of the requirements for the degree of MASTER OF SCIENCE Indira Chatterjee, Ph.D., Advisor Bruce P. Johnson, Ph.D., Committee Member Scott Talbot, M.S., Committee Member Ronald Phaneuf, Ph.D., Graduate School Representative Marsha H. Read, Ph. D., Associate Dean, Graduate School August, 2009 i ABSTRACT The current work is primarily focused on the topic of the advancement of low phase noise and low jitter quartz crystal based electronic oscillators to frequencies beyond those presently available using quartz resonators that are manufactured using the traditional method that processes the entire sample to a uniform thickness. The method of inverted-mesa etching allows the resonant part of the quartz sample to be made much thinner than the remainder of the sample – enabling higher resonant frequencies to be achieved. The current work will introduce and discuss the importance of phase noise and jitter in electronic oscillator applications such as wireless communication systems and sampled data systems. General oscillator and quartz resonator background will be provided to facilitate the understanding of the oscillator circuit used herein.