4.0 Recommended Motherboard Configuration for Intel-Based Electronic Classroom Student Computing Stations

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Reviving the Development of Openchrome

Reviving the Development of OpenChrome Kevin Brace OpenChrome Project Maintainer / Developer XDC2017 September 21st, 2017 Outline ● About Me ● My Personal Story Behind OpenChrome ● Background on VIA Chrome Hardware ● The History of OpenChrome Project ● Past Releases ● Observations about Standby Resume ● Developmental Philosophy ● Developmental Challenges ● Strategies for Further Development ● Future Plans 09/21/2017 XDC2017 2 About Me ● EE (Electrical Engineering) background (B.S.E.E.) who specialized in digital design / computer architecture in college (pretty much the only undergraduate student “still” doing this stuff where I attended college) ● Graduated recently ● First time conference presenter ● Very experienced with Xilinx FPGA (Spartan-II through 7 Series FPGA) ● Fluent in Verilog / VHDL design and verification ● Interest / design experience with external communication interfaces (PCI / PCIe) and external memory interfaces (SDRAM / DDR3 SDRAM) ● Developed a simple DMA engine for PCI I/F validation w/Windows WDM (Windows Driver Model) kernel device driver ● Almost all the knowledge I have is self taught (university engineering classes were not very useful) 09/21/2017 XDC2017 3 Motivations Behind My Work ● General difficulty in obtaining meaningful employment in the digital hardware design field (too many students in the field, difficulty obtaining internship, etc.) ● Collects and repairs abandoned computer hardware (It’s like rescuing puppies!) ● Owns 100+ desktop computers and 20+ laptop computers (mostly abandoned old stuff I -

Linux Hardware Compatibility HOWTO

Linux Hardware Compatibility HOWTO Steven Pritchard Southern Illinois Linux Users Group [email protected] 3.1.5 Copyright © 2001−2002 by Steven Pritchard Copyright © 1997−1999 by Patrick Reijnen 2002−03−28 This document attempts to list most of the hardware known to be either supported or unsupported under Linux. Linux Hardware Compatibility HOWTO Table of Contents 1. Introduction.....................................................................................................................................................1 1.1. Notes on binary−only drivers...........................................................................................................1 1.2. Notes on commercial drivers............................................................................................................1 1.3. System architectures.........................................................................................................................1 1.4. Related sources of information.........................................................................................................2 1.5. Known problems with this document...............................................................................................2 1.6. New versions of this document.........................................................................................................2 1.7. Feedback and corrections..................................................................................................................3 1.8. Acknowledgments.............................................................................................................................3 -

810 Chipset: System Block Diagram

SUPER ® SUPER P6SWA SUPER P6SWD USER’S AND BIOS MANUAL Revision 1.3 The information in this User’s Manual has been carefully reviewed and is believed to be accurate. The vendor assumes no responsibility for any inaccuracies that may be contained in this document, makes no commitment to update or to keep current the information in this manual, or to notify any person or organization of the updates. Please Note: For the most up-to-date version of this manual, please see our web site at www.supermicro.com. SUPERMICRO COMPUTER reserves the right to make changes to the product described in this manual at any time and without notice. This product, including software, if any, and documentation may not, in whole or in part, be copied, photocopied, reproduced, translated or reduced to any medium or machine without prior written consent. IN NO EVENT WILL SUPERMICRO COMPUTER BE LIABLE FOR DIRECT, INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES ARISING FROM THE USE OR INABILITY TO USE THIS PRODUCT OR DOCUMENTATION, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. IN PARTICULAR, THE VENDOR SHALL NOT HAVE LIABILITY FOR ANY HARDWARE, SOFTWARE, OR DATA STORED OR USED WITH THE PRODUCT, INCLUDING THE COSTS OF REPAIRING, REPLACING, INTEGRATING, INSTALLING OR RECOVERING SUCH HARDWARE, SOFTWARE OR DATA. Unless you request and receive written permission from SUPER MICRO COMPUTER, you may not copy any part of this document. Information in this document is subject to change without notice. Other products and companies referred to herein are trademarks or registered trademarks of their respective companies or mark holders. -

BSMS3-872C User Manual Rev 02

1 Electronic Emission Notices Federal Communications Commission (FCC) Statement This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to Part 15 of FCC Rules. These limits are designed to provide reasonable protection against harmful interference in a residential installation. This equipment generates, uses and can radiate radio frequency energy and, if not installed and used in accordance with instructions contained in this manual, may cause harmful interference to radio and television communications. However, there is no guarantee that interference will not occur in a particular installation. If this equipment does cause harmful interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one or more of the following measures: - REORIENT OR RELOCATE THE RECEIVING ANTENNA - INCREASE THE SEPARATION BETWEEN THE EQUIPMENT AND THE RECEIVER - CONNECT THE EQUIPMENT INTO AN OUTLET ON A CIRCUIT DIFFERENT FROM THAT OF THE RECEIVER - CONSULT THE DEALER OR AN EXPERIENCED AUDIO/TELEVISION TECHNICIAN NOTE: Connecting this device to peripheral devices that do not comply with Class B requirements, or using an unshielded peripheral data cable, could also result in harmful interference to radio or television reception. The user is cautioned that any changes or modifications not expressly approved by the party responsible for compliance could void the user’s authority to operate this equipment. To ensure that the use of this product does not contribute to interference, it is necessary to use shielded I/O cables. Copyright This manual is copyrighted with all rights reserved. -

810EMS1-C923 User Manual Rev 02

1 Electronic Emission Notices Federal Communications Commission (FCC) Statement This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to Part 15 of FCC Rules. These limits are designed to provide reasonable protection against harmful interference in a residential installation. This equipment generates, uses and can radiate radio frequency energy and, if not installed and used in accordance with instructions contained in this manual, may cause harmful interference to radio and television communications. However, there is no guarantee that interference will not occur in a particular installation. If this equipment does cause harmful interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one or more of the following measures: - REORIENT OR RELOCATE THE RECEIVING ANTENNA - INCREASE THE SEPARATION BETWEEN THE EQUIPMENT AND THE RECEIVER - CONNECT THE EQUIPMENT INTO AN OUTLET ON A CIRCUIT DIFFERENT FROM THAT OF THE RECEIVER - CONSULT THE DEALER OR AN EXPERIENCED AUDIO/TELEVISION TECHNICIAN NOTE: Connecting this device to peripheral devices that do not comply with Class B requirements, or using an unshielded peripheral data cable, could also result in harmful interference to radio or television reception. The user is cautioned that any changes or modifications not expressly approved by the party responsible for compliance could void the user’s authority to operate this equipment. To ensure that the use of this product does not contribute to interference, it is necessary to use shielded I/O cables. Copyright This manual is copyrighted with all rights reserved. -

Linux Hardware Compatibility HOWTO

Linux Hardware Compatibility HOWTO Steven Pritchard Southern Illinois Linux Users Group / K&S Pritchard Enterprises, Inc. <[email protected]> 3.2.4 Copyright © 2001−2007 Steven Pritchard Copyright © 1997−1999 Patrick Reijnen 2007−05−22 This document attempts to list most of the hardware known to be either supported or unsupported under Linux. Copyright This HOWTO is free documentation; you can redistribute it and/or modify it under the terms of the GNU General Public License as published by the Free software Foundation; either version 2 of the license, or (at your option) any later version. Linux Hardware Compatibility HOWTO Table of Contents 1. Introduction.....................................................................................................................................................1 1.1. Notes on binary−only drivers...........................................................................................................1 1.2. Notes on proprietary drivers.............................................................................................................1 1.3. System architectures.........................................................................................................................1 1.4. Related sources of information.........................................................................................................2 1.5. Known problems with this document...............................................................................................2 1.6. New versions of this document.........................................................................................................2 -

Covering the Spectrum of Intel Communications Products

NOTE: PLEASE ADJUST SPINE TO PROPER WIDTH The Communications and Embedded Products Source Book Source The Communications and Embedded Products The Communications Intel Corporation United States and Canada Intel Corporation Robert Noyce Building and Embedded Products 2200 Mission College Boulevard P.O. Box 58119 Santa Clara, CA 95052-8119 Source Book 2004 USA Phone: (408) 765-8080 Europe Intel Corporation (UK) Ltd. Pipers Way Swindon Wiltshire SN3 1RJ UK Phone: England (44) 1793 403 000 France (33) 1 4694 7171 Germany (49) 89 99143 0 Italy (39) 02 575 441 Israel (972) 2 589 7111 Netherlands (31) 20 659 1800 Asia Pacific Intel Semiconductor Ltd. 32/F Two Pacific Place 88 Queensway, Central Hong Kong SAR Phone: (852) 2844-4555 Japan Intel Kabushiki Kaisha P.O. Box 300-8603 Tsukuba-gakuen May 2004 5-6 Tokodai, Tsukuba-shi Ibaraki-ken 300-2635 Japan Phone: (81) 298-47-8511 South America Intel Semicondutores do Brasil Av. Dr Chucri Zaidan, 940- 10th floor Market Place Tower II 04583-906 Sao Paulo-SP-Brasil Phone: (55) 11 3365 5500 Copyright © 2004 Intel Corporation Intel, and the Intel logo are registered trademarks of Intel Corporation. * Other names and brands may be claimed as the property of others. Printed in USA/2004/10K/MD/HP Covering the spectrum Order No. 272676-012 of Intel communications products Communications and Embedded Products Source Book elcome to The Intel Communications and Embedded Products Sourcebook—2004, your Wcomplete reference guide for Intel’s Communications and Embedded products. As you look through this sourcebook, you will note that all of the sections have been updated to include the latest released products. -

IBM PC 1994 to 2000 - Withdrawn November 2000 - Version 212 IBM PC 300-486 Models - Withdrawn

PC Institute IBM Personal Systems Reference IBM PC 1994 to 2000 - withdrawn November 2000 - Version 212 IBM PC 300-486 models - withdrawn IBM PC Series 300: Memory SVGA Slots available (in bits) Available Diskette Write-back in MB; controller; 16 ISA/32 VESA/32 PCI IBM date Disk: std-max internal CPU / Upgrade L2 cache std / max memory Total bays Std Direct Type-model ms seek / interface MHz MHz std / max all 70 ns std / max ↓ 3.5" | 5.25"features Price 1 3 slot x 3 bay; VL/ISA ✂ 330-486 6571-LOA d opt: up to 2 IDE 486DX2-66/33 DX4/P24T 0KB 256 4 /128 Cirrus Lo 3/1/0 ❘ $ 949➷Jul 95 ✂ 330-486 -L5B d 540M-2.0G 12 IDE 486DX2-66/33 DX4/P24T 4 /128 GD5430 3/1/0 Àª ❘@ W 1064➷Apr 95 ✂ 330-486 " -L5C d 540M-2.0G 12 IDE 486DX2-66/33 DX4/P24T " " 4 /128 VL-Bus 3/1/0 ÀÀ ❘@ W 1064➷Jul 95 ✂ 330-486 " -L5F d 540M-2.0G 12 IDE 486DX2-66/33 DX4/P24T " " 4 /128 1 / 1 MB 3/1/0 ÀÀ ❘@ W 1236➷Apr 95 ✂ 330-486 " -L5K d 540M-2.0G 12 IDE 486DX2-66/33 DX4/P24T " " 8 /128 " 3/1/0 ÀÀ ❘@ 3 1236➷Jul 95 ✂ 330-486 " -WOA d opt: up to 2 IDE 486DX4-100/33 P24CT " " 4 /128 " 3/1/0 ÀÀ ❘@ 1064➷Jul 95 ✂ 330-486 " -W5F d 540M-2.0G 12 IDE 486DX4-100/33 P24CT " " 8 /128 " 3/1/0 Àª ❘@ 3 1351➷Apr 95 ✂ ÀÀ ❘@ ➷ 330-486 " -W5K d 540M-2.0G 12 IDE 486DX4-100/33 P24CT " " 8 /128 3/1/0 ÀÀ @ 3 1351 Jul 95 3 slot x 3 bay; PCI/ISA ✂ 330-486 6573-LOA d opt: up to 2 IDE 486DX2-66/33 DX4/P24T 0KB 256 4 /128 GD5430 3/0/2 ❘ 1035➷Jul 95 ✂ 330-486 -L5F d 540M-2.0G 12 IDE 486DX2-66/33 DX4/P24T " " 8 /128 1 / 1 MB 3/0/2 Àª ❘@ 3 1323➷Feb 95 ✂ 330-486 " -L5K d 540M-2.0G 12 IDE 486DX2-66/33 DX4/P24T -

1.2.6 CHIPSET to Reduce Number of Chips on the Motherboard Microprocessor Is Communication & Processing Are Integrat

1.2.6 CHIPSET To reduce number of chips on the motherboard Microprocessor is communication & processing are integrated into 2 or 3 chips These chips integrated with microprocessor Chip contain more than one logic like DMA logic Timer Logic Interrupt logic Peripheral interfaces logic These chips are called as chipset Chip manufactures are Intel VIA technologies (cyrix) Acer labs(ALI) Silicion integrated systems(SIS) OPT1 Chipset connected with processor On board memory System bus Audio & video Input/output ports INTEL PROCESSOR Advantages: Reduce chip count in a computer Reduce power requirement They shorten the signal paths and allow the circuits to operate at higher speeds Improvement reliability Reduce construction cost EXAMPLE CIRCUIT FOR INTEL CHIP 1) Intel 440GX chipset Processor support – Pentium II/III xenon processor multi processor support 2 processor Functional blocks – host bridge controller DMA interrupt controller time Memory support – SDRAM memory (2GB) Bus support – 100 MHZ system bus, PCI bus at 33MHZ Video and audio support – AGP devices Input/Output support – 2 USB ports 2) Intel 440BX chipset Processor support – Pentium II/III xenon processor multi processor support 2 processor Functional blocks: – AGA host bridge controller Memory support – 1GB of SDRAM/DIMM memory Bus support – 100 MHZ system bus, PCI bus at 33MHZ Video and audio support – AGP devices Input/Output support – 2 USB ports 3) Intel 440 ZX chipset Processor support – Pentium II/III processor Functional blocks – AGA -

Chapter 1 Introduction

CHAPTER 1 INTRODUCTION Chapter 1 INTRODUCTION The MS-6183 Micro ATX WH9 mainboard is a high-performance computer mainboard based on Intel® 810 chipset. The MS-6183 is designed for the Intel® Pentium II/III or CeleronTM processor for inexpensive business/personal desktop markets. The Intel® 810 chipset is the first generation Integrated Graphics chipset for the Intel® CeleronTM processor. The graphics accelerator archi- tecture consists of dedicated multi-media engines executing in parallel to deliver high performance 3D, 2D, and motion compensation video capabili- ties. An integrated centralized memory arbiter allocates memory bandwidth to multiple system agents to optimize system memory utilization. A new chipset component interconnect, the hub interface, is designed into the Intel 810 chipset to provide an efficient communication channel between the memory controller hub and I/O hub controller. The Intel 810 chipset contains three core components: the Graph- ics and Memory Controller Hub (GMCH), the I/O Controller Hub (ICHO/ICH) and the Firmware Hub (FWH). The GMCH integrates a 66/100MHz, P6 family system bus controller, integrates 2D/3D graphics accelerator, 100MHz SDRAM controller and high-speed hub interface for communication with the ICHO/ICH. The ICHO/ICH integrates an Ultra ATA/33(ICHO) or Ultra ATA/ 66(ICH) controller, USB host controller, LPC interface controller, FWH inteface conroller, PCI interface controller, AC’97 digital controller and a hub interface for communication with the GMCH. 1-1 CHAPTER 1 INTRODUCTION 1.1 Mainboard Features CPU l Slot 1 for Intel® Pentium® II/III or CeleronTM processor. l Supports 233MHz, 266MHz, 300MHz, 333MHz, 350MHz, 400MHz, 450MHz, 500MHz and faster processor. -

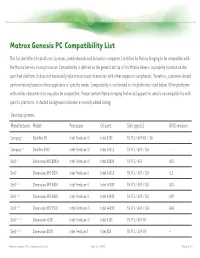

Matrox Genesis PC Compatibility List

Matrox Genesis PC Compatibility List This list identifies the platforms (systems, motherboards and industrial computers) certified by Matrox Imaging to be compatible with the Matrox Genesis vision processor. Compatibility is defined as the general ability of the Matrox Genesis to properly function on the specified platform. It does not necessarily take into account interaction with other expansion peripherals. Therefore, customers should perform testing based on their applications' specific needs. Compatibility is not limited to the platforms listed below. Other platforms with similar characteristics may also be compatible. Please contact Matrox Imaging Technical Support for details on compatibility with specific platforms. A shaded background indicates a recently added listing. Desktop systems Manufacturer Model Processor Chipset Slot type(s) BIOS revision Compaq 3 DeskPro EN Intel Pentium-III Intel 815E 5V PCI / AGP 4X / ISA - Compaq 1, 2 DeskPro 4000 Intel Pentium-III Intel 440LX 5V PCI / AGP / ISA - Dell 1, 2 Dimension XPS B800r Intel Pentium-III Intel 82820 5V PCI / AGP A00 Dell 2 Dimension XPS D300 Intel Pentium-II Intel 440LX 5V PCI / AGP / ISA 6.0 Dell 1, 2 Dimension XPS R400 Intel Pentium-II Intel 440BX 5V PCI / AGP / ISA A03 Dell 1, 2, 6 Dimension XPS R450 Intel Pentium-II Intel 440BX 5V PCI / AGP / ISA A09 Dell 1, 2, 3 Dimension XPS T550 Intel Pentium-III Intel 440BX 5V PCI / AGP / ISA A04 Dell 1, 2, 3, 6 Dimension 4100 Intel Pentium-III Intel 815E 5V PCI / AGP 4X - Dell 1, 2, 3, 6 Dimension 8100 Intel Pentium 4 Intel 850 5V -

Intel® CA810 Motherboard Technical Product Specification

Intel® CA810 Motherboard Technical Product Specification May 1999 Order Number 733082-001 The Intel CA810 motherboard may contain design defects or errors known as errata that may cause the product to deviate from published specifications. Current characterized errata are documented in the CA810 Motherboard Specification Update. Revision History Revision Revision History Date 001 Final release of the CA810 Motherboard Technical Product Specification. May 1999 This product specification applies only to standard CA810 motherboards with BIOS identifier 8C1A100A.86A. For BIOS Setup screen information for motherboards with BIOS identifier 8C1A100A.86R, refer to Section 4.1 on page 79. Other information in this specification applies to motherboards with either BIOS identifier 8C1A100A.86A or 8C1A100A.86R. Changes to this specification will be published in the CA810 Motherboard Specification Update before being incorporated into a revision of this document. Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications. Intel may make changes to specifications and product descriptions at any time, without notice. The CA810 motherboard may contain design defects or errors known as errata that may cause the product to deviate from published specifications.