Serial Communications Thomas C

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Bit & Baud Rate

What’s The Difference Between Bit Rate And Baud Rate? Apr. 27, 2012 Lou Frenzel | Electronic Design Serial-data speed is usually stated in terms of bit rate. However, another oft- quoted measure of speed is baud rate. Though the two aren’t the same, similarities exist under some circumstances. This tutorial will make the difference clear. Table Of Contents Background Bit Rate Overhead Baud Rate Multilevel Modulation Why Multiple Bits Per Baud? Baud Rate Examples References Background Most data communications over networks occurs via serial-data transmission. Data bits transmit one at a time over some communications channel, such as a cable or a wireless path. Figure 1 typifies the digital-bit pattern from a computer or some other digital circuit. This data signal is often called the baseband signal. The data switches between two voltage levels, such as +3 V for a binary 1 and +0.2 V for a binary 0. Other binary levels are also used. In the non-return-to-zero (NRZ) format (Fig. 1, again), the signal never goes to zero as like that of return- to-zero (RZ) formatted signals. 1. Non-return to zero (NRZ) is the most common binary data format. Data rate is indicated in bits per second (bits/s). Bit Rate The speed of the data is expressed in bits per second (bits/s or bps). The data rate R is a function of the duration of the bit or bit time (TB) (Fig. 1, again): R = 1/TB Rate is also called channel capacity C. If the bit time is 10 ns, the data rate equals: R = 1/10 x 10–9 = 100 million bits/s This is usually expressed as 100 Mbits/s. -

CS 61C: Great Ideas in Computer Architecture Dependability: Parity

CS 61C: Great Ideas in Computer Architecture Dependability: Parity, RAID, ECC Instructor: Alan Christopher 8/07/2014 Summer 2014 -- Lecture #27 1 Review of Last Lecture • MapReduce Data Level Parallelism – Framework to divide up data to be processed in parallel – Handles worker failure and laggard jobs automatically – Mapper outputs intermediate (key, value) pairs – Optional Combiner in-between for better load balancing – Reducer “combines” intermediate values with same key 8/07/2014 Summer 2014 -- Lecture #27 2 Agenda • Dependability • Administrivia • RAID • Error Correcting Codes 8/07/2014 Summer 2014 -- Lecture #27 3 Six Great Ideas in Computer Architecture 1. Layers of Representation/Interpretation 2. Technology Trends 3. Principle of Locality/Memory Hierarchy 4. Parallelism 5. Performance Measurement & Improvement 6. Dependability via Redundancy 8/07/2014 Summer 2014 -- Lecture #27 4 Great Idea #6: Dependability via Redundancy • Redundancy so that a failing piece doesn’t make the whole system fail 2 of 3 agree 1+1=2 1+1=2 1+1=2 1+1=1 FAIL! 8/07/2014 Summer 2014 -- Lecture #27 5 Great Idea #6: Dependability via Redundancy • Applies to everything from datacenters to memory – Redundant datacenters so that can lose 1 datacenter but Internet service stays online – Redundant routes so can lose nodes but Internet doesn’t fail – Redundant disks so that can lose 1 disk but not lose data (Redundant Arrays of Independent Disks/RAID) – Redundant memory bits of so that can lose 1 bit but no data (Error Correcting Code/ECC Memory) 8/07/2014 Summer -

Serial Communication Buses

Computer Architecture 10 Serial Communication Buses Made wi th OpenOffi ce.org 1 Serial Communication SendingSending datadata oneone bitbit atat oneone time,time, sequentiallysequentially SerialSerial vsvs parallelparallel communicationcommunication cable cost (or PCB space), synchronization, distance ! speed ? ImprovedImproved serialserial communicationcommunication technologytechnology allowsallows forfor transfertransfer atat higherhigher speedsspeeds andand isis dominatingdominating thethe modernmodern digitaldigital technology:technology: RS232, RS-485, I2C, SPI, 1-Wire, USB, FireWire, Ethernet, Fibre Channel, MIDI, Serial Attached SCSI, Serial ATA, PCI Express, etc. Made wi th OpenOffi ce.org 2 RS232, EIA232 TheThe ElectronicElectronic IndustriesIndustries AllianceAlliance (EIA)(EIA) standardstandard RS-232-CRS-232-C (1969)(1969) definition of physical layer (electrical signal characteristics: voltage levels, signaling rate, timing, short-circuit behavior, cable length, etc.) 25 or (more often) 9-pin connector serial transmission (bit-by-bit) asynchronous operation (no clock signal) truly bi-directional transfer (full-duplex) only limited power can be supplied to another device numerous handshake lines (seldom used) many protocols use RS232 (e.g. Modbus) Made wi th OpenOffi ce.org 3 Voltage Levels RS-232RS-232 standardstandard convertconvert TTL/CMOS-levelTTL/CMOS-level signalssignals intointo bipolarbipolar voltagevoltage levelslevels toto improveimprove noisenoise immunityimmunity andand supportsupport longlong cablecable lengthslengths TTL/CMOS → RS232: 0V = logic zero → +3V…+12V (SPACE) +5V (+3.3V) = logic one → −3V…−12V (MARK) Some equipment ignores the negative level and accepts a zero voltage level as the "OFF" state The "dead area" between +3V and -3V may vary, many receivers are sensitive to differentials of 1V or less Made wi th OpenOffi ce.org 4 Data frame CompleteComplete one-byteone-byte frameframe consistsconsists of:of: start-bit (SPACE), data bits (7, 8), stop-bits (MARK) e.g. -

A Gumstix-Based MIDI-To-OSC Converter

midOSC: a Gumstix-Based MIDI-to-OSC Converter Sebastien´ Schiesser Institute for Computer Music and Sound Technology Zurich University of the Arts Baslerstrasse 30, 8048 Zurich, Switzerland [email protected] Abstract [14], sent to the remote-controlled devices location and con- A MIDI-to-OSC converter is implemented on a commer- verted back to MIDI. Until now, this has been done at each cially available embedded linux system, tighly integrated conversion point through a Max/MSP patch running on a with a microcontroller. A layered method is developed which computer connected to a MIDI interface. This is very de- permits the conversion of serial data such as MIDI to OSC manding in terms of hardware: in the backstage system of formatted network packets with an overall system latency the mAe, a computer is dedicated to conversion purposes below 5 milliseconds for common MIDI messages. only. And when MIDI devices are present on stage, an ad- The Gumstix embedded computer provide an interest- ditional laptop with interface is required. ing and modular platform for the development of such an The mAe is intended to be modular and to support several embedded applications. The project shows great potential “I/O hubs”, where audio and control data are collected and to evolve into a generic sensors-to-OSC ethernet converter dispatched. In order to avoid dependence on a converting which should be very useful for artistic purposes and could computer at each hub, it seemed appropriate to use a dedi- be used as a fast prototyping interface for gesture acquisition cated converter which can run independently, be stacked in devices. -

Introduction to Serial Communication

Technical Tutorial Introduction to Serial Communication Introduction to Serial Communication Technical Tutorial 2002 – 12 - 06 Technical Tutorial Introduction to Serial Communication Table of Contents 1: Introduction 1.1. DCE and DTE Devices 1.2. Synchronous data transfer 1.3. Asynchronous data transfer 2: RS232 2.1. RS232 on DB9 (9-pin D-type connector) 2.2. RS232 on DB25 (25-pin D-type connector) 2.3. RS232 on RJ-45 2.4. Signal Description 2.5. Limitations of RS232 3: RS422 and RS485 3.1. RS422 Serial Communication 3.2. RS485 Serial Communication 3.3. Converters 4: Summary Table 5: Serial Interface of Sena Products 5.1. HelloDevice Lite series 5.2. HelloDevice Pro series 5.3. HelloDevice Super series 5.4. IALink100 Series 5.5. VTS Series 2 Technical Tutorial Introduction to Serial Communication 1. Introduction The purpose of this application note is to attempt to describe the main elements in Serial Communication. This application note attempts to cover enough technical details of RS232, RS422 and RS485. 1.1. DCE and DTE Devices DTE stands for Data Terminal Equipment, and DCE stands for Data Communications Equipment. These terms are used to indicate the pin-out for the connectors on a device and the direction of the signals on the pins. Your computer is a DTE device, while most other devices such as modem and other serial devices are usually DCE devices. RS-232 has been around as a standard for decades as an electrical interface between Data Terminal Equipment (DTE) and Data Circuit-Terminating Equipment (DCE) such as modems or DSUs. -

Lab 5: Serial Communication (Sci/Spi) and C Objectives Required Materials Introduction

University of Florida EEL 3744 –Spring 2018 Dr. Eric M. Schwartz Electrical & Computer Engineering Dept. 28-Mar-18 Page 1/8 Revision 7 LAB 5: SERIAL COMMUNICATION (SCI/SPI) AND C OBJECTIVES As discovered in Homework 4, the asynchronous UART • Understand the basic operation and structure of protocol utilizes a transfer rate (denoted as the baud rate), as asynchronous and synchronous serial communication, well as two physical connections for each device to i.e., SCI (UART) and SPI. communicate data, i.e., a pin for Receiving data (Rx), and a pin • Utilize C programming constructs to create functions to for Transmitting data (Tx). The only way that this protocol interact with the XMEGA’s USART and SPI systems. functions correctly is if both devices agree on a common baud • Learn how to use SPI communication to interact with an rate. external IMU sensor package. • Stream and plot real-time 3D (XYZ) acceleration data SPI, on the other hand, utilizes a shared clock signal connected using the XMEGA’s USART system and Atmel Studio’s between (at least) two devices (usually denoted as SCK), where Data Visualizer. only one device is known as the “master” device, and where the other devices are “slaves.” Full-duplex communication is REQUIRED MATERIALS possible with SPI (i.e., two devices can talk to each other at the • µPAD v2.0 Development Board same time), although the master always starts any • Robotics Backpack communication between the devices. When the master wants • Digilent/NI Analog Discovery (DAD/NAD) kit to transmit/receive data to/from the slave(s), it generates the • LSM330.h header file synchronized Serial Clock signal (SCK). -

EB215 Local Interconnect Network (LIN)

Freescale Semiconductor EB215 Engineering Bulletin Rev. 1.0, 03/2005 Local Interconnect Network (LIN) Physical Interface Difference Between MC33399 and MC33661 Introduction This engineering bulletin highlights the differences between two Local Interconnect Network (LIN) Physical Interfaces, namely the 33399 and the 33661. The LIN is a serial communication protocol designed to support automotive networks in conjunction with Controller Area Network (CAN). As the lowest level of a hierarchical network, LIN enables cost-effective communication with sensors and actuators when all the features of CAN are not required. The 33399 and the 33661 are physical layer components dedicated to automotive sub-bus applications. They offer speech communication from 1.0 kbps to 20 kbps. There are two main operating modes: Normal and Sleep. For feature information, refer to the device data sheets for 33399 and 33661 © Freescale Semiconductor, Inc., 2005. All rights reserved. Differences Guide Differences Guide This section should be used as a quick guide to determine the main differences between the devices in a similar family. Using Table 1, you can note the differences most relevant to your system/application. This engineering bulletin should be used in conjunction with the most recent specification for each device, to ensure that all differences have been captured. Table 1. Device Differences Parameter 33399 33661 LIN Protocol Specification Addresses LIN 1.3 Applications Addresses LIN 2.0 Applications Terminal Out and Package 8-terminal SOICN. 8-terminal SOICN. One baud rate operation: Two baud rate operations: Baud Rate Operation 1.0 kbps to 20 kbps • 1.0 kbps to 10 kbps • 1.0 kbps to 20 kbps Capable of: Capable of: Controlling an external switchable voltage • Controlling an external switchable voltage INH Output regulator. -

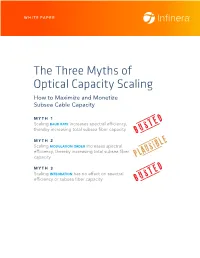

The Three Myths of Optical Capacity Scaling How to Maximize and Monetize Subsea Cable Capacity

WHITE PAPER The Three Myths of Optical Capacity Scaling How to Maximize and Monetize Subsea Cable Capacity MYTH 1 Scaling BAUD RATE increases spectral efficiency, thereby increasing total subsea fiber capacity MYTH 2 Scaling MODULATION ORDER increases spectral efficiency, thereby increasing total subsea fiber capacity MYTH 3 Scaling INTEGRATION has no effect on spectral efficiency or subsea fiber capacity AXES OF SCALABILITY Capacity/wave Capacity/device Baud G/Wave 100 Gbaud 800 Gb/s+ 2.4 Tb/s 600 Gb/s 66 Gbaud 1.2 Tb/s 200 Gb/s 500 Gb/s 33 Gbaud 100 Gb/s Modulation Fiber capacity 6 Carrier SC 1.2 @ 16QAM QPSK 8QAM 16QAM 237.5 GHz 64QAM CS-64QAM Multi-channel Super-channel Gb/s/unit FigureFigure 1: 1: Three The Three axes Axes of opticalof Optical scalability Scaling The Three Axes of Optical Scaling Figure 1 shows the three axes that are needed for optical scaling—baud rate, modulation order and integration. This paper will discuss scaling along each of these axes, but it is important to clarify exactly what is being scaled. There are at least three interpretations: • Increasing the data rate per wavelength • Increasing the capacity per line card or appliance • Increasing the total fiber capacity, or spectral efficiency These can potentially be scaled independently, or in concert as transponder technology evolves. In subsea deployments total fiber capacity, or spectral efficiency, is usually the dominant factor in determining overall network economics, so it becomes extremely important to understand the most effective way to achieve total capacity, especially when scaling baud rate has become a focal point for many dense wavelength-division multiplexing (DWDM) vendors today. -

PIC Serial Communication Modules

PIC Serial Communication Modules Synchronous Serial Port (SSP Module) {clock signal is required} - Serial Peripheral Interface (SPI) - Inter Integrated Circuit (IIC -> I2C) Serial Interface Asynchronous Communication Modules (clock signal is not required) - Universal Asynchronous Receiver Transmitter (UART) UART • A Universal Asynchronous Receiver-Transmitter (UART) is used for serial communications – usually via a cable. • The UART generates signals with the same timing as the RS-232 standard used by the Personal Computer’s COM ports. • The UART input/output uses 0V for logic 0 and 5V for logic 1. • The RS-232 standard (and the COM port) use +12V for logic 0 and –12V for logic 1. • To convert between these voltages levels we need an additional integrated circuit (such as Maxim’s MAX232). Parts of an RS-232 Frame • A frame transmits a single character and is in general composed of: 1) A start bit (always logic 0) 2) Data bits (5, 6, 7, or 8 of them) 3) A parity bit (optional, even or odd parity) 4) A stop bit (always logic 1) RS232 Level Converter PIC & MAX232 Connection UART Timing Accuracy • Since the transmitter and receiver keep track of time independently between clock recovery synchronization points, the combined inaccuracy of the transmitter and receiver’s clocks can not be too large. • For RS-232 communication, this combined inaccuracy is about 5%. • Usually, an RC oscillator is too inaccurate and a crystal is required. UART Bit Time and Baud Rate • The bit time (units of time) is the time from the start of one serial data bit value to the start of another. -

What the Heck Is RS-232 Anyway…

Tech Note What the heck is RS-232 anyway… It just occurred to me that there is an entire generation of technicians in the work force that did not grow up in the days of the TRS-80 and Commodore 64 PC. Rather, they were brought up on broadband and Wi-Fi. To them that funny looking 9-Pin connector that we old folks cut our teeth on is a mystery full of uncertainty and doubt – with a little bit of fear mixed in for good measure. In this paper, I hope to dispel some of the mystery and give you the essentials of RS-232. What is it? At one time, RS-232 / EIA-232 was the most widely used communication standard on the planet. It was defined and redefined many times. The “EIA” stands for “Electronic Industries Association” and the “RS” stands for “Recommended Standard.” That being the case, it was always rather loose. The physical characteristics of the hardware include both a 25 pin and 9 pin D sub connector. RS- 232 is capable of operating at data rates up to 20 Kbps and can push data about 50 ft. The absolute maximum data rate is difficult to nail down due the differences in the transmission line and cable length. It is possible to operate at some pretty high data rates if the distance is short. The voltage levels are defined as a range from -12 to +12 volts. RS-232 is also single ended. This means that a single electrical signal is compared to a common signal (ground) to determine binary logic states. -

Quadrature Amplitude Modulation (QAM) Or Amplitude Phase Shift Keying (APSK) S(T ) = a Sin(2Π F T + )

ΕΠΛ 427: ΚΙΝΗΤΑ ΔΙΚΤΥΑ ΥΠΟΛΟΓΙΣΤΩΝ (MOBILE NETWORKS) Δρ. Χριστόφορος Χριστοφόρου Πανεπιστήμιο Κύπρου - Τμήμα Πληροφορικής Modulation Techniques (Τεχνικές Διαμόρφωσης) Recall (Process and Elements of Radio Transmission) 1 Modulation Demodulation Topics Discussed 2 Digital Modulation Bit rate, Baud rate Basic Digital Modulation Techniques (ASK, FSK, PSK, QAM) Constellation diagrams Factors that influence the choice of Digital Modulation Scheme – Power Efficiency, Bandwidth Efficiency Modulation 3 Message Signal (Data to be transmitted) Carrier signal with frequency fc Controlling the Amplitude of the carrier signal (ASK) Controlling the Frequency of the carrier signal (FSK) Controlling the Phase of the Modulated Signals Modulated carrier signal (PSK) Analog and Digital Signals Αναλογικά και Ψηφιακά Σήματα 4 Means by which data are propagated over a medium (Οι τρόποι με τους οποίους τα δεδομένα διαδίδονται μέσω κάποιου μέσου). An Analog Signal is a continuously varying electromagnetic wave (ένα συνεχόμενο εναλλασσόμενο ηλεκτρομαγνητικό κύμα) that may be propagated over a variety of media: Wire, fiber optic, coaxial, space (wireless) A digital signal is a sequence of discrete voltage pulses (είναι μια αλληλουχία διακριτών παλμών τάσης) that can be transmitted over a wire medium: E.g., a constant positive level of voltage to represent bit 1 and a constant negative level to represent bit 0. Modulation for Wireless Digital Modulation 5 Digital modulation is the process by which an analog carrier wave is modulated to include a discrete (digital) signal. (Ψηφιακή διαμόρφωση είναι η διαδικασία κατά την οποία ένας μεταφορέας αναλογικού σήματος διαμορφώνεται έτσι ώστε να συμπεριλάβει ένα διακριτό (ψηφιακό) σήμα (π.χ., 1 or 0)) Digital modulation methods can be considered as Digital-to- Analog conversion, and the corresponding Demodulation (e.g., at the Receiver) as Analog-to-Digital conversion. -

Design and Its Application of Microprocessor

Design and Its application of Microprocessor The 8088 And 8086 Microprocessors: Programming, Interfacing, Software, Hardware And Applications Suk-Ju Kang Dong-A University [email protected] 1 Chapter 9. Memory Devices, Circuits, and Subsystem Design 2 In This Chapter, … 9.1 Program and Data Storage 9.2 Read-Only Memory 9.3 Random Access Read/Write Memories 9.4 Parity, the Parity Bit, and Parity- Checker/Generator Circuit 9.5 FLASH Memory 9.6 Wait-State Circuitry 9.7 8088/8086 Microcomputer System Memory Circuitry 3 Program and Data Storage The memory unit of a microcomputer is partitioned into a primary storage section and secondary storage section 4 Program and Data Storage The basic input/output system (BIOS) are programs held in ROM. ◦ They are called firmware because of their permanent nature ◦ The typical size of a BIOS ROM used in a PC today is 256 Kbytes Programs are normally read in from the secondary memory storage device, stored in the program storage part of memory, and then run 5 Read-Only Memory ROM, PROM, and EPROM ◦ Mask-programmable read-only memory (ROM) ◦ One-time-programmable read-only memory (PROM) ◦ Erasable read-only memory (EPROM) 6 Read-Only Memory Block diagram of a read-only memory Address bus ◦ Data bus ◦ Control bus Chip enable (CE) Output enable (OE) 7 Read-Only Memory Read operation 8 Random Access Read/Write Memories The memory section of a microcomputer system is normally formed from both read-only memories and random access read/write memories (RAM) RAM is different from ROM in two ways: ◦ Data stored in RAM is not permanent in nature RAM is normally used to store temporary data and application programs for execution ◦ RAM is volatile If power is removed from RAM, the stored data are lost 9 Random Access Read/Write Memories Static and dynamic RAMs ◦ For a static RAM (SRAM), data remain valid as long as the power supply is not turned off.