18545 Final Report Fall 2013 Team Onemorething Project: Super Nintendo Entertainment System Team Members

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

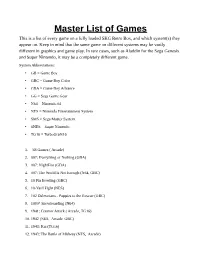

Master List of Games This Is a List of Every Game on a Fully Loaded SKG Retro Box, and Which System(S) They Appear On

Master List of Games This is a list of every game on a fully loaded SKG Retro Box, and which system(s) they appear on. Keep in mind that the same game on different systems may be vastly different in graphics and game play. In rare cases, such as Aladdin for the Sega Genesis and Super Nintendo, it may be a completely different game. System Abbreviations: • GB = Game Boy • GBC = Game Boy Color • GBA = Game Boy Advance • GG = Sega Game Gear • N64 = Nintendo 64 • NES = Nintendo Entertainment System • SMS = Sega Master System • SNES = Super Nintendo • TG16 = TurboGrafx16 1. '88 Games ( Arcade) 2. 007: Everything or Nothing (GBA) 3. 007: NightFire (GBA) 4. 007: The World Is Not Enough (N64, GBC) 5. 10 Pin Bowling (GBC) 6. 10-Yard Fight (NES) 7. 102 Dalmatians - Puppies to the Rescue (GBC) 8. 1080° Snowboarding (N64) 9. 1941: Counter Attack ( Arcade, TG16) 10. 1942 (NES, Arcade, GBC) 11. 1943: Kai (TG16) 12. 1943: The Battle of Midway (NES, Arcade) 13. 1944: The Loop Master ( Arcade) 14. 1999: Hore, Mitakotoka! Seikimatsu (NES) 15. 19XX: The War Against Destiny ( Arcade) 16. 2 on 2 Open Ice Challenge ( Arcade) 17. 2010: The Graphic Action Game (Colecovision) 18. 2020 Super Baseball ( Arcade, SNES) 19. 21-Emon (TG16) 20. 3 Choume no Tama: Tama and Friends: 3 Choume Obake Panic!! (GB) 21. 3 Count Bout ( Arcade) 22. 3 Ninjas Kick Back (SNES, Genesis, Sega CD) 23. 3-D Tic-Tac-Toe (Atari 2600) 24. 3-D Ultra Pinball: Thrillride (GBC) 25. 3-D WorldRunner (NES) 26. 3D Asteroids (Atari 7800) 27. -

Master List of Games This Is a List of Every Game on a Fully Loaded SKG Retro Box, and Which System(S) They Appear On

Master List of Games This is a list of every game on a fully loaded SKG Retro Box, and which system(s) they appear on. Keep in mind that the same game on different systems may be vastly different in graphics and game play. In rare cases, such as Aladdin for the Sega Genesis and Super Nintendo, it may be a completely different game. System Abbreviations: • GB = Game Boy • GBC = Game Boy Color • GBA = Game Boy Advance • GG = Sega Game Gear • N64 = Nintendo 64 • NES = Nintendo Entertainment System • SMS = Sega Master System • SNES = Super Nintendo • TG16 = TurboGrafx16 1. '88 Games (Arcade) 2. 007: Everything or Nothing (GBA) 3. 007: NightFire (GBA) 4. 007: The World Is Not Enough (N64, GBC) 5. 10 Pin Bowling (GBC) 6. 10-Yard Fight (NES) 7. 102 Dalmatians - Puppies to the Rescue (GBC) 8. 1080° Snowboarding (N64) 9. 1941: Counter Attack (TG16, Arcade) 10. 1942 (NES, Arcade, GBC) 11. 1942 (Revision B) (Arcade) 12. 1943 Kai: Midway Kaisen (Japan) (Arcade) 13. 1943: Kai (TG16) 14. 1943: The Battle of Midway (NES, Arcade) 15. 1944: The Loop Master (Arcade) 16. 1999: Hore, Mitakotoka! Seikimatsu (NES) 17. 19XX: The War Against Destiny (Arcade) 18. 2 on 2 Open Ice Challenge (Arcade) 19. 2010: The Graphic Action Game (Colecovision) 20. 2020 Super Baseball (SNES, Arcade) 21. 21-Emon (TG16) 22. 3 Choume no Tama: Tama and Friends: 3 Choume Obake Panic!! (GB) 23. 3 Count Bout (Arcade) 24. 3 Ninjas Kick Back (SNES, Genesis, Sega CD) 25. 3-D Tic-Tac-Toe (Atari 2600) 26. 3-D Ultra Pinball: Thrillride (GBC) 27. -

THE SUPER WILDCARD DX2 FAQ V1.3 by Vincent Charbonneau

THE SUPER WILDCARD DX2 FAQ V1.3 By Vincent Charbonneau (AKA Fat_Mike) Last Update: January 8th 2003 This FAQ was written for the purpose of helping Super WildCard DX2 owners to get the most out of their unit. It is also supposed to help those of you who are new to the backup unit world. If you have a problem that isn’t listed in this document, be sure to e-mail me. If I, or someone, manage to solve it, I will add it in the next update of the FAQ with the proper credits given. And this is about the Super WildCard DX2, so if you are using another SNES backup unit, the information given in this FAQ are darn useless to you. When I talk about the SWC DX2, I refer to the Super WildCard DX2 (in case you didn’t know). And English is not my native language, so there might be grammar errors and such (even though the FAQ was corrected). If you don’t understand something or want me to correct something, again be sure to e-mail me ([email protected])! For those who are totally new to the copier world and don’t know what the hell I’m talking about, a Super WildCard is a Super Nintendo backup unit. With a SWC DX2, you can copy your game cartridges and play these copies (ROMs) without the need of the actual cart. You can also play a downloaded ROM image directly on your SNES just like the real cartridge. And there’s far more the SWC DX2 can do, but I can’t list all the possibilities of this copier, it would take a while. -

Download 80 PLUS 4983 Horizontal Game List

4 player + 4983 Horizontal 10-Yard Fight (Japan) advmame 2P 10-Yard Fight (USA, Europe) nintendo 1941 - Counter Attack (Japan) supergrafx 1941: Counter Attack (World 900227) mame172 2P sim 1942 (Japan, USA) nintendo 1942 (set 1) advmame 2P alt 1943 Kai (Japan) pcengine 1943 Kai: Midway Kaisen (Japan) mame172 2P sim 1943: The Battle of Midway (Euro) mame172 2P sim 1943 - The Battle of Midway (USA) nintendo 1944: The Loop Master (USA 000620) mame172 2P sim 1945k III advmame 2P sim 19XX: The War Against Destiny (USA 951207) mame172 2P sim 2010 - The Graphic Action Game (USA, Europe) colecovision 2020 Super Baseball (set 1) fba 2P sim 2 On 2 Open Ice Challenge (rev 1.21) mame078 4P sim 36 Great Holes Starring Fred Couples (JU) (32X) [!] sega32x 3 Count Bout / Fire Suplex (NGM-043)(NGH-043) fba 2P sim 3D Crazy Coaster vectrex 3D Mine Storm vectrex 3D Narrow Escape vectrex 3-D WorldRunner (USA) nintendo 3 Ninjas Kick Back (U) [!] megadrive 3 Ninjas Kick Back (U) supernintendo 4-D Warriors advmame 2P alt 4 Fun in 1 advmame 2P alt 4 Player Bowling Alley advmame 4P alt 600 advmame 2P alt 64th. Street - A Detective Story (World) advmame 2P sim 688 Attack Sub (UE) [!] megadrive 720 Degrees (rev 4) advmame 2P alt 720 Degrees (USA) nintendo 7th Saga supernintendo 800 Fathoms mame172 2P alt '88 Games mame172 4P alt / 2P sim 8 Eyes (USA) nintendo '99: The Last War advmame 2P alt AAAHH!!! Real Monsters (E) [!] supernintendo AAAHH!!! Real Monsters (UE) [!] megadrive Abadox - The Deadly Inner War (USA) nintendo A.B. -

Reversing the Nintendo 64

Mike Ryan, John McMaster, marshallh REcon 2015-06-21 Introduction History Source: http://vincenzoferme.github.io/informatics_history_HCI_atelier_2015/ html/games/videogame_crash.html “Atari collapsed because they gave too much freedom to third-party developers and the market was swamped with rubbish games.” Hiroshi Yamauchi President of Nintendo, 1986 Birth of the CIC AKA the 10NES SNES Bypassing the NES CIC Sneaky Sneaky Atari • Atari Games Corp. v. Nintendo of America Inc. • “This ‘reverse engineering’ process, to the extent untainted by the 10NES copy purloined from the Copyright Office, qualified as a fair use.” N64 Block Diagram Game ROM CIC Cartridge CPU RCP PIF Mainboard Rambus RAM Modern CIC Clones Source: neviktsi M-m-m-m-multi CIC • 6 variants / region • 2 regions Credit: brizzo Getting @ silicon Resulting tangle Removing bond wires • Pluck with tweezers • Solder amalgam → Delayer • Remove SiO2 + metal • HF uneven, AlF3 residue • Solution: vortex, buffer w/ NH4F (BOE) ROM silicon • An active programmed ROM is easy to see: • CIC ROM: where's the data? Dash etch → Dash: theory • Doping influences competing reactions – HNO3: convert Si to SiO2 – HF: dissolve SiO2 • Form thin SiO2 => optical interference Copyright © Andrew Zonenberg Dash: practice • Etch 10-15 seconds w/ light recommended • Many fine points for good etch • Over etching destroys data Dash: process variation • Different oxide thickness, etc • Need to practice a few times • Old sports games: $0.50/cart → Dash: cleanliness, chemical purity • Small residues can block -

NES Specifications

Everynes - Nocash NES Specs Everynes Hardware Specifications Tech Data Memory Maps I/O Map Picture Processing Unit (PPU) Audio Processing Unit (APU) Controllers Cartridges and Mappers Famicom Disk System (FDS) Hardware Pin-Outs CPU 65XX Microprocessor About Everynes Tech Data Overall Specs CPU 2A03 - customized 6502 CPU - audio - does not contain support for decimal The NTSC NES runs at 1.7897725MHz, and 1.7734474MHz for PAL. NMIs may be generated by PPU each VBlank. IRQs may be generated by APU and by external hardware. Internal Memory: 2K WRAM, 2K VRAM, 256 Bytes SPR-RAM, and Palette/Registers The cartridge connector also passes audio in and out of the cartridge, to allow for external sound chips to be mixed in with the Famicom audio. Original Famicom (Family Computer) (1983) (Japan) 60-pin cartridge slot, with external sound-input, without lockout chip. Two joypads directly attached to console, Joypad 1 with Start/Select buttons, Joypad 2 with microphone, but without Start/Select. 15pin Expansion port for further controllers. Video RF-Output only. "During its first year, people found the Famicom to be unreliable, with programming errors and freezing rampant. Yamauchi recalled all sold Famicom systems, and put the Famicom out of production until the errors were fixed. The Famicom was re-released with a new motherboard." Original NES (Nintendo Entertainment System) (1985) (US, Europe, Australia) Same as Famicom, but with slightly different pin-outs on cartridge slot, and controllers/expansion ports: Front-loading 72-pin cartridge slot, without external sound-input on cartridge slot, without microphone on joypads, with lockout chip. Newer Famicom, AV Famicom (1993-1995) 60-pin cartridge slot, with external sound-input, without lockout chip. -

Nintendo Power Magazine!

y f Vi //i /*I jzJmuJJi 1 E VVIHI# Join the club! Just sign-up fora full year ofclub benefits forSI5, and get 12 issues of Nintendo Power Magazine! Way more than a subscription! we Ve taken all the best parts of Nintendo Power Magazine, and Super-charged them to give you more playing power than ever before! Just look at everything you'll get! Nintendo Power Subscription-Membership includes your monthly Nintendo Power magazine. Every month you'll get tips, strategies, full-color maps and reviews for all 3 Nintendo systems, straight from the pros at Nintendo. Power Certificates -A full year gets you $36 in exclusive Power Certificates to help you get the hottest game paks at reduced prices. Power Trading Cards-Every month you 'll get six Power Trading Cards-they feature stats and challenges for your favorite games. You can even win a FREEgame pak! Super Power Issue-Coming every January, this members- only issue is a year-end look at Nintendo s best and it's packed with exclusive stuff that won 't be available in stores. Power Cleaning Service-Get the most power out of your Nintendo system with a free cleaning at your participating official Nintendo World Class Sen/ice® Center. Join NOW and choose your FREE Player's Guide! Get the Player 's Guide of your choice with your paid membership-a $15 value! NES Game Atlas (code 1003}-featuring complete maps for 18 best-selling classic games! 180 pages of must-have info for the senous player! Mario Mania (code 1004)~including over 100 pages about his new 16-bit adventure, Super Mario World. -

United States Patent (19) 11 Patent Number: 6,071,191 Takeda Et Al

USOO6071191A United States Patent (19) 11 Patent Number: 6,071,191 Takeda et al. (45) Date of Patent: Jun. 6, 2000 54 SYSTEMS AND METHODS FOR PROVIDING OTHER PUBLICATIONS SECURITY IN A WIDEO GAME SYSTEM Open Programming Guide, “The Official Guide to Learning 75 Inventors: Genyo Takeda, Kyoto; Shuhei Kato, OpenGL, Release 1. OpenGL Architecture Review Board, Otsu; Satoshi Nishiumi, Kyoto, all of Jackie Neider, Tom Davis, Mason Woo, Copyright 1993 by Japan Silicon Graphics, Inc. Open GL Reference Manual, “The Official Reference Docu 73 Assignee: Nintendo Co., Ltd., Kyoto, Japan ment for OpenGL, Release 1,” OpenGL Architecture Review Board, Copyright 1992 by Silicon Graphics, Inc. 21 Appl. No.: 08/850,676 MIPS Microprocessor R4000 User's Manual, First Edition, by Joe Heinrich, Copyright 1993 by MIPS Technologies, 22 Filed: May 2, 1997 Inc. Related U.S. Application Data (List continued on next page.) 63 Continuation-in-part of application No. 08/562,288, Nov. Primary Examiner Valencia Martin-Wallace 22, 1995. Attorney, Agent, or Firm Nixon & Vanderhye P.C. (51) Int. Cl. .................................................. G06F 1700 57 ABSTRACT 52 U.S. Cl. .................................. 463/29: 463/36; 463/43 58 Field of Search .................................. 463,29, 36,43, A video game System includes a game cartridge which is 463/44, 45, 46, 47 pluggably attached to a main console having a main processor, a 3D graphics generating coprocessor, expand 56) References Cited able main memory and player controllers. A multifunctional peripheral processing Subsystem external to the game micro U.S. PATENT DOCUMENTS processor and coprocessor is described which executes Re. 31,200 4/1983 Sukonick et al. -

WHETHER You're LOOKING to COMPLETE the FUL SET

COLLECTORS' CORNER! WHETHER You’re lOOKING TO COMPLETE THE FUL SET, COLLECT ALL THE GAMES PUBLISHED IN THE FOUR MAIN TERRITORIES, OR MORE MODESTLY LIST THE TITLES YOU OWN, THE COLLECTor’s CORNER WAS MADE FOR YOU. TITLE PAGE ALTERNATE TITLE RELEASE RELEASE RELEASE DEVELOPER PUBLISHER DATE JP DATE NTSC DATE PAL 2020 SUPER BASEBALL 10 MONOLITH K AMUSEMENT LEASING (JP) / TRADEWEST (US) 3 NINJAS KICK BACK 10 l l MALIBU INTERACTIVE SONY IMAGESOFT 3×3 EYES JÛMA HÔKAN 10 l SYSTEM SUPPLY N-TECH BANPRESTO 3×3 EYES SEIMA KÔRINDEN 10 l NOVA GAMES YUTAKA GREAT BATTLE III (THE) 114 l SUN L BANPRESTO 4-NIN SHÔGI 10 l PLANNING OFFICE WADA PLANNING OFFICE WADA 7TH SAGA (THE) 10 ELNARD (JP) l PRODUCE GAMEPLAN21 (JP) / ENIX AMERICA (US) 90 MINUTES: EUROPEAN PRIME GOAL 11 J.LEAGUE SOCCER PRIME GOAL 3 (JP) l l NAMCO NAMCO (JP) / OCEAN (EU) A.S.P AIR STRIKE PATROL 11 DESERT FIGHTER (EU) l l OPUS SETA (JP-US) / SYSTEM 3 (EU) AAAHH!!! REAL MONSTERS 12 l l l REALTIME ASSOCIATES VIACOM NEW MEDIA ABC MONDAY NIGHT FOOTBALL 11 l l KÛSÔ KAGAKU DATA EAST ACCELE BRID 11 l Gl ENKI TOMY ACE O NERAE! 11 l TELENET JAPAN TELENET JAPAN ACME ANIMATION FACTORY 12 l PROBE SOFTWARE SUNSOFT ACROBAT MISSION 12 l l MICRONICS TECHIKU ACTION PACHIO 12 l C-LAB COCONUTS JAPAN ACTRAISER 13 l QUINTET ENIX (JP-EU) / ENIX AMERICA (US) ACTRAISER 2 14 ACTRAISER 2: CHINMOKU E NO SEISEN (JP) l l l QUINTET ENIX (JP) / ENIX AMERICA (US) / UBISOFT (EU) ADDAMS FAMILY (THE) 14 l l l OCEAN MISAWA (JP) / OCEAN (EU-US) ADDAMS FAMILY (THE): PUGSley’S SCAVENGER HUNT 14 l l l OCEAN OCEAN ADDAMS FAMILY VALUES 14 l l OCEAN OCEAN ADVANCED DUNGEONS & DRAGONS: EYE OF THE BEHOLDER 15 l Cl APCOM CAPCOM ADVENTURES OF BATMAN & ROBIN (THE) 15 l l KONAMI KONAMI ADVENTURES OF DR. -

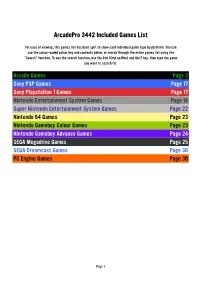

Arcadepro 3442 Included Games List

ArcadePro 3442 Included Games List For ease of viewing, this games list has been split to show each individual game type by platform. You can use the colour-coded colour key and contents below, or search through the entire games list using the "Search" function. To use the search function, use the Ctrl (Cmd on Mac) and the F key, then type the game you want to search for. Arcade Games Page 2 Sony PSP Games Page 17 Sony Playstation 1 Games Page 17 Nintendo Entertainment System Games Page 18 Super Nintendo Entertainment System Games Page 22 Nintendo 64 Games Page 23 Nintendo Gameboy Colour Games Page 23 Nintendo Gameboy Advance Games Page 24 SEGA Megadrive Games Page 25 SEGA Dreamcast Games Page 30 PC Engine Games Page 30 Page 1 Arcade Games Run and Gun (ver EAA 1993 10.8) Kid Niki - Radical Ninja Blomby Car Goal! '92 Kid no HoHo Daisakusen Chequered Flag Oriental Legend V101 Korean Edition--4P King Of The Monsters City Bomber Oriental Legend V103 Special Edition--4P King Of The Monsters 2 Demolition Derby Oriental Legend V105 Korean Edition--4P Kitten Kaboodle Drift Out Oriental Legend V111 China Edition--4P Kizuna Encounter Driving Force Oriental Legend V126--4P Knock Out!! F-1 Grand Prix Oriental Legend V205 Special Plus--4P Knuckle Bash Mille Miglia Bootleg Sanguo Zhan Ji 2 Guang Sao Yu Jun--4P Kong Hang-On Oriental Legend 2 Koro Koro Quest Hang-On Jr. The King of Fighters '97 Practice Korosuke Roller Ironman Ivan Stewart's Super Off-Road The King of Fighters '98 Practice Kung-Fu Master Konami GT The King of Fighters '98 Combo Practice -

The Wonderful World of Arcade Simulators

WWW.OLDSCHOOLGAMERMAGAZINE.COM ISSUE #9 • MARCH 2019 FULL PAGE AD MARCH 2019 • ISSUE #9 SIMULATIONS PEOPLE AND PLACES The Sims Game Swappers of SoCal! 06 BY TODD FRIEDMAN 41 BY AARON BURGER SIMULATIONS PEOPLE AND PLACES Turn and Burn Frank Schwartraubner 08 BY PATRICK HICKEY JR. 42 BY MARC BURGER SIMULATIONS NEWS Fox’s Game: Lucasfilm, Mirage... Video Games Debut at Heritage Auctions 10 BY SHAUN JEX 43 BY BRETT WEISS SIMULATIONS REVIEWS Driver and Driver 2 New Books on Old School Gaming Topics 12 BY CONOR MCBRIEN 44 BY RYAN BURGER AND RIC PRYOR MICHAEL THOMASSON’S JUST 4 QIX COLLECTOR INFO Behind Enemy Lines Super Nintendo Pricer 14 BY MICHAEL THOMASSON 45 PRESENTED BY PRICECHARTING.COM BRETT’S OLD SCHOOL BARGAIN BIN NEWS Asteroids and Beamrider Great Retro Shops 16 BY BRETT WEISS 50 BY OLD SCHOOL GAMER REVIEWS Flip Grip: Bullet Heaven 20 BY ROB FARALDI REVIEWS Old Atari on Switch... 22 BY RYAN BURGER AND RIC PRYOR FEATURE Entering the Digitized Era - Part 1 24 BY WARREN DAVIS FEATURE Intruder Alert...Intruder Alert! 26 BY KEVIN BUTLER PRATT AT THE ARCADE Publisher Design Assistant Con Staff Leader Ryan Burger Marc Burger Paige Burger The Wonderful World of Arcade Simulators Editorial Board BY ADAM PRATT Editor Art Director 32 Brian Szarek Thor Thorvaldson Dan Loosen Doc Mack PEOPLE AND PLACES Business Manager Editorial Consultant Billy Mitchell Aaron Burger Dan Walsh Dan Kitchen: 2600 to Modern and Back Walter Day 35 BY OLD SCHOOL GAMER PEOPLE AND PLACES HOW TO REACH Postmaster – Send address changes to: OSG • 222 SE Main St • Grimes IA 50111 OLD SCHOOL GAMER: Dr. -

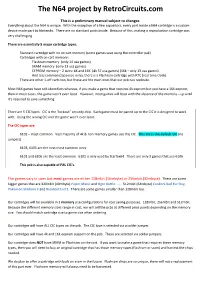

The N64 Project by Retrocircuits.Com

The N64 project by RetroCircuits.com This is a preliminary manual subject to changes. Everything about the N64 is unique. With the exception of a few capacitors, every part inside a N64 cartridge is a custom device made part by Nintendo. There are no standard parts inside. Because of this, making a reproduction cartridge was very challenging. There are essentially 5 major cartridge types: Standard cartridge with no on cart memory (some games save using the controller pak) Cartridges with on cart memory: Flashram memory (only 14 usa games) SRAM memory (only 13 usa games) EEPROM memory – 2 sizes: 4K and 16K (4k 57 usa games) (16k – only 13 usa games) And less common (Japanese only), there is a Flashram cartridge with RTC (real time clock). There are other 1-off carts too, but these are the main ones that our pcb can replicate. Most N64 games have self-identifiers whereas, if you make a game that requires 4k eeprom but you have a 16k eeprom, then in most cases, the game won’t even boot. However, most games will boot with the absence of the memory – up until it’s required to save something. There are 5 CIC types. CIC is the “lockout” security chip. Each game must be paired up to the CIC it is designed to work with. Using the wrong CIC and the game won’t even boot. The CIC types are: 6102 – most common. Vast majority of 4k & non-memory games use this CIC. This CIC is the default CIC (no jumpers) 6103, 6105 are the next most common ones.