Generating Video Sync Signals • Decoding NTSC Video

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Avid Supported Video File Formats

Avid Supported Video File Formats 04.07.2021 Page 1 Avid Supported Video File Formats 4/7/2021 Table of Contents Common Industry Formats ............................................................................................................................................................................................................................................................................................................................................................................................... 4 Application & Device-Generated Formats .................................................................................................................................................................................................................................................................................................................................................................. 8 Stereoscopic 3D Video Formats ...................................................................................................................................................................................................................................................................................................................................................................................... 11 Quick Lookup of Common File Formats ARRI..............................................................................................................................................................................................................................................................................................................................................................4 -

Video Codec Requirements and Evaluation Methodology

Video Codec Requirements 47pt 30pt and Evaluation Methodology Color::white : LT Medium Font to be used by customers and : Arial www.huawei.com draft-filippov-netvc-requirements-01 Alexey Filippov, Huawei Technologies 35pt Contents Font to be used by customers and partners : • An overview of applications • Requirements 18pt • Evaluation methodology Font to be used by customers • Conclusions and partners : Slide 2 Page 2 35pt Applications Font to be used by customers and partners : • Internet Protocol Television (IPTV) • Video conferencing 18pt • Video sharing Font to be used by customers • Screencasting and partners : • Game streaming • Video monitoring / surveillance Slide 3 35pt Internet Protocol Television (IPTV) Font to be used by customers and partners : • Basic requirements: . Random access to pictures 18pt Random Access Period (RAP) should be kept small enough (approximately, 1-15 seconds); Font to be used by customers . Temporal (frame-rate) scalability; and partners : . Error robustness • Optional requirements: . resolution and quality (SNR) scalability Slide 4 35pt Internet Protocol Television (IPTV) Font to be used by customers and partners : Resolution Frame-rate, fps Picture access mode 2160p (4K),3840x2160 60 RA 18pt 1080p, 1920x1080 24, 50, 60 RA 1080i, 1920x1080 30 (60 fields per second) RA Font to be used by customers and partners : 720p, 1280x720 50, 60 RA 576p (EDTV), 720x576 25, 50 RA 576i (SDTV), 720x576 25, 30 RA 480p (EDTV), 720x480 50, 60 RA 480i (SDTV), 720x480 25, 30 RA Slide 5 35pt Video conferencing Font to be used by customers and partners : • Basic requirements: . Delay should be kept as low as possible 18pt The preferable and maximum delay values should be less than 100 ms and 350 ms, respectively Font to be used by customers . -

Lecture 11 : Discrete Cosine Transform Moving Into the Frequency Domain

Lecture 11 : Discrete Cosine Transform Moving into the Frequency Domain Frequency domains can be obtained through the transformation from one (time or spatial) domain to the other (frequency) via Fourier Transform (FT) (see Lecture 3) — MPEG Audio. Discrete Cosine Transform (DCT) (new ) — Heart of JPEG and MPEG Video, MPEG Audio. Note : We mention some image (and video) examples in this section with DCT (in particular) but also the FT is commonly applied to filter multimedia data. External Link: MIT OCW 8.03 Lecture 11 Fourier Analysis Video Recap: Fourier Transform The tool which converts a spatial (real space) description of audio/image data into one in terms of its frequency components is called the Fourier transform. The new version is usually referred to as the Fourier space description of the data. We then essentially process the data: E.g . for filtering basically this means attenuating or setting certain frequencies to zero We then need to convert data back to real audio/imagery to use in our applications. The corresponding inverse transformation which turns a Fourier space description back into a real space one is called the inverse Fourier transform. What do Frequencies Mean in an Image? Large values at high frequency components mean the data is changing rapidly on a short distance scale. E.g .: a page of small font text, brick wall, vegetation. Large low frequency components then the large scale features of the picture are more important. E.g . a single fairly simple object which occupies most of the image. The Road to Compression How do we achieve compression? Low pass filter — ignore high frequency noise components Only store lower frequency components High pass filter — spot gradual changes If changes are too low/slow — eye does not respond so ignore? Low Pass Image Compression Example MATLAB demo, dctdemo.m, (uses DCT) to Load an image Low pass filter in frequency (DCT) space Tune compression via a single slider value n to select coefficients Inverse DCT, subtract input and filtered image to see compression artefacts. -

(A/V Codecs) REDCODE RAW (.R3D) ARRIRAW

What is a Codec? Codec is a portmanteau of either "Compressor-Decompressor" or "Coder-Decoder," which describes a device or program capable of performing transformations on a data stream or signal. Codecs encode a stream or signal for transmission, storage or encryption and decode it for viewing or editing. Codecs are often used in videoconferencing and streaming media solutions. A video codec converts analog video signals from a video camera into digital signals for transmission. It then converts the digital signals back to analog for display. An audio codec converts analog audio signals from a microphone into digital signals for transmission. It then converts the digital signals back to analog for playing. The raw encoded form of audio and video data is often called essence, to distinguish it from the metadata information that together make up the information content of the stream and any "wrapper" data that is then added to aid access to or improve the robustness of the stream. Most codecs are lossy, in order to get a reasonably small file size. There are lossless codecs as well, but for most purposes the almost imperceptible increase in quality is not worth the considerable increase in data size. The main exception is if the data will undergo more processing in the future, in which case the repeated lossy encoding would damage the eventual quality too much. Many multimedia data streams need to contain both audio and video data, and often some form of metadata that permits synchronization of the audio and video. Each of these three streams may be handled by different programs, processes, or hardware; but for the multimedia data stream to be useful in stored or transmitted form, they must be encapsulated together in a container format. -

VIDEO Blu-Ray™ Disc Player BP330

VIDEO Blu-ray™ Disc Player BP330 Internet access lets you stream instant content from Make the most of your HDTV. Blu-ray disc playback Less clutter. More possibilities. Cut loose from Netflix, CinemaNow, Vudu and YouTube direct to delivers exceptional Full HD 1080p video messy wires. Integrated Wi-Fi® connectivity allows your TV — no computer required. performance, along with Bonus-view for a picture-in- you take advantage of Internet access from any picture. available Wi-Fi® connection in its range. VIDEO Blu-ray™ Disc Player BP330 PROFILE & PLAYABLE DISC PLAYABLE AUDIO FORMATS BD Profile 2.0 LPCM Yes USB Playback Yes Dolby® Digital Yes External HDD Playback Yes (via USB) Dolby® Digital Plus Yes BD-ROM/BD-R/BD-RE Yes Dolby® TrueHD Yes DVD-ROM/DVD±R/DVD±RW Yes DTS Yes Audio CD/CD-R/CD-RW Yes DTS-HD Master Audio Yes DTS-CD Yes MPEG 1/2 L2 Yes MP3 Yes LG SMART TV WMA Yes Premium Content Yes AAC Yes Netflix® Yes FLAC Yes YouTube® Yes Amazon® Yes PLAYABLE PHOTO FORMATS Hulu Plus® Yes JPEG Yes Vudu® Yes GIF/Animated GIF Yes CinemaNow® Yes PNG Yes Pandora® Yes MPO Yes Picasa® Yes AccuWeather® Yes CONVENIENCE SIMPLINK™ Yes VIDEO FEATURES Loading Time >10 Sec 1080p Up-scaling Yes LG Remote App Yes (Free download on Google Play and Apple App Store) Noise Reduction Yes Last Scene Memory Yes Deep Color Yes Screen Saver Yes NvYCC Yes Auto Power Off Yes Video Enhancement Yes Parental Lock Yes Yes Yes CONNECTIVITY Wired LAN Yes AUDIO FEATURES Wi-Fi® Built-in Yes Dolby Digital® Down Mix Yes DLNA Certified® Yes Re-Encoder Yes (DTS only) LPCM Conversion -

FMS6404 — Precision Composite Video Output with Sound Trap And

FMS6404 — Precision Composite October 2011 FMS6404 Precision Composite Video Output with Sound Trap and Group Delay Compensation Features Description The FMS6404 is a single composite video 5th-order Video Output with Sound Trap 7.6MHz 5th-Order Composite Video Filter . Butterworth low-pass video filter optimized for minimum . 14dB Notch at 4.425MHz to 4.6MHz for Sound Trap overshoot and flat group delay. The device contains an Capable of Handling Stereo audio trap that removes video information in a spectral location of the subsequent RF audio carrier. The group 50dB Stopband Attenuation at 27MHz on . delay compensation circuit pre-distorts the signal to CV Output compensate for the inherent receiver intermediate . > 0.5dB Flatness to 4.2MHz on CV Output frequency (IF) filter’s group delay distortion. Equalizer and Notch Filter for Driving RF Modulator In a typical application, the composite video from the with Group Delay of -180ns DAC is AC coupled into the filter. The CV input has DC- restore circuitry to clamp the DC input levels during No External Frequency Selection Components . video synchronization. The clamp pulse is derived from or Clocks the CV channel. < 5ns Group Delay on CV Output All outputs are capable of driving 2VPP, AC- or DC- . AC-Coupled Input coupled, into either a single or dual video load. A single video load consists of a series 75Ω impedance . AC- or DC-Coupled Output matching resistor connected to a terminated 75Ω line. and Group Delay Compensation . Capable of PAL Frequency for CV This presents a total of 150Ω of loading to the part. -

A Look at SÉCAM III

Viewer License Agreement You Must Read This License Agreement Before Proceeding. This Scroll Wrap License is the Equivalent of a Shrink Wrap ⇒ Click License, A Non-Disclosure Agreement that Creates a “Cone of Silence”. By viewing this Document you Permanently Release All Rights that would allow you to restrict the Royalty Free Use by anyone implementing in Hardware, Software and/or other Methods in whole or in part what is Defined and Originates here in this Document. This Agreement particularly Enjoins the viewer from: Filing any Patents (À La Submarine?) on said Technology & Claims and/or the use of any Restrictive Instrument that prevents anyone from using said Technology & Claims Royalty Free and without any Restrictions. This also applies to registering any Trademarks including but not limited to those being marked with “™” that Originate within this Document. Trademarks and Intellectual Property that Originate here belong to the Author of this Document unless otherwise noted. Transferring said Technology and/or Claims defined here without this Agreement to another Entity for the purpose of but not limited to allowing that Entity to circumvent this Agreement is Forbidden and will NOT release the Entity or the Transfer-er from Liability. Failure to Comply with this Agreement is NOT an Option if access to this content is desired. This Document contains Technology & Claims that are a Trade Secret: Proprietary & Confidential and cannot be transferred to another Entity without that Entity agreeing to this “Non-Disclosure Cone of Silence” V.L.A. Wrapper. Combining Other Technology with said Technology and/or Claims by the Viewer is an acknowledgment that [s]he is automatically placing Other Technology under the Licenses listed below making this License Self-Enforcing under an agreement of Confidentiality protected by this Wrapper. -

Multimedia Systems Part 12

Multimedia Systems Part 12 Mahdi Vasighi www.iasbs.ac.ir/~vasighi Department of Computer Science and Information Technology, Institute for Advanced Studies in Basic Sciences, Zanjan, Iran To discuss: • Types of video signals • Analog Video • Digital Video Types of Video Signals Video Signals can be classified as 1. Composite Video 2. S-Video 3. Component Video Types - Composite Video • Used in broadcast TV’s • Compatible with B/W TV • Chrominance ( I & Q or U & V) & Luminance (Y) signals are mixed into a single carrier wave, which can be separated at the receiver • Mixing of signals leads interference & create crosstalk and visual defects (dot crawl) Types – S-Video o S stands Super / Separated o Uses 2 wires, one for luminance & the other for chrominance signals o Less cross talk Pin 1 Ground (Y) Pin 2 Ground (C) Pin 3 Intensity (Luminance) Pin 4 Color (Chrominance) o Humans have much higher acuity for luminescence part of images than for the color part of color images. o we can send less accurate color information than must be sent for intensity information Types – Component Video o Each primary is sent as a separate video signal. The primaries can either be RGB or a luminance- chrominance transformation of them (e.g., YIQ, YUV). Best color reproduction . Requires more bandwidth and good synchronization of the three components Types – Component Video SONY Bravia KDL-46XBR4 Analog Video o Represented as a continuous (time varying) signal o Brightness is a monotonic function of the voltage o Sweeping an electrical signal horizontally across the display one line at a time. -

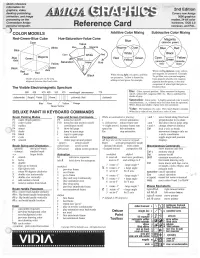

Amiga Graphics Reference Card 2Nd Edition

Quick reference information for graphics, video, 2nd Edition desktop publishing, Covers new Amiga animation, and image 3000 graphics processing on the modes, 24-bit color Commodore Amiga hardware, DOS 2.0 personal computer. Reference Card overscan, and PAL. ) COLOR MODELS Additive Color Mixing Subtractive Color Mixing Red-Green-Blue Cube Hue-Saturation-Value Cone Cyan Value White Blue Blue] Axis Yellow Black ~reen Axis When mixi'hgpigments, cyan, yellow, Red When mixing light, red, green, and blue and magenta are primaries. Example: are primaries. Yell ow is formed by To get blue, mix cyan and magenta. Shades of gray are on the long Cyan pigment absorbs red, magenta adding red and green, for example. diagonal between black and white. pigment absorbs green, so the only component of white light that gets re The Visible Electromagnetic Spectrum flected is blue. 380 420 470 495 535 575 wavelength (nanometers) 770 Hue: Color; spectral position. Often measured in degrees; red=0°, yellow=60°, magenta=300°, etc. Hue is undefined for shades of gray. (ultraviolet) Purple Violet yellowish Red (infrared) Saturation: Color purity. A highly-saturated color is nearly Blue Orange monochromatic, i.e., contains only one color from the spectrum. White, black, and shades of gray have zero saturation. Value: The darkness of a color. How much black it contain's. DELUXE PAINT Ill KEYBOARD COMMANDS White has a value of one, black has a value of zero. Brush Painting Modes Page and Screen Commands While an animation is playing: ; ana, move brush along fixed axis -

Frequently Asked Questions Dolby Digital Plus

Frequently Asked Questions Dolby® Digital Plus redefines the home theater surround experience for new formats like high-definition video discs. What is Dolby Digital Plus? Dolby® Digital Plus is Dolby’s new-generation multichannel audio technology developed to enhance the premium experience of high-definition media. Built on industry-standard Dolby Digital technology, Dolby Digital Plus as implemented in Blu-ray Disc™ features more channels, less compression, and higher data rates for a warmer, richer, more compelling audio experience than you get from standard-definition DVDs. What other applications are there for Dolby Digital Plus? The advanced spectral coding efficiencies of Dolby Digital Plus enable content producers to deliver high-resolution multichannel soundtracks at lower bit rates than with Dolby Digital. This makes it ideal for emerging bandwidth-critical applications including cable, IPTV, IP streaming, and satellite (DBS) and terrestrial broadcast. Dolby Digital Plus is also a preferred medium for delivering BonusView (Profile 1.1) and BD-Live™ (Profile 2.0) interactive audio content on Blu-ray Disc. Delivering higher quality and more channels at higher bit rates, plus greater efficiency at lower bit rates, Dolby Digital Plus has the flexibility to fulfill the needs of new content delivery formats for years to come. Is Dolby Digital Plus content backward-compatible? Because Dolby Digital Plus is built on core Dolby Digital technologies, content that is encoded with Dolby Digital Plus is fully compatible with the millions of existing home theaters and playback systems worldwide equipped for Dolby Digital playback. Dolby Digital Plus soundtracks are easily converted to a 640 kbps Dolby Digital signal without decoding and reencoding, for output via S/PDIF. -

User Manual 8X4 Composite Video/S-Video and Analog

User Manual 8x4 Composite Video/S-Video and Analog Audio Matrix Switcher With IR & RS 232 Control / RS 232 Driver for Win98/2000/XP AT-SAV-84M Toll free: 1-877-536-3976 Local: 1-408-962-0515 www.atlona.com TABLE OF CONTENTS 1. Introduction .................................................. 2 2. Features .................................................. 2 3. Specifications .................................................. 3 4. Package Contents .................................................. 3 5. Panel Descriptions .................................................. 3 5.1 Front Panel .................................................. 3 5.2 Rear Panel .................................................. 3 6. IR Codes .................................................. 4 7. RS-232 Commands .................................................. 5 8. Installation .................................................. 6 9. Safety Information .................................................. 7 10. Warranty .................................................. 8 11. Atlona Product Registration .................................................. 9 Toll free: 1-877-536-3976 Local: 1-408-962-0515 1 www.atlona.com INTRODUCTION Atlona Technologies’ AT-SAV-84M is a 8x4 S-Video/Composite Video/Analog Audio Matrix Switcher de¬signed to work as a switcher for multiple Audio/Video sources and displays. This Atlona unit is capable of switching Composite Video, S-Video and Stereo Audio signals between eight sources and four displays. Because it is a matrix switch, -

IARU-R1 VHF Handbook

IARU-R1 VHF Handbook Vet Vers Version 9.01 March 2021 ion 8.12 IARU-R1 The content of this Handbook is the property of the International Amateur Radio Union, Region 1. Copying and publication of the content, or parts thereof, is allowed for non-commercial purposes provided the source of information is quoted. Contact information Website: http://www.iaru-r1.org/index.php/vhfuhsshf Newsletters: http://www.iaru- r1.org/index.php/documents/Documents/Newsletters/VHF-Newsletters/ Wiki http://iaruwiki.oevsv.at Contest robot http://iaru.oevsv.at/v_upld/prg_list.php VHF Handbook 9.00 1/180 IARU-R1 Oostende, 17 March 2021 Dear YL and OM, The Handbook consists of 5 PARTS who are covering all aspects of the VHF community: • PART 1: IARU-R1 VHF& up Organisation • PART 2: Bandplanning • PART 3: Contesting • PART 4: Technical and operational references • PART 5: archive This handbook is updated with the new VHF contest dates and rules and some typo’s in the rest of the handbook. Those changes are highlighted in yellow. The recommendations made during this Virtual General conference are highlighted in turquoise 73 de Jacques, ON4AVJ Secretary VHF+ committee (C5) IARU-R1 VHF Handbook 9.00 2/180 IARU-R1 CONTENT PART 1: IARU-1 VHF & UP ORGANISATION ORGANISATION 17 Constitution of the IARU Region 1 VHF/UHF/Microwaves Committee 17 In the Constitution: 17 In the Bye-laws: 17 Terms of reference of the IARU Region 1 VHF/UHF/Microwaves Committee 18 Tasks of IARU R-1 and its VHF/UHF/µWave Committee 19 Microwave managers Sub-committee 20 Coordinators of the VHF/UHF/Microwaves Committee 21 VHF Contest Coordinator 21 Satellite coordinator 21 Beacon coordinator 21 Propagations coordinators 21 Records coordinator 21 Repeater coordinator 21 IARU R-1 Executive Committee 21 Actual IARU-R1 VHF/UHF/SHF Chairman, Co-ordinators and co-workers 22 National VHF managers 23 Microwave managers 25 Note.