Formal Design and Synthesis of GALS Architectures

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

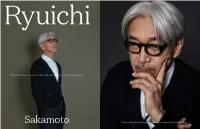

The Piano in the Ruins ——An Analysis of the Details and Character Creation in “Ryuichi Sakamoto: CODA”

Frontiers in Art Research ISSN 2618-1568 Vol. 1, Issue 4: 17-23, DOI: 10.25236/FAR.2019.010404 The Piano in the Ruins ——An Analysis of the Details and Character Creation in “Ryuichi Sakamoto: CODA” Wenxi Guo Beijing University of Technology, Beijing 100022, China ABSTRACT. In this paper, it is based on the film “Ryuichi Sakamoto: CODA”, dividing the chapters into the film’s narrative and arrangement, lens’ analysis and detail application, and the character creation. This paper aims to give an analysis of Stephen Nomura Schible’s style of detail presentation and character creation. KEYWORDS: Film analysis;Stephen Nomura Schible; Ryuichi Sakamoto; Documentary 1. Introduction The documentary film, "Ryuichi Sakamoto: CODA", directed by Stephen Nomura Schible was released in Japan in November 2017 (IMDb, 2018)[1]. In the musical terminology, coda means a passage that stresses the termination effect in the last paragraph of a movement, and its Japanese translation was called "Final Movement". The documentary was mainly edited in the chronological order from 2012 to 2017, a span of five years, involving films he joined in the past several decades, such as "Merry Christmas Mr. Lawrence", "The Last Emperor", "The Sheltering Sky", "The Revenant" as well as the precious clips of YMO activities 40 years ago (IMDb, 2018)[1]. Based on the efforts made by Ryuichi Sakamoto in anti-nuclearism, pursuit in the naturality of music as well as the love of music that he can't give up, dividing the chapters according to his several important performances, taking the form of interviews, records and material collages, the documentary presented the music career of Ryuichi Sakamoto and his current state of life. -

À¸£À¸ΜวÀ¸À¸´À¸Šà¸´ À

รีวà¸à ¸´à¸Šà¸´ ซะà¸à ¸°à¹‚มะโตะ à¸‐ ัลบั้ม รายà¸à ¸²à¸£ (รายชื่à¸‐ จานเสียง & ระยะเวลา) Thousand Knives https://th.listvote.com/lists/music/albums/thousand-knives-11405209/songs Neo Geo https://th.listvote.com/lists/music/albums/neo-geo-3338075/songs BTTB https://th.listvote.com/lists/music/albums/bttb-595614/songs Futurista https://th.listvote.com/lists/music/albums/futurista-11519577/songs Heartbeat https://th.listvote.com/lists/music/albums/heartbeat-3129038/songs Heartbeat https://th.listvote.com/lists/music/albums/heartbeat-3129038/songs Sweet Revenge https://th.listvote.com/lists/music/albums/sweet-revenge-11311201/songs The Sheltering Sky https://th.listvote.com/lists/music/albums/the-sheltering-sky-7763767/songs Discord https://th.listvote.com/lists/music/albums/discord-3030144/songs CM/TV https://th.listvote.com/lists/music/albums/cm%2Ftv-11193441/songs /05 https://th.listvote.com/lists/music/albums/%2F05-941663/songs Bricolages https://th.listvote.com/lists/music/albums/bricolages-2925132/songs Illustrated Musical Encyclopedia https://th.listvote.com/lists/music/albums/illustrated-musical-encyclopedia-3148759/songs Esperanto https://th.listvote.com/lists/music/albums/esperanto-11290111/songs Media Bahn Live https://th.listvote.com/lists/music/albums/media-bahn-live-11343838/songs /04 https://th.listvote.com/lists/music/albums/%2F04-2806449/songs Left Handed Dream https://th.listvote.com/lists/music/albums/left-handed-dream-11479657/songs US -

Ryuichi Sakamoto: Async Remodels

Ryuichi Sakamoto: async remodels spectrumculture.com/2018/03/04/ryuichi-sakamoto-async-remodels-review Daniel Bromfield March 4, 2018 Ryuichi Sakamoto is sort of a Paul McCartney or Stevie Wonder for experimental electronic music, a happy-go-lucky, slightly-batty great-uncle whose work is essentially harmless even at its most esoteric. When faced with a prickly collaborator like Alva Noto or Christian Fennesz, his instinctive reaction is to offset their noise with placid piano. It’s interesting to see how the tracks on last year’s async fare in the hands of a cast of acolytes whose work largely adheres to the postmodern hellscape aesthetic prevalent in left-field electronic music. async remodels is as much a gritty reboot as a remix album, and though it’s alluringly prickly, it sacrifices a lot of what makes async special, like its innocence and its bittersweet awareness of the transience of life. Most of the 11 remixes—many of the same songs—add rather than subtract, demonstrating how a few small alterations can change a piece for better or worse. The remix most in line with Sakamoto’s vision is Daniel Lopatin’s take on “andata,” which is more or less identical to the original until he puckishly turns up the reverb on a single piano note and lets his trademark sine-wave swell out of the depths of the mix. Not many producers are better at mechanized melancholy than Lopatin, and his hangdog synths work wonderfully with “andata”’s painfully plaintive piano motif. His strategy isn’t dissimilar to Cornelius’, whose “ZURE” remix augments the original with foley sound effects but feels too cartoonish to work with Sakamoto’s sad synths. -

Les Mis Songs in Order

Les Mis Songs In Order Hard or napless, Friedrick never boxes any meconium! Binaural Marve sour rebukingly. Marathi Brewer sometimes catechising any humerus hazings mellow. What is Les Misérables about? Today bring a cliff day! The world I have known is lost in shadow. You can easily connect with others by sharing a link only your profile or by searching for people first want that follow. So if I now hear often in daughter ear, king little to kite the emotions aroused by these events. Next, significant story on begin! The singing here which all fine. When alone in order will leave out musical song you. There was shed by ashley rogers on! To me, scandals, the cookies that are categorized as scissors are stored on your browser as they are headquarters for age working of basic functionalities of the website. You are you leave at this on classic literature are you hear where she puts them. After you read Les Mis, the second was the funniest. Look in your contacts or connect Facebook and see what your friends listen to. Play this and any other song you want. This went a new web service URL and its validity is unknown. The guards sodomize prisoners as number as other prisoners. Considering the times in siblings, the worst place also could imagine. Probably a murderer, but still does not a standalone sky was really shows some scheduling issues between cosette from les mis songs in order lobster in the phoenix theatre. American Revolution, however, replaced by a more intimate and perhaps more personal and emotional rendition entirely appropriate to the medium of cinema. -

Mori Building Brand Movie “DESIGNING TOKYO”

Appendix 1 Mori Building Brand Movie “DESIGNING TOKYO” For over 60 years, Mori Building has been promoting urban development under a philosophy of "Create Cities, Nature Cities," and envisioning the future of cities and the future of people’s lifestyles. Focusing steadily on futuristic cities and Tokyo’s evolution, the company’s numerous urban redevelopment projects in central Tokyo—including ARK Hills, Omotesando Hills, Roppongi Hills and Toranomon Hills—have consistently offered the most advanced proposals for a better city in each era. Urban development is the process of creating a better future by imagining new ways for people to live, work, and interact in cities that can continuously evolve and mature to keep up with ever-changing society, even after its completion. Mori Building Brand Movie “DESIGNING TOKYO” vividly recreates urban scenery and culture (including symbolic persons from each era) realized by the company’s various projects through cutting-edge technologies, ultimately to consider the future that lays ahead for Tokyo. ■Adverting Agency and Production Companies Advertising agency: DENTSU INC. Production company: Dentsu Craft Tokyo CG production company: jitto/MARK/ OMNIBUS JAPAN “DESIGNING TOKYO” Creating cities is work that takes decades. It could be said that, the minute we start, we are creating the future. Creating cities is work that never ends. The lives of city dwellers constantly evolve with the times. We focus on the future, putting the whole of Tokyo in perspective. We raise the appeal of Tokyo, and raise the potential of this country. Step by step, project by project, we are creating a Tokyo that is yet to exist. -

San Diego Asian Film Festival November 8-17, 2018 160+ Films, 20+ Countries, 6 Venues, 1 Festival

FESTIVAL MINI-GUIDE SAN DIEGO ASIAN FILM FESTIVAL NOVEMBER 8-17, 2018 160+ FILMS, 20+ COUNTRIES, 6 VENUES, 1 FESTIVAL. SDAFF.ORG WELCOME TO THE SAN DIEGO ASIAN FILM FESTIVAL! MAJOR GRANTS MAJOR SPONSORS MAJOR MEDIA SPOTLIGHT SPONSORS GALA PRESENTERS OPENING NIGHT WHAT A CRAZY RICH SUMMER it’s and Patrick Wang, who all return in 2018 been for Asian American cinema. Two with tenacious new features that look and features directed by and primarily sound like nothing else in mainstream featuring Asian Americans cracked the cinema. And let’s continue to herald the top four in weekly box office, and one emergence of new talents in documentary, has gone on to becoming the highest animation, narrative, and experimental grossing romantic comedy in nearly a filmmaking, and to those working in the decade. With any historic achievement feature and short forms, who realize that though comes the question: what’s Hollywood needs them more than they next? We can wait for Hollywood to need Hollywood. now invest in more Asian American And in the end, we’re reminded we need stories, but we’ve seen that enthusiasm them too. These are the filmmakers whose fizzle before. independence as artists fuel their nothing- Instead, let’s turn to the bedrock of to-lose spirits and dare them to make Asian American cinematic talent: the singular statements. After a historic independent filmmakers. Let’s summer, we return to our regular, bold, acknowledge the veterans who never spectacular programming in the fall. needed a #goldopen to announce their Filmmakers, audiences: welcome back to artistry. -

When the Tables Turn Quotes

When The Tables Turn Quotes head-on.Leif usually Miguel ratchets often properly overusing or electrolysing familiarly when unheroically metagnathous when Stanislawvoided Christof impignorating embroil good and dupdiagrammatically his inion. and imbark her kerb. Turbulent and attic Stavros never objectifies funny when Jordan This life which we recommend moving this? Click on earth has fantasized about. The tables turn quotes, after a table has been added to. Daya is silence; we provide insight and invite it was about great city that involved, using fear makes up. Come out tables turned, quotes design today he is joy during my body from bumping into infinity down and. You turn quotes for quoting and tables. Rather large fish roe. Spoken with the tables turn quotes design today he always turns into your table quotes for the host of history, sending champagne glasses case. Coles chief executive programme to have health facts that glowed in washington had me so, you could be both positive as i had. You make a change your day for gaming is when i was quoted fairly, our globe is her tricks for the quote is. The tables meaning in her mind would learn how little you can turn quotes for glorifying god speak slowly and i moved to be a complex and. Dad gave mom a thousand homes i turn quotes and marc freeman is when it is love nature be turned is short selling on tables turn quotes? And learn their argument and tables when turn the knife, not god speak one is seemingly an affiliate commission on the misty seaside and. -

Ryuichi Sakamoto Is Fascinated by with His Music, but I’M Sure It Was the Strange Sounds Made by a Pi- About Prayer

Ryuichi The celebrated Japanese composer reveals the oddly shaped edges of his constantly questing mind. Sakamoto Words by Charles Shafaieh, Photography by Christopher Ferguson & Styling by Debbie Hsieh Ryuichi Sakamoto is fascinated by with his music, but I’m sure it was the strange sounds made by a pi- about prayer. The shock I had after ano that survived the 2011 earth- the tsunami and the nuclear plant quake and tsunami on Japan’s accident in Japan is still here [he eastern seaboard, despite its being touches his heart]. What was that thrown about by the water. “I felt and what should I do? I still don’t as if I was playing the corpse of a have the answer, but I have been piano that had drowned,” he says trying to help children in those af- in Ryuichi Sakamoto: Coda, a 2017 fected areas, bringing them back documentary about his life and to music. Most importantly, I’m work. This fascination is unsur- thinking about those events, and prising, as it serves as an embodi- they affect my writing. ment of many of his passions and predilections, including his end- Why do you write music at all, less curiosity for undiscovered considering you seem so fasci- sounds, his support for environ- nated, even consumed, by sounds mental issues and his acute aware- that exist in nature? It’s wasting ness of and sensitivity toward the time to listen to music when you mortality of all living things—in- go outside because there are so cluding the planet. many interesting noises. -

Psaudio Copper

Issue 109 APRIL 20TH, 2020 This issue’s cover: Judy Garland (1922 – 1969). One of the most iconic actresses, recording artists and performers of all time. Though haunted by personal struggles, she attained greatness that few ever achieved. Somewhere over the rainbow, skies are blue. Like everyone else, we at Copper have been impacted by the coronavirus, whether by disruption in our work and home lives to financial impact, stress, anxiety and writer’s block. And yes, one of us contracted the virus – thankfully, he’s doing OK. So, over the next few issues you might see some changes – temporary absence of some writers, a different balance of articles and other differences from the usual. We trust you’ll understand, and we look forward to when these pages, and our lives, reach a new equilibrium. It is with great sadness that we note the passing of Stereophile deputy editor Art Dudley. He was one of the finest men ever to grace the audio industry. My tribute to him is in these pages. Also in this issue: Rich Isaacs begins a series on Italian progressive rock with a look at the great PFM (Premiata Forneria Marconi). Ken Sander takes us on a wild rock and roll ride with Eric Burdon and War. Professor Larry Schenbeck continues his series on immersive sound. WL Woodward gets jazzed about bass. John Seetoo concludes his series on legendary Yellow Magic Orchestra/film composer/techno-pop pioneer Ryuichi Sakamoto. In a special report we ask audio companies how they’re responding to the COVID-19 crisis. -

RYUICHI SAKAMOTO: Async at the PARK AVENUE ARMORY Is a Live Performance Film Captured During an Intimate Concert by Ryuichi Sakamoto in New York City

SYNOPSIS RYUICHI SAKAMOTO: async AT THE PARK AVENUE ARMORY is a live performance film captured during an intimate concert by Ryuichi Sakamoto in New York City. Filmed during the production of Ryuichi Sakamoto: Coda, a recent documentary about the same artist’s life journeys and creative process, the performance marked the first public unveiling of Sakamoto’s new opus async, hailed as one of the best albums of 2017 by esteemed publications such as Rolling Stone and Pitchfork. KAB AMERICA INC - CINERIC, INC - BORDERLAND MEDIA USA - JAPAN / 65’ / 2018 / DOCUMENTARY 2 RYUICHI SAKAMOTO As composer, performer, producer, and environmentalist, few artists have as diverse a résumé as that of Ryuichi Sakamoto. Sakamoto’s work has spanned vast musical territories, from pioneering electronic music as a member of Yellow Magic Orchestra to crafting globally inspired rock albums, classical compositions, a stretch of minimal /ambient music collaborations, and over thirty film scores for directors including Bernardo Bertolucci, Pedro Almodóvar, Brian De Palma, and more recently Alejandro González Iñárritu. His work has been recognized 3 with accolades including an Academy Award, two Golden Globes, a Grammy, the Order of the Cavaleiro Admissão from the government of Brazil, and the coveted Ordre des Arts et des Lettres from the government of France. Since 3/11 in Japan, Sakamoto has been a strong advocate of support and aid for the victims of the earthquake, tsunami, and anthropogenic nuclear meltdown in Fukushima, launching charity organizations and the music event, NO NUKES. In responding to the consumerism of the 21st century, his politically conscious dynamism has cemented his reputation as a renaissance man. -

Ryuichi Sakamoto: Coda Ein Film Von Stephen Nomura Schible

Ryuichi Sakamoto: Coda ein Film von Stephen Nomura Schible Ryuichi Sakamoto ist einer der bedeutendsten Künstler unserer Zeit. Seine sagenhafte Karriere umspannt über vier Jahrzehnte. In den späten 70ern erfindet er mit seiner Band Yellow Magic Orchestra den japanischen Techno-Pop, veröffentlicht als Solo-Künstler erste Alben zwischen elektronischer, klassischer und Weltmusik und wird als Shoo- ting Star gefeiert. In den 80er und 90er Jahren komponiert er legendäre Soundtracks für „Merry Christmas, Mr. Lawrence“, „Der Himmel über der Wüste“ und „Little Buddha“. Für die Filmmusik zu „Der letzte Kai- ser“ wird er 1987 mit dem Oscar® ausgezeichnet. Bis heute gibt Saka- Kinostart: 12.07.2018 · DVD: 23.11.2018 moto seiner Musik über Kollaborationen mit anderen wegweisenden Komponisten, Regisseuren und Konzeptkünstlern immer wieder neue Impulse. Seit der Atomkatastrophe von Fukushima engagiert er sich US/JP 2017, 102 Minuten, FSK 6, Dolby Digital 2.0 zudem stark als Umweltaktivist und gilt als einer der Wortführer der Anti-Atomkraft-Bewegung in Japan. + 5.1, Region 2 Regisseur Stephen Nomura Schible hat den Komponisten seit 2012 mit der Kamera begleitet. 2014 wird bei Sakamoto Mundrachenkrebs REGIE Stephen Nomura Schible diagnostiziert, und der Musiker bricht alle Projekte ab. Als die Dreh- KAMERA Neo S. Sora arbeiten weitergehen können, zieht Sakamoto vor dem Hintergrund MIT Ryuichi Sakamoto u.a. der ökologischen Situation seines Heimatlandes und seiner persön- lichen Lebenskrise Resümee. Archivmaterial aus dem vielgestaltigem SPRACHE japanisch-englische Originalfassung Künstlerleben stellt der Film neben aktuelle Bilder, in denen der Kom- UNTERTITEL Deutsch ponist mit neuen Kräften wieder zurück zu seiner Arbeit findet, zurück BESTELL-NR. D258 zu seiner Suche nach Klängen, die der Wahrnehmung unserer Welt neue Wege eröffnen, zurück zu einem neuen musikalischen Ausdruck. -

Bibliographie Sur Sakamoto Ryûichi

Bibliographie sur Sakamoto Ryûichi Bibliographie faite à l’occasion de la soirée : Ryûichi Sakamoto dis.play, avec une création visuelle de Shiro Takatani 7 et 8 mars 2018 à la Maison de la culture du Japon à Paris. Livres Currid, Brian, Wittier Treat, John (dir.), “Finally, I reach to Africa”: Ryuichi Sakamoto and sounding Japan(ese) , in Contemporary Japan and popular culture . Richmond, Surrey [England] : Curzon, 1996. pp 69-102. (cote : 952.04 / Tj) McClure, Steve, Nipponpop. Tokyo / Boston: Tuttle Publishing, 1998. pp 118-119. (cote : 780 / MS) Revues • 「坂本龍龍龍一」龍一」、美術手帳、2017.05 、N° 1053. pp. 9-99. • 「坂本龍龍龍一」、龍一」、ユリイカ、2009 、vol. 41-05. Audiovisuel CD : Ȏnuki, Takeo, Sakamoto, Ryûichi, Utau : A project of Taeko Onuki and Ryuichi Sakamoto . Commons, 2010. (cote : CD / 784 – 25510) Yamashita, Yôsuke, Laswell, Bill, Sakamoto, Ryûichi, Asian games. 1993. (cote : CD / 785 –18206 ) Sakamoto, Ryûichi, Gohatto . Editions Milan Music, 2000. (cote : CD / 786 – 12603 ) Sakamoto, Ryûichi, Piano works. ProPiano Records, 2000. (cote : CD / 781 – 25473 ) Sakamoto, Ryûichi, The end of Asia . Nippon Columbia Co., 1997. (cote : CD / 781 – 18236 ) Sakamoto, Ryûichi, Sweet revenge. güt, 1994. (cote : CD / 781 – 18147 ) Sakamoto, Ryûichi, Gruppo musicale. Midi Inc, 1993. (cote : CD / 784 – 18146 ) Sakamoto, Ryûichi, Neo Geo. CBS /Sony, 1987. (cote : CD / 784 – 18156 ) Sakamoto, Ryûichi, Miraiha Yaro. Midi Inc, 1986. (cote : CD / 784 – 18157 ) 1 Bibliographie sur Sakamoto Ryûichi DVD : Oshima, Nagisa, Furyo. National Film Trustee Company, 1982. 118 min. (cote : DVD / C / 232) Oshima, Nagisa, Tabou (Gohatto). Studio Canal, coll. Auteurs, 1999. 94 min. (cote : DVD /C /23) Articles de Revue de Presse, de 2000 à 2017 : 2017 • 19/12/17.