5 Volt Intel Strataflash Memory Provides the Highest Levels of Quality and Reliability

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

The Past, Present, and Future of SD Memory Cards

The Past, Present, and Future of SD Memory Cards Douglas Wong Toshiba America Electronic Components, Inc. Flash Memory Summit 2011 Santa Clara, CA 1 Early Flash Memory Cards in the 90s PCMCIA ATA Card CompactFlash Miniature Card SmartMedia (aka SSFDC: solid state floppy disk card) 2011/8/8 2 SD Card Announcement MATSUSHITA ELECTRIC, SANDISK AND TOSHIBA AGREE TO JOIN FORCES TO DEVELOP AND PROMOTE NEXT GENERATION SECURE MEMORY CARD SD (Secure Digital) Memory Card Expected To Unleash Wave Of New Digital AV (Audio/Video) Consumer Products And Enable Internet And Wireless E-Commerce. REDWOOD CITY, CA, (Aug. 25, 1999) - Matsushita Electric Industrial Co., Ltd. (NYSE:MC), best known by its Panasonic brand name, SanDisk Corporation (NASDAQ:SNDK) and Toshiba Corporation have reached an agreement on comprehensive collaboration to jointly develop, specify and widely promote a next generation secure memory card. The announcement was made today at joint press conferences in Tokyo, Japan, Osaka, Japan and Redwood City, CA. … Powerful security and copy protection (SDMI compliant) …The security level has been designed to comply with both current and future SDMI (Secure Digital Music Initiative) portable device requirements. Sampling of the new SD Memory Card will begin in the first quarter of 2000. Production shipments are expected to commence in the second quarter of 2000. It is expected that application products that use the new card will be available in the first half of next year. 2011/8/8 3 SD Card Security Elements 2011/8/8 4 SD Association Note: SD, microSD, SDHC, microSDHC, SDXC, microSDXC 2011/8/8 5 and smartSD Logos are trademarks of SD-3C, LLC SD Family Roadmap 2011/8/8 6 SD Standard Roadmap Basic Spec. -

PC Card Adapter Reference

E TECHNICAL PAPER PC Card Adapter Reference November 1996 Order Number: 297719-001 Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications. Intel may make changes to specifications and product descriptions at any time, without notice. *Third-party brands and names are the property of their respective owners. Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order. Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from: Intel Corporation P.O. Box 7641 Mt. Prospect, IL 60056-7641 or call 1-800-879-4683 COPYRIGHT © INTEL CORPORATION, 1996 CG-041493 E TECHNICAL PAPER CONTENTS PAGE 1.0 INTRODUCTION .......................................................................................................................................5 ACMA COMPUTERS INCORPORATED ........................................................................................................6 -

Ammc0xxa 2, 4, Or 8 Megabyte 5.0 Volt-Only Flash Miniature Card

PRELIMINARY AmMC0XXA 2, 4, or 8 Megabyte 5.0 Volt-only Flash Miniature Card DISTINCTIVE CHARACTERISTICS ■ Available in industrial temperature grade (–40°C to +85°C) ■ 2, 4, or 8 Mbytes of addressable Flash memory ■ Miniature Card standard form factor ■ 5.0 Volt-only, single power supply operation — True interchangeability — Write and read voltage: 5.0 V ± 10% — 60-pad connector — No additional supply current required for VPP — Supports multiple technologies ■ Fast access time — Sonic welded stainless steel case — 100 or 150 ns access time — PCMCIA Type II adapter available ■ CMOS low power consumption — Selectable byte- or word-wide configuration — Typical active read current: — Small form factor (38 mm x 33 mm x 3.5 mm) 70 mA (word mode) ■ 60 connection bus — Typical active erase/write current: 100 mA (word mode) — 16-bit data bus — Typical standby current: — 25-bit address bus 10 µA (8 Mbyte card) — Easy system integration ■ High write endurance — Low cost implementation — Guaranteed minimum 100,000 write/erase — Low cost cards cycles per card ■ Consumer-friendly mechanicals — More than 1,000,000 cycles per card typical — User can easily insert and remove card, upgrade memory, and add applications ■ Uniform sector architecture ■ — 64K byte individually useable sectors Voltage level keying — Erase Suspend/Resume increases system level — Does not allow a 5 V card to plug into a 3 V performance system and vice versa — BUSY# and RESET# signals — Single power supply design — System does not need a separate program ■ Zero data retention power voltage supply; only one is necessary to read — No power required to retain data and write GENERAL DESCRIPTION Am29F017B Flash Memory devices, ensuring high reli- ability and excellent performance. -

Windows XP Compatibility Located at This Patch Will Not Work on Any Camedia Master 2.5 Other Operating System

TWO CORPORATE CENTER DRIVE MELVILLE, NY 11747- 3157 DIGITAL TECHNICAL SUPPORT CONSUMER PRODUCTS GROUP (888) 553- 4448 http://support.olympusamerica.com Windows Compatibility for Digital Products Windows compatibility with Olympus digital products is supplied below by model. This information will be updated as additional testing is completed. Windows Compatibility For Camedia Master Software Versions Software Version Remarks Camedia Master 4.3 Windows 98, 98SE, 2000, ME, and XP are fully supported with Camedia Master 4.3 Camedia Master 4.2 Windows 98, 98SE, 2000, ME, and XP are fully supported with Camedia Master 4.2 Camedia Master 4.1 Windows 98, 2000, ME, and XP are fully supported with Camedia Master 4.1 Camedia Master 4.0 Windows 98, 2000, ME, and XP are fully supported with Camedia Master 4.0. In order to use the drag and drop functionality in Windows XP you will need to download and install the Camedia Master 2.51 patch for Windows XP compatibility located at http://www.olympusamerica.com/files/cm251_update.exe This patch will not work on any Camedia Master 2.5 other operating system. While you can download images using Camedia Master 2.0, you may experience incompatibilities when using the drag and drop Camedia Master 2.0 feature in Windows 98, 2000, ME, and XP. Digital Vision 3.0 The Digital Vision 3.0 software is functional but not officially supported with Windows 98, 2000, ME, and XP. Olympus America Inc. Page 1 of 7 Last updated on July 14, 2004 TWO CORPORATE CENTER DRIVE MELVILLE, NY 11747- 3157 DIGITAL TECHNICAL SUPPORT CONSUMER PRODUCTS GROUP (888) 553- 4448 http://support.olympusamerica.com Windows Compatibility For Auto Connect USB Digital Cameras Model Original Software Remarks C-755 Zoom C-725 Zoom C-8080 Wide Zoom C-765 Ultra Zoom The C-770 Ultra Zoom is shipped with Camedia Master 4.2SE. -

Bar No. 171552) EVAN R

Case3:10-cv-03098-JSW Document105 Filed09/16/11 Page1 of 60 1 SIMON J. FRANKEL (Bar No. 171552) EVAN R. COX (Bar No. 133229) 2 COVINGTON & BURLING LLP One Front Street, 35th Floor 3 San Francisco, California 94111 Telephone: (415) 591-6000 4 Facsimile: (415) 591-6091 Email: [email protected] 5 [email protected] 6 TIMOTHY C. HESTER* DEREK LUDWIN* 7 JONATHAN GIMBLETT* J. MAREN SCHMIDT** 8 COVINGTON & BURLING LLP 1201 Pennsylvania Avenue, N.W. 9 Washington, D.C. 20004-2401 Telephone: (202) 662-6000 10 Facsimile: (202) 662-6291 Email: [email protected] 11 * admitted pro hac vice ** pro hac vice application pending 12 Attorneys for Plaintiff SAMSUNG ELECTRONICS CO., LTD 13 14 UNITED STATES DISTRICT COURT 15 FOR THE NORTHERN DISTRICT OF CALIFORNIA 16 SAN FRANCISCO DIVISION 17 18 SAMSUNG ELECTRONICS CO., LTD., Case No. 10-3098 JSW 19 a Korean corporation, 20 Plaintiff, SECOND AMENDED COMPLAINT 21 v. DEMAND FOR JURY TRIAL 22 PANASONIC CORPORATION, a Japanese corporation; PANASONIC 23 CORPORATION OF NORTH AMERICA, a Delaware corporation; and SD-3C LLC, a 24 Delaware limited liability company. 25 Defendants. 26 27 28 SECOND AMENDED COMPLAINT Case No. 10-3098 JSW Case3:10-cv-03098-JSW Document105 Filed09/16/11 Page2 of 60 1 Plaintiff Samsung Electronics Co., Ltd. (“Samsung”), by its attorneys, brings this 2 action for damages, declaratory judgment and injunctive relief, against Defendants Panasonic 3 Corporation, Panasonic Corporation of North America (collectively “Panasonic”) and SD-3C 4 LLC (“SD-3C”) (together with Panasonic, “Defendants”). 5 This Second Amended Complaint is filed in response to the Court’s Order of 6 August 25, 2011, dismissing the First Amended Complaint with leave to amend. -

Flash Memory Technology

10 FLASH MEMORY TECHNOLOGY OVERVIEW Flash memory technology is a mix of EPROM and EEPROM technologies. The term ÒflashÓ was chosen because a large chunk of memory could be erased at one time. The name, therefore, dis- tinguishes flash devices from EEPROMs, where each byte is erased individually. Flash memory technology is today a mature technology. It is a strong competitor to other non- volatile memories such as EPROMs and EEPROMs, and to some DRAM applications. HOW THE DEVICE WORKS The more common elementary flash cell consists of one transistor ONO DIELECTRIC POLY 2 WORD/SELECT with a floating gate, similar to an POLY 1 FLOATING EPROM cell. However, technology GATE and geometry differences between N+ S/D flash devices and EPROMs exist. In N+ S/D particular, the gate oxide between the silicon and the floating gate is thinner for flash technology. EPROM MEMORY CELL Source and drain diffusions are also different. These differences allow the flash device to be programmed POLYCIDE and erased electrically. Figures 10- ONO 1 and 10-2 show a comparison OXIDE ON N+ between a flash memory cell and an POLY 1 EPROM cell from a same manufac- N+ S/D turer (AMD) with the same technol- GATE OXIDE 1 ogy complexity. The cells look similar since the gate oxide thick- FLASH MEMORY CELL ness and the source/drain diffusion Photos by ICE, “Memory 1997” 22482 differences are not visible in the Figure 10-1. AMD EPROM Versus AMD Flash Memory Cells photographs. INTEGRATED CIRCUIT ENGINEERING CORPORATION 10-1 Flash Memory Technology Cell Gate Type Density Date Code Cell Size Length Flash 4Mbit 9406 6µm2 0.7µm EPROM 1Mbit 9634 5.52µm2 0.7µm Source: ICE, "Memory 1997" 22483 Figure 10-2. -

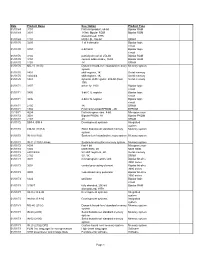

Date Product Name Description Product Type 01/01/69 3101 First

Date Product Name Description Product Type 01/01/69 3101 first Intel product, 64-bit Bipolar RAM 01/01/69 3301 1K-bit, Bipolar ROM Bipolar ROM discontinued, 1976 01/01/69 1101 MOS LSI, 256-bit SRAM 01/01/70 3205 1-of-8 decoder Bipolar logic circuit 01/01/70 3404 6-bit latch Bipolar logic circuit 01/01/70 3102 partially decoded, 256-bit Bipolar RAM 01/01/70 3104 content addressable, 16-bit Bipolar RAM 01/01/70 1103 1K DRAM 01/01/70 MU-10 (1103) Dynamic board-level standard memory Memory system system 01/01/70 1401 shift register, 1K Serial memory 01/01/70 1402/3/4 shift register, 1K Serial memory 01/01/70 1407 dynamic shift register, 200-bit (Dual Serial memory 100) 01/01/71 3207 driver for 1103 Bipolar logic circuit 01/01/71 3405 3-bit CTL register Bipolar logic circuit 01/01/71 3496 4-bit CTL register Bipolar logic circuit 01/01/71 2105 1K DRAM 01/01/71 1702 First commercial EPROM - 2K EPROM 11/15/71 4004 first microprocessor, 4-bit Microprocessor 01/01/72 3601 Bipolar PROM, 1K Bipolar PROM 01/01/72 2107 4K DRAM 01/01/72 SIM 4, SIM 8 Development systems Integrated system 01/01/72 CM-50 (1101A) Static board-level standard memory Memory system system 01/01/72 IN-10 (1103) System-level standard memory system Memory system 01/01/72 IN-11 (1103) Univac System-level custom memory system Memory system 01/01/72 8008 first 8-bit Microprocessor 01/01/72 1302 MOS ROM, 2K MOS ROM 01/01/72 2401/2/3/4 5V shift registers, 2K Serial memory 01/01/72 2102 5V, 1K SRAM 01/01/73 3001 microprogram control unit Bipolar bit-slice 3000 series 01/01/73 3002 central -

Intel Strataflash ® Memory

Intel StrataFlash® Memory (J3) 256-Mbit (x8/x16) Datasheet Product Features ■ Performance ■ Architecture —110/115/120/150 ns Initial Access Speed —Multi-Level Cell Technology: High —125 ns Initial Access Speed (256 Mbit Density at Low Cost density only) —High-Density Symmetrical 128-Kbyte —25 ns Asynchronous Page mode Reads Blocks —256 Mbit (256 Blocks) (0.18µm only) —30 ns Asynchronous Page mode Reads —128 Mbit (128 Blocks) (256Mbit density only) —64 Mbit (64 Blocks) —32-Byte Write Buffer —32 Mbit (32 Blocks) —6.8 µs per byte effective ■ Quality and Reliability programming time —Operating Temperature: ■ Software -40 °C to +85 °C —Program and Erase suspend support —100K Minimum Erase Cycles per Block —Flash Data Integrator (FDI), Common —0.18 µm ETOX™ VII Process (J3C) Flash Interface (CFI) Compatible —0.25 µm ETOX™ VI Process (J3A) ■ Security ■ Packaging and Voltage —128-bit Protection Register —56-Lead TSOP Package —64-bit Unique Device Identifier —64-Ball Intel® Easy BGA Package —64-bit User Programmable OTP Cells —Lead-free packages available —48-Ball Intel® VF BGA Package (32 and —Absolute Protection with VPEN = GND —Individual Block Locking 64 Mbit) (x16 only) —Block Erase/Program Lockout during —VCC = 2.7 V to 3.6 V Power Transitions —VCCQ = 2.7 V to 3.6 V Capitalizing on Intel’s 0.25 and 0.18 micron, two-bit-per-cell technology, the Intel StrataFlash® Memory (J3) device provides 2X the bits in 1X the space, with new features for mainstream performance. Offered in 256- Mbit (32-Mbyte), 128-Mbit (16-Mbyte), 64-Mbit, and 32-Mbit densities, the J3 device brings reliable, two-bit- per-cell storage technology to the flash market segment. -

Modern and Digitalized USB Device with Extendable Memory Capacity

(IJACSA) International Journal of Advanced Computer Science and Applications, Vol. 3, No. 11, 2012 Modern and Digitalized USB Device With Extendable Memory Capacity J. Nandini Meeraa, S. Devi C. Chithiraikkayalvizhi K. Rathina Kumar Abirami, N. Indhuja, R. Aravind Dept of ECE, Final year Assistant Prof, Dept of ECE Dept of CSE, Final year Sri Krishna College of Engineering Knowledge Institute of Technology NSIT, Salem, India Coimbatore, India Salem, India Abstract—This paper proposes a advance technology which is in today’s market. The main idea of this paper is change this completely innovative and creative. The urge of inventing this trend and bring into the advanced concept of the adjustable proposal lies on the bases of the idea of making a pen drive have memory capacity pen drive devices. an extendable memory capacity with a modern and digitalized look. This device can operate without the use of a computer This process allows the pen drive to have extendable slots system or a mobile. The computerized pen drive has a display through which additional memory cards can be inserted in unit to display the contents of the pen drive and in-built USB order to increase the size of the memory capacity of the slots to perform data transmission to other pen drives directly computerized pen drive. These are the brief introduction about without the use of the computer system. The implementation of the modern and digitalized USB device with extendable the extendable memory slots to the computerized pen drive memory capacity and the concept implementation are described makes it a modern digitalized and extendable USB device. -

5 the Flash Memory Market

5 THE FLASH MEMORY MARKET 1996 FACTS 1997 FORECAST Market Size: $2,610 million Market Size: $3,000 million Shipments: 359 million Shipments: 554 million ASP: $7.27 ASP: $5.41 OVERVIEW In the semiconductor hierarchy, flash is a member of the non-volatile family (Figure 5-1). Expanding the non-volatile memory family (Figure 5-2), flash memory represents a middle-of-the- road alternative in terms of cost and functionality. Figure 5-3 looks more closely at how flash memory compares with other non-volatile devices, specifically, the EPROM and EEPROM. Lower Cost Per Bit Increased Functionality SRAM DRAM NON-VOLATILE MEMORY (ROM) Source: AMD/ICE, "Memory 1997" 20588 Figure 5-1. Semiconductor Memory Hierarchy The flash memory market is one that ICE projects will be among the fastest growing semiconduc- tor product segments through the year 2002. Though currently not as big as the DRAM or SRAM markets, its sales growth makes it an important market to follow. Over the last five years, the flash memory market matured at a rapid pace. Contributing to this were new systems and products that are smarter, integrated, all-encompassing, and more eco- nomical than ever before. Also contributing to flash market growth was the gradual acceptance of industry-wide specifications. The flash industry has grown with the adoption of various inter- face specifications—especially those relating to the PC card market. INTEGRATED CIRCUIT ENGINEERING CORPORATION 5-1 The Flash Memory Market Lower Cost Per Bit Increased Functionality NVRAM EEPROM FLASH EPROM ROM Source: AMD/ICE, "Memory 1997" 20589 Figure 5-2. -

Disk Imaging Report: Hard Drive, Flash Drive, Or Memory Card

Disk Imaging Report Conservation Department Hard Disk Drive, Flash Drive, Memory Card Section 1: Disk Image Acquisition Source Media Information Artist: Artwork Title: Version Information: Component Number of Source Media: If multiple drives inside computer, number of source media with explanation of drive position and connection: [X of X] (Note: Include information below if not included in disk imaging program's report) Drive Type: [Internal] [External] Storage Technology: [Solid State Drive] [Hard Disk Drive] [Hybrid/SSHD] Make: Model Name: Model Number: Serial Number: Date of Manufacture: [YYYY-MM-DD] Listed capacity of drive: [in MB, GB, or TB] Form Factor: [2.5"] [3.5"] [Memory Card] [Flash Drive] [Other] Connection type: [SCSI] [PATA/IDE] [SATA] [USB 3.0] [USB 2.0] [Thunderbolt] [Thunderbolt 2] [Thunderbolt 3] [Firewire 400] [Firewire 800] [eSATA] [PCIe] [Apple PCIe] [Secure Digital] [miniSD] [microSD] [CompactFlash] [CFast] [PCMCIA] [SmartMedia] [Miniature Card] [Sony Memory Stick] Number of Partitions on original drive or card: Partition 1 name: Partition 2 name: Partition 3 name: Partition 4 name: Disk Image Information Component Number of Disk Image: Filename: File Format: [E01] [raw/dd] File size: Checksum: Checksum algorithm: Imaging Program (including version number): Date of creation: Name of technician: Were there bad sectors found during imaging: YES/NO Describe reasoning and method used to create disk image (document hardware used including type of forensic bridge, cables used, adapters used, different software and tools used to recover data): Describe method used to obtain hardware/software information about the computer (what program was used, etc.): Section 2 - Disk Image QC Was the disk image verified (specify program or method that verified the image)? Date: Name: Checksum of bitstream (for Forensic images only): Checksum algorithm: Test 1A Attempt to open and explore the files within the disk image: PASS/FAIL Test 1B Examine the partitions of the disk image. -

(12) United States Patent (10) Patent No.: US 7418,344 B2 Holtzman Et Al

USOO741834.4B2 (12) United States Patent (10) Patent No.: US 7418,344 B2 Holtzman et al. (45) Date of Patent: Aug. 26, 2008 (54) REMOVABLE COMPUTER WITH MASS 5,418,752 A 5/1995 Harari et al. STORAGE (75) Inventors: Michael Holtzman, Kfar Vradim (IL); Yosi Pinto, Kfar-Vradim (IL) (Continued) (73) Assignee: SanDisk Corporation, Milpitas,- 0 CA FOREIGN PATENT DOCUMENTS (US) DE 298 06899 U1 7, 1998 (*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 370 days. (Continued) (21) Appl. No.: 09/924,185 OTHER PUBLICATIONS “The Free On-Line Dictionary of Computing.” Entry stream. (22) Filed: Aug. 2, 2001 Online Nov. 6, 1996. Retrieved from Internet Jan. 7, 2005. <http:// foldoc.doc.ic.ac.uk/foldoc/foldoc.cgi?query=streamc. * (65) Prior Publication Data US 2003/0O28699 A1 Feb. 6, 2003 (Continued) Primary Examiner Mark Rinehart (51) Int. Cl. Assistant Examiner Thomas J Cleary G06F 3/00 (2006.01) (74) Attorney, Agent, or Firm—Brinks Hofer Gilson & Lione G06F 3/4 (2006.01) G06F 3/00 (2006.01) (57) ABSTRACT G06F 5/00 (2006.01) G06F 3/12 (2006.01) G06F I3/38 (2006.01) The present invention provides a detachable add-on card unit H05K 7/10 (2006.01) to a host system that combines mass storage capability and a (52) U.S. Cl. ........................... 701/301; 710/52; 710/65; processor on the same card. The card can receive data from 710,305 the host, process the data, and store it in processed form, as (58) Field of Classification Search ....................