Intel® Architecture Instruction Set Extensions Programming Reference

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Intel® Architecture Instruction Set Extensions and Future Features Programming Reference

Intel® Architecture Instruction Set Extensions and Future Features Programming Reference 319433-037 MAY 2019 Intel technologies features and benefits depend on system configuration and may require enabled hardware, software, or service activation. Learn more at intel.com, or from the OEM or retailer. No computer system can be absolutely secure. Intel does not assume any liability for lost or stolen data or systems or any damages resulting from such losses. You may not use or facilitate the use of this document in connection with any infringement or other legal analysis concerning Intel products described herein. You agree to grant Intel a non-exclusive, royalty-free license to any patent claim thereafter drafted which includes subject matter disclosed herein. No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document. The products described may contain design defects or errors known as errata which may cause the product to deviate from published specifica- tions. Current characterized errata are available on request. This document contains information on products, services and/or processes in development. All information provided here is subject to change without notice. Intel does not guarantee the availability of these interfaces in any future product. Contact your Intel representative to obtain the latest Intel product specifications and roadmaps. Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling 1- 800-548-4725, or by visiting http://www.intel.com/design/literature.htm. Intel, the Intel logo, Intel Deep Learning Boost, Intel DL Boost, Intel Atom, Intel Core, Intel SpeedStep, MMX, Pentium, VTune, and Xeon are trademarks of Intel Corporation in the U.S. -

Horizontal PDF Slides

1 2 Speed, speed, speed $1000 TCR hashing competition D. J. Bernstein Crowley: “I have a problem where I need to make some University of Illinois at Chicago; cryptography faster, and I’m Ruhr University Bochum setting up a $1000 competition funded from my own pocket for Reporting some recent work towards the solution.” symmetric-speed discussions, Not fast enough: Signing H(M), especially from RWC 2020. where M is a long message. Not included in this talk: “[On a] 900MHz Cortex-A7 NISTLWC. • [SHA-256] takes 28.86 cpb ::: Short inputs. • BLAKE2b is nearly twice as FHE/MPC ciphers. • fast ::: However, this is still a lot slower than I’m happy with.” 1 2 3 Speed, speed, speed $1000 TCR hashing competition Instead choose random R and sign (R; H(R; M)). D. J. Bernstein Crowley: “I have a problem where I need to make some Note that H needs only “TCR”, University of Illinois at Chicago; cryptography faster, and I’m not full collision resistance. Ruhr University Bochum setting up a $1000 competition Does this allow faster H design? funded from my own pocket for TCR breaks how many rounds? Reporting some recent work towards the solution.” symmetric-speed discussions, Not fast enough: Signing H(M), especially from RWC 2020. where M is a long message. Not included in this talk: “[On a] 900MHz Cortex-A7 NISTLWC. • [SHA-256] takes 28.86 cpb ::: Short inputs. • BLAKE2b is nearly twice as FHE/MPC ciphers. • fast ::: However, this is still a lot slower than I’m happy with.” 1 2 3 Speed, speed, speed $1000 TCR hashing competition Instead choose random R and sign (R; H(R; M)). -

A Superscalar Out-Of-Order X86 Soft Processor for FPGA

A Superscalar Out-of-Order x86 Soft Processor for FPGA Henry Wong University of Toronto, Intel [email protected] June 5, 2019 Stanford University EE380 1 Hi! ● CPU architect, Intel Hillsboro ● Ph.D., University of Toronto ● Today: x86 OoO processor for FPGA (Ph.D. work) – Motivation – High-level design and results – Microarchitecture details and some circuits 2 FPGA: Field-Programmable Gate Array ● Is a digital circuit (logic gates and wires) ● Is field-programmable (at power-on, not in the fab) ● Pre-fab everything you’ll ever need – 20x area, 20x delay cost – Circuit building blocks are somewhat bigger than logic gates 6-LUT6-LUT 6-LUT6-LUT 3 6-LUT 6-LUT FPGA: Field-Programmable Gate Array ● Is a digital circuit (logic gates and wires) ● Is field-programmable (at power-on, not in the fab) ● Pre-fab everything you’ll ever need – 20x area, 20x delay cost – Circuit building blocks are somewhat bigger than logic gates 6-LUT 6-LUT 6-LUT 6-LUT 4 6-LUT 6-LUT FPGA Soft Processors ● FPGA systems often have software components – Often running on a soft processor ● Need more performance? – Parallel code and hardware accelerators need effort – Less effort if soft processors got faster 5 FPGA Soft Processors ● FPGA systems often have software components – Often running on a soft processor ● Need more performance? – Parallel code and hardware accelerators need effort – Less effort if soft processors got faster 6 FPGA Soft Processors ● FPGA systems often have software components – Often running on a soft processor ● Need more performance? – Parallel -

Broadwell Skylake Next Gen* NEW Intel NEW Intel NEW Intel Microarchitecture Microarchitecture Microarchitecture

15 лет доступности IOTG is extending the product availability for IOTG roadmap products from a minimum of 7 years to a minimum of 15 years when both processor and chipset are on 22nm and newer process technologies. - Xeon Scalable (w/ chipsets) - E3-12xx/15xx v5 and later (w/ chipsets) - 6th gen Core and later (w/ chipsets) - Bay Trail (E3800) and later products (Braswell, N3xxx) - Atom C2xxx (Rangeley) and later - Не включает в себя Xeon-D (7 лет) и E5-26xx v4 (7 лет) 2 IOTG Product Availability Life-Cycle 15 year product availability will start with the following products: Product Discontinuance • Intel® Xeon® Processor Scalable Family codenamed Skylake-SP and later with associated chipsets Notification (PDN)† • Intel® Xeon® E3-12xx/15xx v5 series (Skylake) and later with associated chipsets • 6th Gen Intel® Core™ processor family (Skylake) and later (includes Intel® Pentium® and Celeron® processors) with PDNs will typically be issued no later associated chipsets than 13.5 years after component • Intel Pentium processor N3700 (Braswell) and later and Intel Celeron processors N3xxx (Braswell) and J1900/N2xxx family introduction date. PDNs are (Bay Trail) and later published at https://qdms.intel.com/ • Intel® Atom® processor C2xxx (Rangeley) and E3800 family (Bay Trail) and late Last 7 year product availability Time Last Last Order Ship Last 15 year product availability Time Last Last Order Ship L-1 L L+1 L+2 L+3 L+4 L+5 L+6 L+7 L+8 L+9 L+10 L+11 L+12 L+13 L+14 L+15 Years Introduction of component family † Intel may support this extended manufacturing using reasonably Last Time Order/Ship Periods Component family introduction dates are feasible means deemed by Intel to be appropriate. -

Multiprocessing Contents

Multiprocessing Contents 1 Multiprocessing 1 1.1 Pre-history .............................................. 1 1.2 Key topics ............................................... 1 1.2.1 Processor symmetry ...................................... 1 1.2.2 Instruction and data streams ................................. 1 1.2.3 Processor coupling ...................................... 2 1.2.4 Multiprocessor Communication Architecture ......................... 2 1.3 Flynn’s taxonomy ........................................... 2 1.3.1 SISD multiprocessing ..................................... 2 1.3.2 SIMD multiprocessing .................................... 2 1.3.3 MISD multiprocessing .................................... 3 1.3.4 MIMD multiprocessing .................................... 3 1.4 See also ................................................ 3 1.5 References ............................................... 3 2 Computer multitasking 5 2.1 Multiprogramming .......................................... 5 2.2 Cooperative multitasking ....................................... 6 2.3 Preemptive multitasking ....................................... 6 2.4 Real time ............................................... 7 2.5 Multithreading ............................................ 7 2.6 Memory protection .......................................... 7 2.7 Memory swapping .......................................... 7 2.8 Programming ............................................. 7 2.9 See also ................................................ 8 2.10 References ............................................. -

The Intel X86 Microarchitectures Map Version 2.0

The Intel x86 Microarchitectures Map Version 2.0 P6 (1995, 0.50 to 0.35 μm) 8086 (1978, 3 µm) 80386 (1985, 1.5 to 1 µm) P5 (1993, 0.80 to 0.35 μm) NetBurst (2000 , 180 to 130 nm) Skylake (2015, 14 nm) Alternative Names: i686 Series: Alternative Names: iAPX 386, 386, i386 Alternative Names: Pentium, 80586, 586, i586 Alternative Names: Pentium 4, Pentium IV, P4 Alternative Names: SKL (Desktop and Mobile), SKX (Server) Series: Pentium Pro (used in desktops and servers) • 16-bit data bus: 8086 (iAPX Series: Series: Series: Series: • Variant: Klamath (1997, 0.35 μm) 86) • Desktop/Server: i386DX Desktop/Server: P5, P54C • Desktop: Willamette (180 nm) • Desktop: Desktop 6th Generation Core i5 (Skylake-S and Skylake-H) • Alternative Names: Pentium II, PII • 8-bit data bus: 8088 (iAPX • Desktop lower-performance: i386SX Desktop/Server higher-performance: P54CQS, P54CS • Desktop higher-performance: Northwood Pentium 4 (130 nm), Northwood B Pentium 4 HT (130 nm), • Desktop higher-performance: Desktop 6th Generation Core i7 (Skylake-S and Skylake-H), Desktop 7th Generation Core i7 X (Skylake-X), • Series: Klamath (used in desktops) 88) • Mobile: i386SL, 80376, i386EX, Mobile: P54C, P54LM Northwood C Pentium 4 HT (130 nm), Gallatin (Pentium 4 Extreme Edition 130 nm) Desktop 7th Generation Core i9 X (Skylake-X), Desktop 9th Generation Core i7 X (Skylake-X), Desktop 9th Generation Core i9 X (Skylake-X) • Variant: Deschutes (1998, 0.25 to 0.18 μm) i386CXSA, i386SXSA, i386CXSB Compatibility: Pentium OverDrive • Desktop lower-performance: Willamette-128 -

Intel® Omni-Path Architecture Overview and Update

The architecture for Discovery June, 2016 Intel Confidential Caught in the Vortex…? Business Efficiency & Agility DATA: Trust, Privacy, sovereignty Innovation: New Economy Biz Models Macro Economic Effect Growth Enablers/Inhibitors Intel® Solutions Summit 2016 2 Intel® Solutions Summit 2016 3 Intel Confidential 4 Data Center Blocks Reduce Complexity Intel engineering, validation, support Data Center Blocks Speed time to market Begin with a higher level of integration HPC Cloud Enterprise Storage Increase Value VSAN Ready HPC Compute SMB Server Block Reduce TCO, value pricing Block Node Fuel innovation Server blocks for specific segments Focus R&D on value-add and differentiation Intel® Solutions Summit 2016 5 A Holistic Design Solution for All HPC Needs Intel® Scalable System Framework Small Clusters Through Supercomputers Compute Memory/Storage Compute and Data-Centric Computing Fabric Software Standards-Based Programmability On-Premise and Cloud-Based Intel Silicon Photonics Intel® Xeon® Processors Intel® Solutions for Lustre* Intel® Omni-Path Architecture HPC System Software Stack Intel® Xeon Phi™ Processors Intel® SSDs Intel® True Scale Fabric Intel® Software Tools Intel® Xeon Phi™ Coprocessors Intel® Optane™ Technology Intel® Ethernet Intel® Cluster Ready Program Intel® Server Boards and Platforms 3D XPoint™ Technology Intel® Silicon Photonics Intel® Visualization Toolkit Intel Confidential 14 Parallel is the Path Forward Intel® Xeon® and Intel® Xeon Phi™ Product Families are both going parallel How do we attain extremely high compute -

Intel Atom Processor E3800 Product Families in Retail

White Paper Intelligent Systems Intel® Celeron® Processor and Intel® Atom™ Processor E3800 Product Families Intel® Celeron® Processor and Intel® Atom™ Processor E3800 Product Families in Retail Transform user experiences in entry retail devices with full HD video decode, improved graphics, quad-core compute performance, and built-in security Introduction Advanced features include: Intelligent devices that provide HD • Media: Scalable full HD video playback video capability, compelling graphics, includes support for 10 or more responsive performance, and security are simultaneous video streams. transforming in-store retail experiences. • Graphics: Gen 7 Intel® Graphics Today’s retail customers expect POS Architecture enables enhanced visual systems, interactive kiosks, and digital processing over previous-generation signs to support rich media and graphics Intel Atom processors. experience for timely and visually compelling digital promotions and a range • Power and Form Factor: SoC with of choices at checkout, with confidence smaller package size and industrial “The Intel Celeron processor and that the device provides security to temperature range is ideal for thin, protect transactional and personal data. light and environmentally adaptive Intel Atom processor E3800 entry retail devices. The Intel® Celeron® processor and Intel® product families provide full Atom™ processor E3800 product families • Compute: Quad-core processing1 HD simultaneous video decode for intelligent systems help bring these enables improved out-of-order compute capabilities to entry retail devices. performance for more responsive user capability, delivering interactive Compared to previous-generation Intel experiences. Celeron and Atom processors, this new 2-D and 3-D graphics with much • Security: Built-in hardware-assisted processor family provides significantly security enhancements include Intel® improved playback enabling improved media and graphics performance AES New Instructions (Intel® AES NI)2 and enables smaller, more power-efficient immersive visual experiences and Secure Boot. -

Intel® Atom™ Processor E3800 the Latest Low Power Platform E3800 Family Platform for Intelligent Systems

Intel® Atom™ Processor E3800 The Latest Low Power Platform E3800 Family Platform for Intelligent Systems tŚŝůĞĚĞƐŝŐŶĞĚƚŽďĞĂƚƌƵĞƚĞƐƚŽĨ/ŶƚĞů͛ƐƉĞƌĨŽƌŵĂŶĐĞŝŶƚŚĞƵůƚƌĂŵŽďŝůĞƐƉĂĐĞ͕^ŝůǀĞƌŵŽŶƚŝƐƚŚĞĮƌƐƚƚƌƵĞĂƌĐŚŝƚĞĐƚƵƌĞ ƵƉĚĂƚĞƚŽ/ŶƚĞů͛ƐƚŽŵƉƌŽĐĞƐƐŽƌƐŝŶĐĞŝƚƐŝŶƚƌŽĚƵĐƟŽŶŝŶϮϬϬϴ͘>ĞǀĞƌĂŐŝŶŐ/ŶƚĞů͛ƐĮƌƐƚϮϮŶŵƉƌŽĐĞƐƐĂŶĚĂǀĞƌLJůŽǁƉŽǁĞƌͲ ŵŝĐƌŽĂƌĐŚŝƚĞĐƚƵƌĞ͕^ŝůǀĞƌŵŽŶƚĂŝŵƐƐƋƵĂƌĞůLJĂƚƚŚĞůĂƚĞƐƚ<ƌĂŝƚĐŽƌĞƐĨƌŽŵYƵĂůĐŽŵŵĂŶĚZD͛ƐŽƌƚĞdžϭϱ͘ĂƐĞĚŽŶ ^ŝůǀĞƌŵŽŶƚ͕/ŶƚĞůΠŝŶƚƌŽĚƵĐĞƐϯϴϬϬƉƌŽĚƵĐƚĨĂŵŝůLJ͕ĂƐĞƌŝĞƐŽĨƐLJƐƚĞŵŽŶĐŚŝƉ;^ŽͿĚĞƐŝŐŶĞĚĨŽƌůŽǁͲƉŽǁĞƌ͕ĨĞĂƚƵƌĞͲƌŝĐŚ ĂŶĚŚŝŐŚůLJͲĐĂƉĂďůĞĂƉƉůŝĐĂƟŽŶƐ͘ ϯϴϬϬƉƌŽĚƵĐƚĨĂŵŝůLJƚĂŬĞƐƵƉƚŽĨŽƵƌ^ŝůǀĞƌŵŽŶƚĐŽƌĞƐ͕ĂŶĚĨŽƌƚŚĞĮƌƐƚƟŵĞŝŶĂŶƵůƚƌĂŵŽďŝůĞ/ŶƚĞů^Ž͕ŝƐƉĂŝƌĞĚǁŝƚŚ /ŶƚĞů͛ƐŽǁŶŐƌĂƉŚŝĐƐ/W͘/ŶŽƚŚĞƌǁŽƌĚƐ͕ƌĂƚŚĞƌƚŚĂŶƵƐŝŶŐĂ'WhďůŽĐŬĨƌŽŵ/ŵĂŐŝŶĂƟŽŶdĞĐŚŶŽůŽŐŝĞƐ͕E3800 product family leverages the same GPU architecture as the 3rdŐĞŶĞƌĂƟŽŶ/ŶƚĞůŽƌĞƉƌŽĐĞƐƐŽƌƐ;ĐŽĚĞŶĂŵĞĚ/ǀLJƌŝĚŐĞͿ͘ Silvermont Core Highlights Better Performance Better Power Efficiency 22nm Architecture 200 250 150 300 100 350 50 400 0 450 500 Out-of-order execuon engine Wider dynamic operang range 3D Tri-gate transistors tuned for New mul-core and system fabric Enhanced acve and idle power SoC products architecture management Architecture and design co-opmized with the process New IA instrucons extensions (Intel Core Westmere Level) Bay Trail: Not just for Atoms anymore E3800 product family combines a CPU based on Intel’s new Silver- mont architecture with a GPU that is architecturally similar to (but 4xPCIe* less powerful than) the HD 4000 graphics engine integrated in the 3rdŐĞŶĞƌĂƟŽŶ/ŶƚĞůΠŽƌĞƉƌŽĐĞƐƐŽƌƐůĂƵŶĐŚĞĚŝŶĞĂƌůLJϮϬϭϮ͘dŚĞƐĞ -

Validation Report

National Information Assurance Partnership Common Criteria Evaluation and Validation Scheme Validation Report Cisco Network Convergence System 1000 Series Report Number: CCEVS-VR--11093 Dated: 07/07/2020 Version: 1.0 National Institute of Standards and Technology National Security Agency Information Technology Laboratory Information Assurance Directorate 100 Bureau Drive 9800 Savage Road STE 6940 Gaithersburg, MD 20899 Fort George G. Meade, MD 20755-6940 Cisco Network Convergence System 1000 SeriesValidation Report Version 1.0, 07/06/2020 ACKNOWLEDGEMENTS Validation Team Paul Bicknell: Senior Validator Randy Heimann Linda Morrison: Lead Validator Clare Olin Common Criteria Testing Laboratory Chris Keenan Katie Sykes Gossamer Security Solutions, Inc. Catonsville, MD ii Cisco Network Convergence System 1000 SeriesValidation Report Version 1.0, 07/06/2020 Table of Contents Contents 1 Executive Summary .................................................................................................... 1 2 Identification ............................................................................................................... 2 3 Architectural Information ........................................................................................... 3 3.1 TOE Evaluated Configuration ............................................................................ 3 3.2 TOE Architecture ................................................................................................ 3 3.3 Physical Boundaries ........................................................................................... -

Sales Opportunity Guide

Intel® Pentium® Silver and Celeron® Processors Sales Opportunity Better Performance Faster Security And battery life Enabled Browsing better web browsing 3 UP TO UP 79% experience better Windows* browsing and sharing application hours of Security- with password 1 2 ** APPROX. UP TO UP 58% performance 10 battery life enabled managers Flexible connectivity Enhanced media and choices graphics experience graphics Gigabit Fast networking performance performance with the first Gigabit Wi-Fi PC 4 UP TO UP 2.7X improvement Wi-fi* capability on entry level systems – faster than wired Dynamically boost your display visibility outdoors in sunlight with Gigabit Ethernet connection5,6 Local Adaptive Contrast Enhancement (LACE) technology 1. As projected by SYSmark* 2014 v1.5 on Intel® Pentium® Silver Processor N5000 PL1=6W TDP, 4C/4T, up to 2.7GHz, Memory: 2x2GB DDR4 2400, Storage: Intel SSD, OS: Windows* 10 RS2 vs. Intel® Pentium® Processor N3540, PL1=7.5W TDP, 4C/4T, up to 2.66GHz, Memory: 2x2GB DDR3L-1333, Storage: Intel SSD, OS: Windows* 10 RS2 > 2. As projected by 1080p Video Playback on Intel® Pentium® Silver Processor N5000 , PL1=6W TDP, 4C/4T, up to 2.7GHz, Memory: 2x2GB DDR4 2400, Storage: Intel SSD, OS: Windows* 10 RS2 Battery: 35WHr, 12.5", 1920x1080 > 3. As projected by WebXPRT* 2015 on Intel® Pentium® Silver Processor N5000 PL1=6W TDP, 4C/4T, up to 2.7GHz, Memory: 2x2GB DDR4 2400, Storage: Intel SSD, OS: Windows* 10 RS2 vs. Intel® Pentium® Processor N3540, PL1=7.5W TDP, 4C/4T, up to 2.66GHz, Memory: 2x2GB DDR3L-1333, Storage: Intel SSD, OS: Windows* 10 RS2 > 4. -

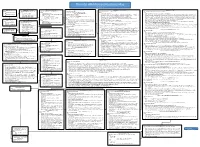

The Intel X86 Microarchitectures Map Version 2.2

The Intel x86 Microarchitectures Map Version 2.2 P6 (1995, 0.50 to 0.35 μm) 8086 (1978, 3 µm) 80386 (1985, 1.5 to 1 µm) P5 (1993, 0.80 to 0.35 μm) NetBurst (2000 , 180 to 130 nm) Skylake (2015, 14 nm) Alternative Names: i686 Series: Alternative Names: iAPX 386, 386, i386 Alternative Names: Pentium, 80586, 586, i586 Alternative Names: Pentium 4, Pentium IV, P4 Alternative Names: SKL (Desktop and Mobile), SKX (Server) Series: Pentium Pro (used in desktops and servers) • 16-bit data bus: 8086 (iAPX Series: Series: Series: Series: • Variant: Klamath (1997, 0.35 μm) 86) • Desktop/Server: i386DX Desktop/Server: P5, P54C • Desktop: Willamette (180 nm) • Desktop: Desktop 6th Generation Core i5 (Skylake-S and Skylake-H) • Alternative Names: Pentium II, PII • 8-bit data bus: 8088 (iAPX • Desktop lower-performance: i386SX Desktop/Server higher-performance: P54CQS, P54CS • Desktop higher-performance: Northwood Pentium 4 (130 nm), Northwood B Pentium 4 HT (130 nm), • Desktop higher-performance: Desktop 6th Generation Core i7 (Skylake-S and Skylake-H), Desktop 7th Generation Core i7 X (Skylake-X), • Series: Klamath (used in desktops) 88) • Mobile: i386SL, 80376, i386EX, Mobile: P54C, P54LM Northwood C Pentium 4 HT (130 nm), Gallatin (Pentium 4 Extreme Edition 130 nm) Desktop 7th Generation Core i9 X (Skylake-X), Desktop 9th Generation Core i7 X (Skylake-X), Desktop 9th Generation Core i9 X (Skylake-X) • New instructions: Deschutes (1998, 0.25 to 0.18 μm) i386CXSA, i386SXSA, i386CXSB Compatibility: Pentium OverDrive • Desktop lower-performance: Willamette-128