Macintosh LC III

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Official Apple Macintosh Pricelist (Oct 1993 Macnews Australia)

l\/1'-'� t 5.��.. .. er 1993 Issue 52 The Australian Macintosh Business Magazine NZ $6.95 (INC GST) $5.00 Apple puts PowerPC on hold TECHNICAL SUPPORT: Release of the first PowerPC Mac has been delayed until March 1994. Apple was expecting non-PowerPC How to find the answers you need! applications to run at Quadra 700 speed in emulation rnode, but some Free technical support, included in programs are only reaching LCIII the price we pay for our speed, while others software, is becoming a thing of the are not running at all. 11 past But when you're in need of help, there are a range of · Sorting through large alternative sources, including screen monitors resellers and third party Knowing the right questions to ask support providers. 22 can make your selection of a larger monitor seem less Australian company ....?; ;/,. Breakthrough daunting. We look at the issues involved, localises Newton '). in high quality and include a guide to locally available Australians using Apple's MessagePad are printing large screen ( over in for a time. Newton's hand• ...co frustrating 19") displays. 48 co"' writing is based on I recognition technology Digital prepress technology CD > recognising words has enabled a revolutionary 0 c c contained in its built- halftone that Mercury chip breaks .Q system iii .s in system dictionaries, delivers high-quality litho the speed barrier :0 :, a. Image proce sing speed will I and if the word isn't printing unmatched by ui accelerate beyone workstation 8. there it won't traditional methods. .!!! performance with the introduction of � recognise it However, an Australian third• With stochastic screening a radical new board architecture from ui :, <{ party company has come to the rescue, and there's no moires, pattern RasterOps, codenamed 'Mercury'. -

Holiday Catalog

Brilliant for what’s next. With the power to achieve anything. AirPods Pro AppleCare+ Protection Plan†* $29 Key Features • Active Noise Cancellation for immersive sound • Transparency mode for hearing and connecting with the world around you • Three sizes of soft, tapered silicone tips for a customizable fit • Sweat and water resistant1 • Adaptive EQ automatically tunes music to the shape of your ear • Easy setup for all your Apple devices2 • Quick access to Siri by saying “Hey Siri”3 • The Wireless Charging Case delivers more than 24 hours of battery life4 AirPods Pro. Magic amplified. Noise nullified. Active Noise Cancellation for immersive sound. Transparency mode for hearing what’s happening around you. Sweat and water resistant.1 And a more customizable fit for all-day comfort. AirPods® AirPods AirPods Pro with Charging Case with Wireless Charging Case with Wireless Charging Case $159 $199 $249 1 AirPods Pro are sweat and water resistant for non-water sports and exercise and are IPX4 rated. Sweat and water resistance are not permanent conditions. The charging case is not sweat or water resistant. 2 Requires an iCloud account and macOS 10.14.4, iOS 12.2, iPadOS, watchOS 5.2, or tvOS 13.2 or later. 3Siri may not be available in all languages or in all areas, and features may vary by area. 4 Battery life varies by use and configuration. See apple.com/batteries for details. Our business is part of a select group of independent Apple® Resellers and Service Providers who have a strong commitment to Apple’s Mac® and iOS platforms and have met or exceeded Apple’s highest training and sales certifications. -

Power Macintosh 6100/ WS 6150

K Service Source Power Macintosh 6100/ WS 6150 Power Macintosh 6100/60, 6100/60AV, 6100/66, 6100/66AV, 6100/DOS Compatible, and Workgroup Server 6150 K Service Source Basics Power Macintosh 6100/WS 6150 Basics Power Macintosh System Overview - 1 Power Macintosh System Overview PowerPC microprocessors are a family of processors built on reduced instruction-set computing (RISC) technology. RISC processors streamline the internal workings of computers. Whereas traditional (complex instruction-set computing, or CISC) processors contain a wide variety of instructions to handle many different tasks, RISC processors contain only those instructions that are used most often. When a complex instruction is needed, a RISC processor builds it from a combination of basic instructions. RISC processors are designed to execute these basic instructions extremely quickly. The performance gains achieved by speeding up the most-used instructions more than compensate for the time spent creating less-used instructions. Basics Power Macintosh System Overview - 2 Previously, RISC technology had been used only in high-end workstations and commercial database servers. With the introduction of Macintosh PowerPC computers, Apple succeeded in bringing RISC technology to personal computing. Key Points Three key points to remember about a PowerPC processor- based Macintosh system: It's a Macintosh; it's compatible; it offers tremendous performance. Apple's PowerPC computers feature the same user interface as their 680x0-based predecessors. Users can mix RISC- based and 680x0-based Macintosh systems on the same net- work and exchange files and disks between them. In addition, users can run both 680x0 and native PowerPC applications on the same Power Macintosh system simultaneously. -

Compusa Macintosh Products Guide Winter 1992.Pdf

Over 800 Macintosh l1t·oducts at Super Everyday Low Prices! How To Load An Apple Macintosh LC II. GreatWorks Eight full-featured At CompUSA, getting the perfect Apple® applications in one easy-to-use program. Macintosh®comp uter, configured just Word processing, data base, spreadsheet, illus the way you want is just this easy! tration and more. Everything you need to build the perfect system is right within #220)14 your reach. And of course, our friendly, knowledgeable staffers are always close by to help you load up not onlyyo ur cart, but your new computer, too! Appte• Macintosh• 12" RGB Monitor Apple's lowest cost display. Bright, vibrant colors on a high-contrast screen . .28 mm dot pitch. #9002 14 It just doesn't get any easier than this. In fact, we make • 16MHz030 it easy to load a full line of Apple• Macintosh• Processor Apple Macintosh computers, LC 4/40 Computer • 4MBRA'-.i peripherals, accessories and TI1e most affordable • 40 MB Hard Drive software . Over 800 different Madntosh color system • 1.4 MB Apple Mac• products in all! And of features a slender, modular SuperDrive· course, they're all priced design so it's easy to set up • 1 Video, 2 Serial Ports Authorized Dealer super low every day. So load and easy to use. Exce ll ent choice for business or education. • Keyboard #WJ24·1 some today. At CompUSA! Apple, the Apple logo, Mac, and ~1 a cimosh are registcrt>d tradcmarlc; of Apple Computer, In c. Quadra and SuperDrive arc trmlemarlc; of Apple Computer, Inc. A range of desktop mtd notebook contputers for business, hotne mul educati ,..~ Macintosh PCs .................. -

Macintosh LC Series/ Quadra 605

K Service Source Macintosh LC Series/ Quadra 605 Macintosh LC, Macintosh LC II, Macintosh LC III, Macintosh LC 475, Macintosh Quadra 605 K Service Source Basics Macintosh LC Series/Quadra 605 Basics Overview - 2 Overview This manual includes complete repair procedures for the Macintosh LC Series/ Quadra 605, shown at left. Figure: Macintosh LC Series, Quadra 605 K Service Source Specifications Macintosh LC Series/Quadra 605 Specifications Processor - 1 Processor LC Motorola 68020 microprocessor 16 MHz 16-bit internal data bus LC II Motorola 68030 microprocessor 16 MHz 16-bit internal data bus Burst-mode RAM access LC III Motorola 68030 microprocessor 25 MHz 32-bit internal data bus Burst-mode RAM access Coprocessor socket Specifications Processor - 2 LC 475/Quadra 605 Motorola 68LC040 microprocessor 25 MHz 32-bit internal data bus Burst-mode RAM access Specifications Memory - 3 Memory DRAM LC: 2 MB, expandable to 10 MB (100 ns or faster SIMMs) LC II: 4 MB standard, expandable to 10 MB (100 ns or faster SIMMs) LC III: 4 MB standard, expandable to 36 MB (80 ns or faster SIMMs) LC 475/Quadra 605: 4 MB or 8 MB standard, expandable to 36 MB (80 ns or faster SIMMs) ROM LC/LC II: 512 K LC III/LC 475/Quadra 605: 1 MB Specifications Memory - 4 VRAM LC: 256K VRAM, upgradable to 512K LC II: 256K VRAM SIMM, upgradable to 512K LCIII: 512K VRAM on board, upgradable to 768K LC 475/Quadra 605: Two 256K VRAM SIMMs, upgradable to 1MB Specifications Disk Storage - 5 Disk Storage Floppy Drive LC/ LC II/ LC III: Apple SuperDrive 1.4 MB Floppy Disk Drive Optional -

Gestalt Manager 1

CHAPTER 1 Gestalt Manager 1 This chapter describes how you can use the Gestalt Manager and other system software facilities to investigate the operating environment. You need to know about the 1 operating environment if your application takes advantage of hardware (such as a Gestalt Manager floating-point unit) or software (such as Color QuickDraw) that is not available on all Macintosh computers. You can also use the Gestalt Manager to inform the Operating System that your software is present and to find out about other software registered with the Gestalt Manager. The Gestalt Manager is available in system software versions 6.0.4 and later. The MPW software development system and some other development environments supply code that allows you to use the Gestalt Manager on earlier system software versions; check the documentation provided with your development system. In system software versions earlier than 6.0.4, you can retrieve a limited description of the operating environment with the SysEnvirons function, also described in this chapter. You need to read this chapter if you take advantage of specific hardware or software features that may not be present on all versions of the Macintosh, or if you wish to inform other software that your software is present in the operating environment. This chapter describes how the Gestalt Manager works and then explains how you can ■ determine whether the Gestalt Manager is available ■ call the Gestalt function to investigate the operating environment ■ make information about your own hardware or software available to other applications ■ retrieve a limited description of the operating environment even if the Gestalt Manager is not available About the Gestalt Manager 1 The Macintosh family of computers includes models that use a number of different processors, some accompanied by a floating-point unit (FPU) or memory management unit (MMU). -

From 128K to Quadra: Model by Model

Chapter 12 From 128K to Quadra: Model by Model IN THIS CHAPTER: I What the specs mean I The specs for every Mac model ever made I Secrets of the pre-PowerPC Mac models I Just how much your Mac has devalued Yes, we’ve already been told that we’re nuts to attempt the next two chapters of this book. Since 1984, Apple has created more than 140 different Mac models — including 35 different PowerBooks and 53 different Performas! Each year, Apple piles on another dozen or so new models. By the time you finish reading this page, another Performa model probably will have been born. So, writing a couple of chapters that are supposed to describe every model is an exercise in futility. But we’re going to attempt it anyway, taking the models one by one and tracking their speeds, specs, and life cycles. This chapter will cover all the Apple Macs — both desktop and portable models — from the birth of the original Macintosh 128K to the release of the PowerBook 190, the last Mac ever made that was based on Motorola’s 68000-series processor chip. When you’re finished reading this chapter, you will be one of the few people on Earth who actually knows the difference between a Performa 550, 560, 575, 577, 578, 580, and 588. 375 376 Part II: Secrets of the Machine Chapter 13 will cover every Power Mac — or, more accurately, every PowerPC-based machine (those with four-digit model numbers) — from the first ones released in 1994 to the models released just minutes before this book was printed. -

Macintosh Quadra 800/WS 80

K Service Source Macintosh Quadra 800/WS 80 Macintosh Quadra 800 Workgroup Server 80 K Service Source Specifications Quadra 800/WS 80 Specifications Processor - 2 Processor CPU Motorola 68040 microprocessor 33 MHz Built-in paged memory management unit (PMMU), floating-point unit (FPU), and 8K memory cache Addressing 32-bit registers 32-bit address/data bus Specifications Memory - 3 Memory DRAM 8 MB (soldered DRAM) or 24 MB (8 MB soldered DRAM plus four 4 MB SIMMs) standard; expandable to 136 MB 72-pin SIMMs 60 ns access time ROM 1 MB soldered on logic board PRAM 256 bytes of parameter memory Specifications Memory - 4 VRAM 512K or 1 MB standard, expandable to 1 MB (80 ns or faster VRAM SIMMs) Maximum pixel depths for 512K / 1 MB VRAM: 12-inch color (512 x 384) - 16 / 16 bits per pixel 12-inch monochrome (640 x 480) - 8 / 8 bits per pixel 13-inch color (640 x 480) - 8 / 16 bits per pixel 15-inch portrait (640 x 870) - 4 / 8 bits per pixel 16-inch color (832 x 624) - 8 / 16 bits per pixel 19-inch color (1024 x 768) - 4 / 8 bits per pixel 21-inch monochrome (1152 x 870) - 4 / 8 bits per pixel 21-inch color (1152 x 870) - 4 / 8 bits per pixel VGA (640 x 480) - 8 / 16 bits per pixel SVGA (800 x 600) - 8 / 16 bits per pixel Clock/Calendar CMOS custom chip with long-life lithium battery Specifications Disk Storage - 5 Disk Storage Floppy Drive Internal, 1.4 MB Apple SuperDrive Hard Drive Internal, 3.5 in. -

October 1993 $2.95

October 1993 $2.95 The Journal of Washington Apple Pi, Ltd. Volmne 15, Number 10 Great printquality. aroatprice. LOOKING GOOD The HP DeskWriter: FOR LESS. $365. It looks like laser printing. But its :::::~:,;::.~=-~~-= priced like a dot matriX. ltcoold only --to-- 1\1 --..... """"'bOO"\I•"·'~'~· c.HQ_.._.._ ........,U•"'l· ,_,lall1<t...,,....,,._... ., """"' · • be a DeskWrllcr black and.white .,.,.,l)o __ flt'(loAjfMW'i..• ..... 'f;k.r~•o...-.(•Y•.. •• •th.uJ printer from Hewlett-Packard. · ~~ t;io~•'Ll(•.,.. ....., • .,.._ ,u,,. IW!>tnl"<>,......,,,,.'°-.. ._.. ,. .. ............ ,_ ....... tlit>:'r-&C.-..l'W'--7Wll>o• The HP DeskWriter for Macintosh --. r._·.~·'"° .., ,.,1,..,.,...,. .. .,.,.,,.......... ............... """ ,,:.i,....v.c., - ~-Y'-1"'"... ~·.,·-· IPs _,,,,t-W••·~lo(jllo -·~-.oq..,,....., . ...., uses I exclusive inltjct tech .......... "..... ,..,.. .. ,,,_,.~ .. r....._..,,_...,., c_~ Dl.djllll~__ .....,.._., ..... nology for laser-sharp text and .,,,,, .. __,_ "'°'~t-- -.. -~.-.. .. _, .._,_or_... graphics. The kind of print quality and spc.«I you expect from HP. At a price you have to see to believe. F<1rjlist $365• yo1,1 get high-quality, water-resistant print outpul, com patibility with most popular soft ware, and HPs three-year limited warranty, the longestIn the industry. ow the only thing you could possibly want is the name of your nearby authorized HP dealer. 1b get that too,just<:all t-800-5F>2-8500.t See what you can do. Desk.Jct Printers Make it happPn. ·. F//Q9 HEWLETT ~~PACKARD .. Washington Apple Pi General Meeting 4th Saturday• 9:00 a.m. • Sept. & Nov.: Community & Cultural Center Northern VA Community College, 8333 Little River Turnpike, Annandale, VA Oct.: Holiday Inn, 8120 Wisconsin Ave., Bethesda, MD Sept. -

Lnternetting -P

April 1994 $2.95 The Journal of Washington Apple Pi, Ltd. Volume 16, Number 4 lnternetting -p. 9 WordPerfect 3.0-p. 14 ~ Laser Printers -p. 18 Washington Apple Pi General Meeting 4th Saturday • 9:00 a.m. • Burning Tree Elementary School • 7900 Beech Tree Rd. Bethesda, Maryland April 23, 1994 Microsoft: FoxPro May21, 1994 Ares Software Burning• Tree E.S. DATES CHANGE! Bethesda, MD ~@W~ ~om the Beltway (I-495f take Exit 39 onto River lRoad (MD 190) inward toward DC and Bethesda approx. 1 mile. Tum left onto Beech Tree Road. ...A... Burning Tree Elementary 11111 School will be approx. 1/ 4 mile on the left . Northern Virginia ommunity College (NOVA) Table of Contents From the President Volume 16 April 1994 Number 4 TheTCS As It Evolves Club News Artist on Exhibit ........................ 26 by Lorin Evans by Blake Lange WAPHotline ........................ 39, 42 Macintosh Tutorials ................... 28 he operation of an electronic WAP Calendar ..................... 40, 41 Tutorial Registration Form ........ 29 bulletin board such as ours is a ln:dex to Advertisers .................... 2 Special Computer Offer ............. 30 T Classified Advertisements ......... 79 never-ending cycle of moderniza WAP Membership Form ............ 80 tion, expansion, and upgrade. The current TCS is a full replacement Apple II Articles for the Corvus network that was SIGs and Slices Teach a New Trick to a Venerable cajoled and coerced into the 20th Computer century. This first year of opera Stock SIG ..................................... 7 Dave & Joan Jernigan ........... 35 tion has given us a good idea as to by Morris Pelham Notes from the Apple II Vice what our members would like to see Mac Programmers' SIG .............. -

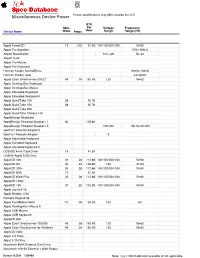

Miscellaneous Device Power Power Specifications May Differ Outside the U.S

Miscellaneous Device Power Power specifications may differ outside the U.S. BTU Max. Per Voltage Frequency Device Name Watts Amps Hour Range Range (Hz) Apple PowerCD 15 .125 51.30 100-125/200-240 50-60 Apple Pro Speakers 70Hz-20kHz Airport BaseStation 100–120 50–60 Airport Card Apple Pro Mouse Apple Pro Keyboard Harman Kardon SoundSticks 200Hz-15kHz Harman Kardon iSub 44-180Hz Apple Color OneScanner 600/27 45 .38 153.90 120 58-62 Apple Desktop Bus Keyboard Apple Desktop Bus Mouse Apple Extended Keyboard Apple Extended Keyboard II Apple QuickTake 100 28 95.76 Apple QuickTake 150 28 95.76 Apple QuickTake 200 Apple QuickTime Camera 100 AppleDesign Keyboard AppleDesign Powered Speakers I 40 136.80 AppleDesign Powered Speakers II 100-240 150 Hz-20 kHz GeoPort Telecom Adapter II GeoPort Telecom Adapter 5 Apple Adjustable Keyboard Apple Standard Keyboard Apple Standard Keyboard II DDS-DC 4mm Tape Drive 15 51.30 UniDisk-Apple 5.25 Drive AppleCD 300 33 .28 112.86 100-125/200-240 50-60 AppleCD SC 40 .33 136.80 120 47-64 AppleCD 300+ 33 .28 112.86 100-125/200-240 50-60 AppleCD 600i 15 51.30 AppleCD 600e Plus 33 .28 112.86 100-125/200-240 50-60 AppleCD 1200i AppleCD 150 30 .25 102.60 100-125/200-240 50-60 Apple Joystick //e Apple Modem 1200 Numeric Keypad IIe Apple Fax Modem 9600 10 .08 34.20 120 60 Apple Desktop Bus Mouse II Apple USB Mouse Apple USB Keyboard AppleCD 800 Apple Color OneScanner 1200/30 45 .38 153.90 120 58-62 Apple Color OneScanner for Windows 45 .38 153.90 120 58-62 AppleCD 300e Apple 3.5 Drive Apple 5.25 Drive Macintosh 800K External Disk Drive Macintosh HDI-20 External 1.4MB Floppy OCTOBER 15, 2016 12:58 AM Note: n/a = information not available or not applicable Miscellaneous Device Power Power specifications may differ outside the U.S. -

Macintosh LC II System Fact Sheet SYSTEM POWER PORTS ADB: 1 Introduced: March 1992 Max

Macintosh LC II System Fact Sheet SYSTEM POWER PORTS ADB: 1 Introduced: March 1992 Max. Watts: 50 Video: DB-15 Discontinued: March 1993 Amps: 0.42 Floppy: none Gestalt ID: 37 BTU Per Hour: 171 SCSI: DB-25 Form Factor: LC Voltage Range: 90-240 GeoPort Connectors: none Weight (lbs.): 8.8 Freq'y Range (Hz): 50-60 Ethernet: none Dimensions (inches): 2.9 H x 12.2 W x 15.3 D Battery Type: 3.6V lithium Microphone Port Type: Omni Soft Power Printer Speaker Codename: Foster Farms Monitor Power Outlet Headphone Oder Number: M1720LL/A Modem KB Article #: 9946 Airport Remote Control Support Discontinued 9/1/98 1 VIDEO Built-in Display: none Maximum Color Bit-depth At: 512 640 640 640 800 832 1024 1152 1280 VRAM Speed: VRAM Needed: Video Configuration: x384 x400 x480 x8702 x600 x624 x768 x870 x1024 100 ns 1x256K 256K VRAM 8 n/a 4 n/a n/a n/a n/a n/a n/a 1x512K 512K VRAM 16 n/a 8 n/a n/a n/a n/a n/a n/a 1 1-bit = Black & White; 2-bit = 4 colors; 4-bit = 16 colors; 8-bit = 256 colors; 16-bit = Thousands; 24-bit = Millions 2 The maximum color depth listed for 640x870 is 8-bit, reflecting the capabilities of the Apple 15" Portrait Display. LOGIC BOARD MEMORY Main Processor: 68030, 16 MHz Memory on Logic Board: 4 MB PMMU: integrated Minimum RAM: 4 MB FPU: none Maximum RAM: 10 MB Data Path: 16-bit, 16 MHz RAM Slots: 2 30-pin L1 Cache: 0.5K Minimum RAM Speed: 100 ns L2 Cache: none RAM Sizes: 1, 2, 4 MB Secondary Processor: none Install in Groups of: 2 Slots: 1 LC PDS When all SIMM slots are filled with 4MB SIMMs, the lower 2MB of RAM on the logic board cannot be addressed.